电阻选型: 1.时间常数RC电路所需电阻一般选误差尽量小的。 2.电阻额定功率应大于实际功率的2倍,以保证长期工作。电阻型号及其功率:0201型为1/20W,0402型为1/16W,0603型为1/10W,0805型为1/8W,1206型为1/4W。

IC芯片损坏的因素主要有: 1、静电击穿,故有些时候在触碰操作芯片时要求带上乳胶手套以防静电击穿。 2、电源超压。 3、过流输出。 4、过热烧毁。

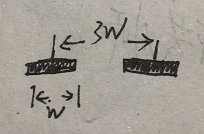

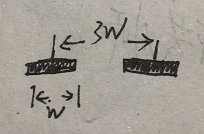

3W原则:线与线之间距离保持3倍线宽,以减少线间串扰。线中心距不少于3倍线宽则可保持70%的线间电场不互相干扰,如要达到98%的电场不互相干扰可用10W

20H原则:电源层比地层内缩20H(H为两层间的距离),内缩20H可将70%电场限制,内缩100H可将98%电场限制。实际上内缩1mm基本可以满足要求。(依据《信号完整性与PCB设计》作者:Douglas Brooks所说,20H实际上并没有什么明显的效果,至少他设计的电路中没有用到20H原则,板子没什么问题。)

特性阻抗:导线对其上面传输的射频能量的阻碍力的大小(通俗说法) 传输线本身特性阻抗可被设计。且电路设计中,要求终端电路负载与特性阻抗相匹配(大小相同)才能最大程度上吸收射频干扰。高速PCB中,时钟等关键的高速信号线,走线需要进行屏蔽处理,覆铜要良好接地,一般每1000mil打孔接地。(具体计算为小于λ/20的间距打孔,其中λ为具体信号波长)当布线长度为信号波长1/4的整数倍时,此布线将产生谐振,而谐振会辐射电磁波,产生干扰。高速信号必须有良好的回流路径,且保证时钟等高速信号回流路径最小,因为辐射大小和信号路径和回流路径所包围的面积成正比。简单来说就是回流路径在布线时尽量重合以减少包围的面积。

IC芯片损坏的因素主要有: 1、静电击穿,故有些时候在触碰操作芯片时要求带上乳胶手套以防静电击穿。 2、电源超压。 3、过流输出。 4、过热烧毁。

3W原则:线与线之间距离保持3倍线宽,以减少线间串扰。线中心距不少于3倍线宽则可保持70%的线间电场不互相干扰,如要达到98%的电场不互相干扰可用10W

20H原则:电源层比地层内缩20H(H为两层间的距离),内缩20H可将70%电场限制,内缩100H可将98%电场限制。实际上内缩1mm基本可以满足要求。(依据《信号完整性与PCB设计》作者:Douglas Brooks所说,20H实际上并没有什么明显的效果,至少他设计的电路中没有用到20H原则,板子没什么问题。)

特性阻抗:导线对其上面传输的射频能量的阻碍力的大小(通俗说法) 传输线本身特性阻抗可被设计。且电路设计中,要求终端电路负载与特性阻抗相匹配(大小相同)才能最大程度上吸收射频干扰。高速PCB中,时钟等关键的高速信号线,走线需要进行屏蔽处理,覆铜要良好接地,一般每1000mil打孔接地。(具体计算为小于λ/20的间距打孔,其中λ为具体信号波长)当布线长度为信号波长1/4的整数倍时,此布线将产生谐振,而谐振会辐射电磁波,产生干扰。高速信号必须有良好的回流路径,且保证时钟等高速信号回流路径最小,因为辐射大小和信号路径和回流路径所包围的面积成正比。简单来说就是回流路径在布线时尽量重合以减少包围的面积。