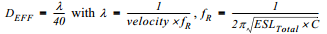

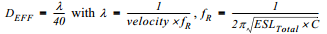

滤波半径还是基于著名的四分之一波长理论。(四分之一波长理论在高速先生的各种文章会反复多次出现,为了方便大家理解,我们会专题讨论各种四分之一波长的问题,这里就不再赘述,如果觉得理解这篇文章有问题,可以单独和高速先生进行讨论)电容去耦半径理论认为,当电容的位置距需要滤波的器件(管脚)的距离刚好是四分之一波长的时候,电容的补偿电流和信号噪声电流相位刚好相差180度,滤波失效。所以为了保证电容的滤波作用,要求电容的位置距需要滤波的器件(管脚)的距离小于1/10的四分之一波长,当然,更严格的要求希望小于1/20的四分之一波长。

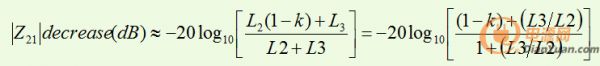

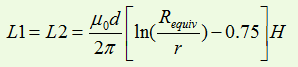

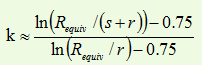

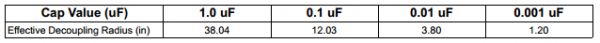

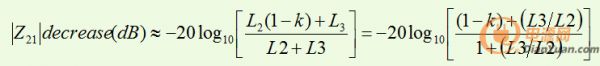

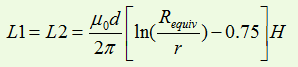

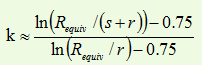

大家看到这,估计有点烦躁了,有的人说,这个我早就知道了。也有人说,不是叫“看得懂的高速设计”吗,你说的这些我看不懂。那我们就来看看常见的滤波电容的滤波半径。(这里我们为了计算的简化,假设电容的ESL为0.4NH,电容的安装电感为1.5NH。具体的电容安装电感问题,在上一个专题的第四篇文章里面讨论过了,大家可以参考)

大家看到这,估计有点烦躁了,有的人说,这个我早就知道了。也有人说,不是叫“看得懂的高速设计”吗,你说的这些我看不懂。那我们就来看看常见的滤波电容的滤波半径。(这里我们为了计算的简化,假设电容的ESL为0.4NH,电容的安装电感为1.5NH。具体的电容安装电感问题,在上一个专题的第四篇文章里面讨论过了,大家可以参考)

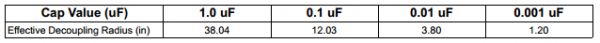

看到这里,估计很多PCB设计师会大吃一惊?我们常用的0.1 uf电容,在考虑四十分之一波长的时候,电容的有效去耦半径居然有12英寸。就算严格点考虑两百分之一波长,也有将近2英寸的去耦半径。我们在滤波电容布局的时候,这个去耦半径还是问题吗?

看到这里,估计很多PCB设计师会大吃一惊?我们常用的0.1 uf电容,在考虑四十分之一波长的时候,电容的有效去耦半径居然有12英寸。就算严格点考虑两百分之一波长,也有将近2英寸的去耦半径。我们在滤波电容布局的时候,这个去耦半径还是问题吗?

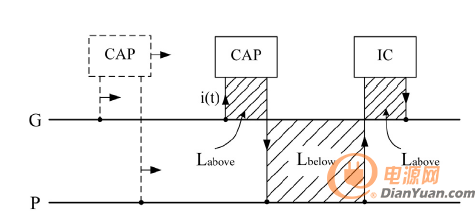

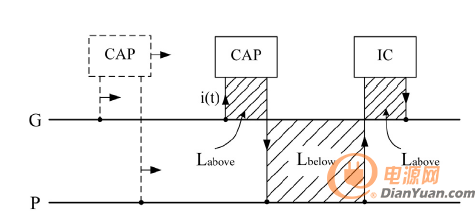

本节的结论还是继续有效的,我们常用的0.1uf电容,滤波半径远远比我们想象的要大。 本节的问题是: 既然简单的用四分之一波长理论推算的电容去耦半径,对电容布局设计起不到指导作用,那么电容放置的离芯片电源管脚比较远,还会有哪些影响呢? 我们知道平常“耳熟能详”的电容去耦半径理论,对PCB设计其实没有什么指导意义。0.1uf的电容去耦半径足够大,设计中参考这个值没有用处,工程师还是会“尽量”把0.1uf电容靠近芯片的电源管教放置。PCB设计师需要更有效的理论来指导电容的布局设计。 既然简单的用四分之一波长理论推算的电容去耦半径不起作用,那么电容放置得离芯片电源管脚比较远,还会有哪些影响呢?很多人都答对了,影响安装电感。 在上一个专题的第四篇文章里面,已经讨论过电容安装电感的估算。这一次,我们来更详细的看看安装电感。从图3能看到,安装电感可以简单分为L above和 L below。

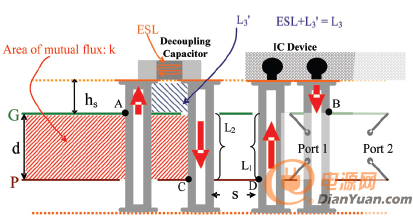

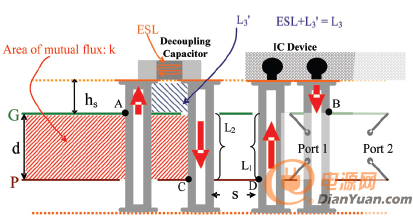

图3 在这里引入两个概念:Labove 、Lbelow(电容和IC下面的电流回路大小不一定一样,但在这里分析的时候,假定大小等同) 总电感:LTotal= 2Labove+Lbelow Labove包括电容的ESL和Fan out带来的电感,我们会另外专题讨论电容的Fan out问题。至于L below就更多收到电容位置的影响。简单来说,电容离芯片电源管脚越远,L below围成的面积就越大,相应的安装电感就越大。 更具体点,Lbelow主要是两个过孔的自感和互感,当电容的位置离IC器件更近时,如图4所示,Lbelow的互感增大,因互感的作用与自感的作用相反,导致其整体电感减小,充放电速率更快

图4 可以列出一堆公式来推导这个互感乃至L below,但这个不是高速先生的风格。

图3 其实从图3可以简单看出,G和P之间的距离对L below影响很大,G和P之间的距离越近,L below对应的阴影区域面积就越小。而L below越小,也就意味这电容可以放得越远,换句话说,电容的有效滤波范围更大。电容也就更加倾向于呈现“全局”特性。

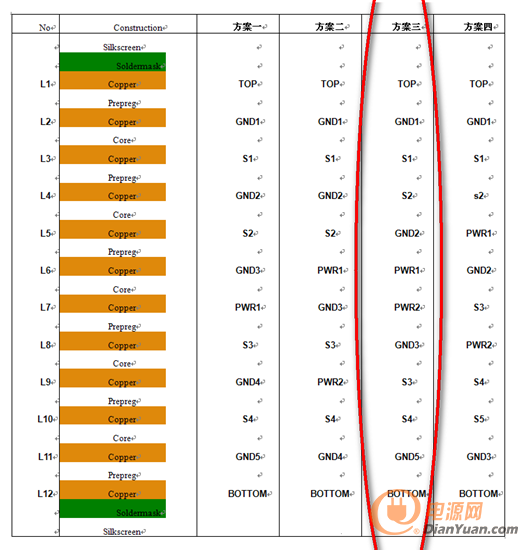

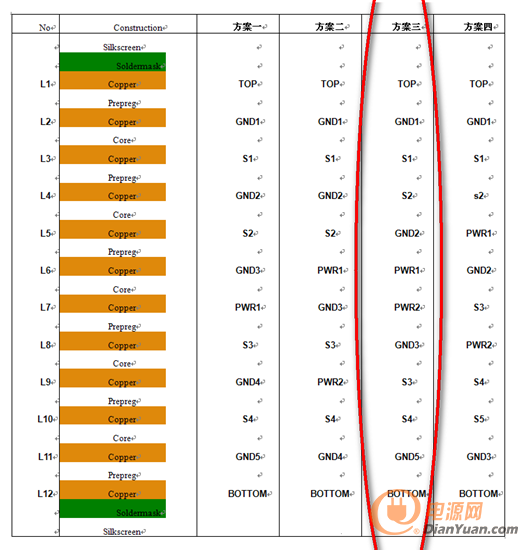

“滥用”磁珠,会带来哪些坏处?什么情况下我们需要使用磁珠对电源进行隔离?什么情况下,“滥用”磁珠会带来负面影响? 多层板设计的时候,电容倾向于呈现“全局特性”,“电源加磁珠”的设计方法,会影响电容在全局范围内起作用。同时电源种类太多,还会带来其他设计问题。 所以,我们可以得出简单的结论: 典型的8层以上单板,或者6层板采用3个电源地平面,电源地相对紧耦合的设计,这时候板上的滤波电容呈现“全局特性”,也就是说电容的位置不是很“重要”,电容在全局起作用。双面板四层板,以及6层板电源地距离比较远,相对松耦合的时候,板上的滤波电容倾向于“局部特性”,电容的位置比较重要,最好能靠近芯片管脚放置。 当电源供电网络不使用电源地平面来设计的时候,电容更倾向于“局部特性”。如PLL电源的电容,如DDR3设计中Vref电源的电容,都希望严格把相应的电容靠近芯片的管脚,甚至最好能做到设计时指定电源必须从滤波电容进入芯片管脚。 同样的,对于常规数字电源,如3.3V,2.5V等IO电源,如果我们对每一个芯片都使用磁珠隔离之后单独供电,那么电容就失去了“全局”作用。最直接的一个负面作用就是导致设计需要增加更多的滤波电容。或者某个芯片的电容数量与种类不够,导致电源轨道噪声变大。 就算是电容的数量不是问题,电源噪声可控,“滥用”磁珠还会造成其他设计问题。图9中的方案三是现在非常流行的12层板层叠设计。大家选择这样的层叠最主要的原因就是电源的分割太破碎,这样的电源层如果作为参考平面的话,会比较难避免“跨分割”问题(单面跨电源分割问题,我们会另外有专题讨论)。方案三的层叠避免了电源分割多的问题,却带来更加恶劣的层间串扰等其他问题。

电源种类多是设计的现状,“滥用”磁珠会“雪上加霜”的让电源种类更多。加大电源地平面设计的难度。而增加的磁珠,其实并没有给电源噪声带来好处。

图9 总结:常规的数字电源,在采用多层板设计,电源地平面紧耦合的情况下,不建议“滥用”磁珠,保持电容的“全局”特性起作用。 需要使用磁珠的场合大致分为两种 1、“特别”保护自己,如PLL电源等 2、“关爱”他人,自身的干扰性比较强,避免EMI问题,如强驱动的时钟芯片等 每次一个话题结束的时候,总觉得没什么问题可以问,因为觉得都讲清楚了。不过每次编辑都会强调“你的问题”呢?那就找一个问题,作为下一个话题的铺垫吧: 我们怎么减小上一篇文章中提到的L above?

大家看到这,估计有点烦躁了,有的人说,这个我早就知道了。也有人说,不是叫“看得懂的高速设计”吗,你说的这些我看不懂。那我们就来看看常见的滤波电容的滤波半径。(这里我们为了计算的简化,假设电容的ESL为0.4NH,电容的安装电感为1.5NH。具体的电容安装电感问题,在上一个专题的第四篇文章里面讨论过了,大家可以参考)

大家看到这,估计有点烦躁了,有的人说,这个我早就知道了。也有人说,不是叫“看得懂的高速设计”吗,你说的这些我看不懂。那我们就来看看常见的滤波电容的滤波半径。(这里我们为了计算的简化,假设电容的ESL为0.4NH,电容的安装电感为1.5NH。具体的电容安装电感问题,在上一个专题的第四篇文章里面讨论过了,大家可以参考)

看到这里,估计很多PCB设计师会大吃一惊?我们常用的0.1 uf电容,在考虑四十分之一波长的时候,电容的有效去耦半径居然有12英寸。就算严格点考虑两百分之一波长,也有将近2英寸的去耦半径。我们在滤波电容布局的时候,这个去耦半径还是问题吗?

看到这里,估计很多PCB设计师会大吃一惊?我们常用的0.1 uf电容,在考虑四十分之一波长的时候,电容的有效去耦半径居然有12英寸。就算严格点考虑两百分之一波长,也有将近2英寸的去耦半径。我们在滤波电容布局的时候,这个去耦半径还是问题吗?

本节的结论还是继续有效的,我们常用的0.1uf电容,滤波半径远远比我们想象的要大。 本节的问题是: 既然简单的用四分之一波长理论推算的电容去耦半径,对电容布局设计起不到指导作用,那么电容放置的离芯片电源管脚比较远,还会有哪些影响呢? 我们知道平常“耳熟能详”的电容去耦半径理论,对PCB设计其实没有什么指导意义。0.1uf的电容去耦半径足够大,设计中参考这个值没有用处,工程师还是会“尽量”把0.1uf电容靠近芯片的电源管教放置。PCB设计师需要更有效的理论来指导电容的布局设计。 既然简单的用四分之一波长理论推算的电容去耦半径不起作用,那么电容放置得离芯片电源管脚比较远,还会有哪些影响呢?很多人都答对了,影响安装电感。 在上一个专题的第四篇文章里面,已经讨论过电容安装电感的估算。这一次,我们来更详细的看看安装电感。从图3能看到,安装电感可以简单分为L above和 L below。

图3 在这里引入两个概念:Labove 、Lbelow(电容和IC下面的电流回路大小不一定一样,但在这里分析的时候,假定大小等同) 总电感:LTotal= 2Labove+Lbelow Labove包括电容的ESL和Fan out带来的电感,我们会另外专题讨论电容的Fan out问题。至于L below就更多收到电容位置的影响。简单来说,电容离芯片电源管脚越远,L below围成的面积就越大,相应的安装电感就越大。 更具体点,Lbelow主要是两个过孔的自感和互感,当电容的位置离IC器件更近时,如图4所示,Lbelow的互感增大,因互感的作用与自感的作用相反,导致其整体电感减小,充放电速率更快

图4 可以列出一堆公式来推导这个互感乃至L below,但这个不是高速先生的风格。

图3 其实从图3可以简单看出,G和P之间的距离对L below影响很大,G和P之间的距离越近,L below对应的阴影区域面积就越小。而L below越小,也就意味这电容可以放得越远,换句话说,电容的有效滤波范围更大。电容也就更加倾向于呈现“全局”特性。

“滥用”磁珠,会带来哪些坏处?什么情况下我们需要使用磁珠对电源进行隔离?什么情况下,“滥用”磁珠会带来负面影响? 多层板设计的时候,电容倾向于呈现“全局特性”,“电源加磁珠”的设计方法,会影响电容在全局范围内起作用。同时电源种类太多,还会带来其他设计问题。 所以,我们可以得出简单的结论: 典型的8层以上单板,或者6层板采用3个电源地平面,电源地相对紧耦合的设计,这时候板上的滤波电容呈现“全局特性”,也就是说电容的位置不是很“重要”,电容在全局起作用。双面板四层板,以及6层板电源地距离比较远,相对松耦合的时候,板上的滤波电容倾向于“局部特性”,电容的位置比较重要,最好能靠近芯片管脚放置。 当电源供电网络不使用电源地平面来设计的时候,电容更倾向于“局部特性”。如PLL电源的电容,如DDR3设计中Vref电源的电容,都希望严格把相应的电容靠近芯片的管脚,甚至最好能做到设计时指定电源必须从滤波电容进入芯片管脚。 同样的,对于常规数字电源,如3.3V,2.5V等IO电源,如果我们对每一个芯片都使用磁珠隔离之后单独供电,那么电容就失去了“全局”作用。最直接的一个负面作用就是导致设计需要增加更多的滤波电容。或者某个芯片的电容数量与种类不够,导致电源轨道噪声变大。 就算是电容的数量不是问题,电源噪声可控,“滥用”磁珠还会造成其他设计问题。图9中的方案三是现在非常流行的12层板层叠设计。大家选择这样的层叠最主要的原因就是电源的分割太破碎,这样的电源层如果作为参考平面的话,会比较难避免“跨分割”问题(单面跨电源分割问题,我们会另外有专题讨论)。方案三的层叠避免了电源分割多的问题,却带来更加恶劣的层间串扰等其他问题。

电源种类多是设计的现状,“滥用”磁珠会“雪上加霜”的让电源种类更多。加大电源地平面设计的难度。而增加的磁珠,其实并没有给电源噪声带来好处。

图9 总结:常规的数字电源,在采用多层板设计,电源地平面紧耦合的情况下,不建议“滥用”磁珠,保持电容的“全局”特性起作用。 需要使用磁珠的场合大致分为两种 1、“特别”保护自己,如PLL电源等 2、“关爱”他人,自身的干扰性比较强,避免EMI问题,如强驱动的时钟芯片等 每次一个话题结束的时候,总觉得没什么问题可以问,因为觉得都讲清楚了。不过每次编辑都会强调“你的问题”呢?那就找一个问题,作为下一个话题的铺垫吧: 我们怎么减小上一篇文章中提到的L above?