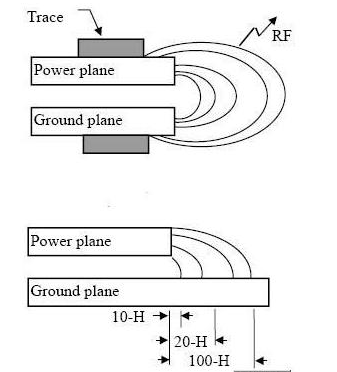

3W原则:参看:PCB设计之3W原则扩展:Complete PCB Design Using OrCad Capture and Layout为了减少走线之间的窜扰,提高信号质量,应保证线间距足够大;常规中,当走线中心间距不少于3倍线宽时,则可保持70%的电场不互相干扰,称为3W规则。如要走线中心间距达到10W,则可以达到98%的电场不相互干扰(其中W表示走线的宽度),针对EMI(电磁干扰)。3W原则是指多个高速信号线长距离走线的时候,其间距应该遵循3W原则,例如时钟线,差分线,视频、音频信号线,复位信号线及其他系统关键电路需要遵循3W原则,而并不是板上所有的布线都要强制符合3W原则。

具体到Hi3516A的硬件设计:VI 接口:Parallel CMOS接口

VO 接口:Hi3516A共有1个BT.1120

DDR3 PCB 布线设计

网口信号设计

相邻信号走线间距需要保持“ 3W”原则。

20H原则:

参看:Protel硬件开发PCB设计的3W和20H原则及五五规则扩展:Effects of 20-H Rule

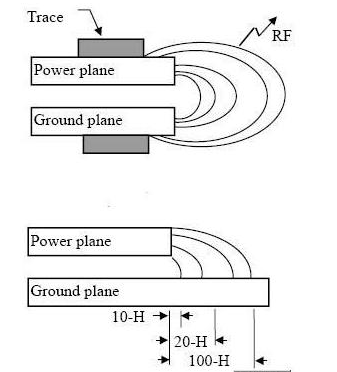

由于电源层与地层之间的电场是变化的,在板的边缘会向外辐射电磁干扰。在PCB设计中,可以将电源层内缩,使得电场只在接地层的范围内传导。若电源层相对地层内缩20H,则可以将70%的电场限制在接地边沿内;若内缩100H则可以将98%的电场限制在内(其中H表示电源和地之间的介质厚度),针对EMC(电磁兼容)

20H规则的采用是指要确保电源平面的边缘要比0V平面边缘至少缩入相当于两个平面间层距的20倍。这个规则经常被要求用来作为降低来自0V/电源平面结构的侧边射击发射技术(抑制边缘辐射效应)。

但是,20H规则仅在某些特定的条件下才会提供明显的效果。这些特定条件包括有:

1. 在电源总线中电流波动的上升/下降时间要小于1ns。

2. 电源平面要处在PCB的内部层面上,并且与它相邻的上下两个层面都为0V平面。这两个0V平面向外延伸的距离至少要相当于它们各自与电源平面间层距的20倍。

3. 在所关心的任何频率上,电源总线结构不会产生谐振。

4. PCB的总导数至少为8层或更多。

具体到Hi3516A的硬件设计:VI 接口:Parallel CMOS接口

VO 接口:Hi3516A共有1个BT.1120

DDR3 PCB 布线设计

网口信号设计

相邻信号走线间距需要保持“ 3W”原则。

20H原则:

参看:Protel硬件开发PCB设计的3W和20H原则及五五规则扩展:Effects of 20-H Rule

由于电源层与地层之间的电场是变化的,在板的边缘会向外辐射电磁干扰。在PCB设计中,可以将电源层内缩,使得电场只在接地层的范围内传导。若电源层相对地层内缩20H,则可以将70%的电场限制在接地边沿内;若内缩100H则可以将98%的电场限制在内(其中H表示电源和地之间的介质厚度),针对EMC(电磁兼容)

20H规则的采用是指要确保电源平面的边缘要比0V平面边缘至少缩入相当于两个平面间层距的20倍。这个规则经常被要求用来作为降低来自0V/电源平面结构的侧边射击发射技术(抑制边缘辐射效应)。

但是,20H规则仅在某些特定的条件下才会提供明显的效果。这些特定条件包括有:

1. 在电源总线中电流波动的上升/下降时间要小于1ns。

2. 电源平面要处在PCB的内部层面上,并且与它相邻的上下两个层面都为0V平面。这两个0V平面向外延伸的距离至少要相当于它们各自与电源平面间层距的20倍。

3. 在所关心的任何频率上,电源总线结构不会产生谐振。

4. PCB的总导数至少为8层或更多。