PCB范例

1、差分走线长度匹配

1、差分走线长度匹配

2、走线禁止跨越不完整的地平面

2、走线禁止跨越不完整的地平面

3、如果走线跨越分割地平面不可避免,请用1uF以下电容拼接两个地平面

4、高速差分信号线距和线宽参考设计如下:

5、不要放测试点在任何高速差分信号线上。

5、不要放测试点在任何高速差分信号线上。

6、不要在晶体、振荡器,时钟信号发生器,开关电源,安装孔,磁性器件或者周期性信号芯片的附近或者下方走高速信号线。

7、尽量使高速信号线走在TOP和BOTTOM层,并有完整的参考地层。不建议走内层。

8、高速信号到参考地的边缘保持大于90mil的距离。

9、走出BGA后,走线请保持恒定的宽度,以保持阻抗恒定。

10、差分对间的间距尽可能的扩大。

11、插座和连接器接线的处理

12、信号换层处理

12、信号换层处理

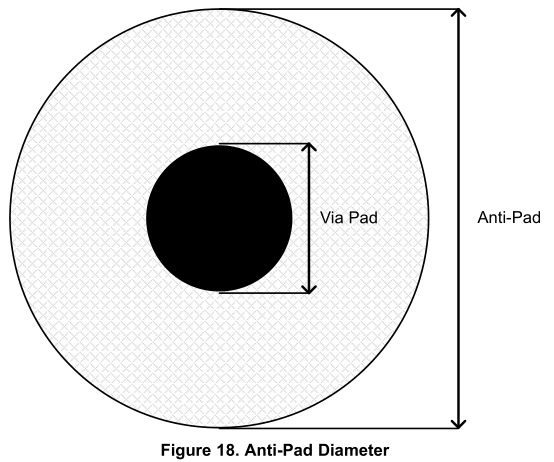

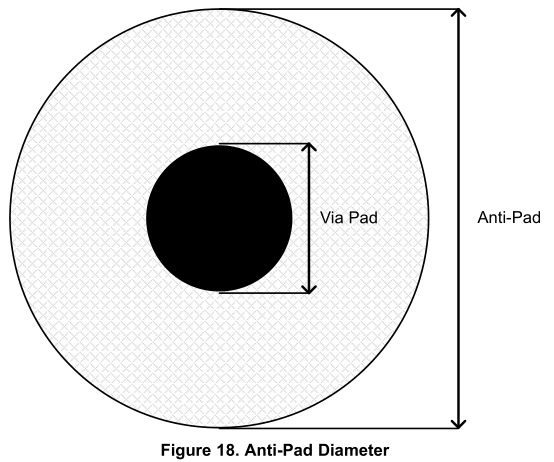

13、增加通孔的反焊盘直径,可以减少电容效应和插入损耗。Anti-pad推荐30mil就可以了。要确保每层都有Anti-pad。

14、如果差分走线不可避免使用过孔,请确保过孔的数量相等,并且过孔的间距相等。推荐过孔尽量靠近放在SOC芯片端。

14、如果差分走线不可避免使用过孔,请确保过孔的数量相等,并且过孔的间距相等。推荐过孔尽量靠近放在SOC芯片端。

15、高速差分线串联阻容处理(比如交流耦合的情况),不要使用0603以上封装的器件,建议使用0402的封装。

16、高速差分线串联阻容下面的地请100%挖空,至少挖空两个PCB层,如下图:

17、信号弯曲走线可参考下图规则:

18、ESD器件尽量靠近连接器放置,在ESD / EMI组件信号焊盘下加入60%的空隙,以减少损耗。

交流耦合器件要放在受保护侧,并靠近共模滤波器。如果有过孔,请把过孔靠近共模滤波器。

交流耦合电容,共模滤波器,ESD器件要尽可能靠近连接器放置。

以上资料参考《TI高速信号设计》。

以上资料参考《TI高速信号设计》。

1、差分走线长度匹配

1、差分走线长度匹配 2、走线禁止跨越不完整的地平面

2、走线禁止跨越不完整的地平面

3、如果走线跨越分割地平面不可避免,请用1uF以下电容拼接两个地平面

4、高速差分信号线距和线宽参考设计如下:

5、不要放测试点在任何高速差分信号线上。

5、不要放测试点在任何高速差分信号线上。6、不要在晶体、振荡器,时钟信号发生器,开关电源,安装孔,磁性器件或者周期性信号芯片的附近或者下方走高速信号线。

7、尽量使高速信号线走在TOP和BOTTOM层,并有完整的参考地层。不建议走内层。

8、高速信号到参考地的边缘保持大于90mil的距离。

9、走出BGA后,走线请保持恒定的宽度,以保持阻抗恒定。

10、差分对间的间距尽可能的扩大。

11、插座和连接器接线的处理

12、信号换层处理

12、信号换层处理

13、增加通孔的反焊盘直径,可以减少电容效应和插入损耗。Anti-pad推荐30mil就可以了。要确保每层都有Anti-pad。

14、如果差分走线不可避免使用过孔,请确保过孔的数量相等,并且过孔的间距相等。推荐过孔尽量靠近放在SOC芯片端。

14、如果差分走线不可避免使用过孔,请确保过孔的数量相等,并且过孔的间距相等。推荐过孔尽量靠近放在SOC芯片端。15、高速差分线串联阻容处理(比如交流耦合的情况),不要使用0603以上封装的器件,建议使用0402的封装。

16、高速差分线串联阻容下面的地请100%挖空,至少挖空两个PCB层,如下图:

17、信号弯曲走线可参考下图规则:

18、ESD器件尽量靠近连接器放置,在ESD / EMI组件信号焊盘下加入60%的空隙,以减少损耗。

交流耦合器件要放在受保护侧,并靠近共模滤波器。如果有过孔,请把过孔靠近共模滤波器。

交流耦合电容,共模滤波器,ESD器件要尽可能靠近连接器放置。

以上资料参考《TI高速信号设计》。

以上资料参考《TI高速信号设计》。