概述

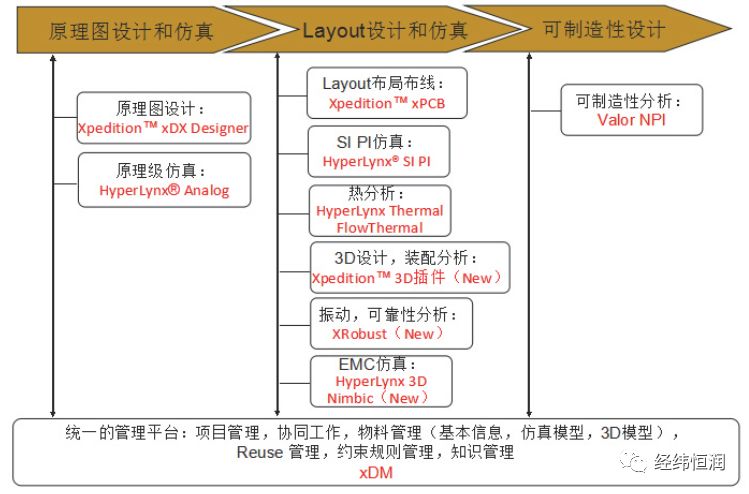

作为世界 PCB 领域首选的设计仿真平台,Mentor 公司为设计者提供了一个从概念设计到生产制造的的硬件全流程解决方案。它涉及到 PCB 设计从系统定义、原理仿真、约束定义、Layout 布线,到后续生产制造的 DFM 分析、以及物流及知识管理等,都在设计平台中得以完美实现,如下图所示:

产品介绍

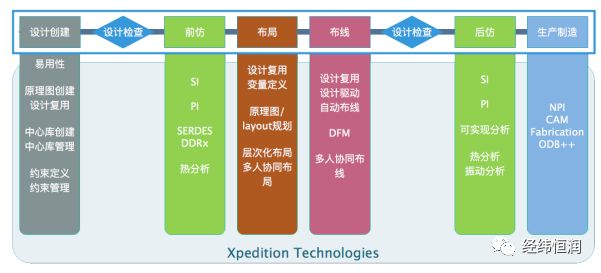

Mentor 公司 Xpedition 企业级电子设计平台解决方案集成以下模块或工具:

• 元器件中心库管理工具:xDM Library

• 原理图设计工具:xDX Designer

• PCB Layout 工具:xPCB Layout

• FPGA/IO 协同工具:xDX I/O Designer

• 仿真分析工具:HyperLynx

• DFM 分析工具:Valor NPI

• PCB 综合设计工具:PADS

• xDM 数据管理

♦ 将PCB设计所涉及的企业标准、设计规范、物料库、元器件库、器件手册、各阶段设计文件、生产数据等都是保存在服务器的数据库中

♦ xDM Library 是专门的元器件库管理工具,除了符号、封装等,设计复用模块、仿真模型都可以在工具进行管理

• 原理图设计 xDX Designer

♦ xDX Designer 是专门的原理图绘制工具,它为设计团队提供了便利易用的设计环境,支持多人协同设计,支持设计复用,同时它提供了与企业其它管理系统接口,实现了元器件、设计数据和生产文件高度一致

• 布局布线 xPCB Layout

♦ xPCB Layout 运用多种技术,规则约束、元件布局和网络规划及优化,同时通过多人协同设计,帮助设计人员完成任何复杂 PCB 设计,加速 PCB 设计进程

♦ 针对复杂、高密度的电子设计,工具加入了高级自动设计规划、布局和布线功能,包括动态覆铜、泪滴焊盘生成、高性能差分对布线,HDI/ 微孔技术、盲埋孔技术等,减少产品开发周期

• FPGA I/O 协同工具:xDX I/O Designer

♦ I/O Designer“跨接”在 FPGA 设计流程与 PCB 设计流程之间,使得工程师们可以通过多种方式来实现 FPGA 的管脚分配,并能保证全流程中设计数据的严格同步

• 仿真分析工具 Hyperlynx

♦ HyperLynx 仿真工具是目前业界内功能最全、技术最先进的解决方案。主要有模拟电路仿真分析、信号完整性分析(SI)、电源完整性分析(PI)、板级热分析、3D 电磁场建模分析等

• DFM 分析工具 Valor

♦ Valor NPI 提供了设计阶段的 DFM 验证功能,它内嵌 800 余条检查规则,支持所有 PCB 设计工具的数据格式,可将设计错误同步到 PCB 设计环境中以便错误定位

• 其他特性

♦ 统一、标准的元件库管理机制,在多人协同的团队设计中,保证了数据的唯一性,降低了分歧产生的可能,大大缩短了设计时间

♦ 集成的参数化 3D 模型、约束管理和 DRC 检查,在设计阶段能够有效的检测设计干涉,研制可装配性等内容

• PCB 硬件设计套件—PADS

PADS 是 Mentor 公司针对小规模硬件设计团队,它使用Xpedition 的软件架构,整合 Hyperlynx 相关模块,形成完善的PCB 电子硬件设计仿真平台。

♦ Library 中心库和元件信息管理:PADS 提供中心库管理模块,包含符号、封装和 Part 映射关系。符合 IPC-7351B 标准,包含原理图符号、PCB 封装

♦ 设计定义和归档管理:PADS 支持数字、模拟 / 混合信号和RF 电路的表格驱动设计方式及变体设计,支持归档管理及变体管理。提供 Databook 功能,支持元件信息的快速搜索和图形示例

♦ DRC 设计规则检查:提供全面的 DRC 设计规则检查,可验证EMI/EMC 问题

♦ Constraint 约束管理:定义设计规则,提供满足约束下的设计方法,保证设计质量

♦ 2D/3D 综合布线和 Sketch Router:使用Sketch Router 机制,实现自动布线,成功率高(> 90%),特别适合复杂 PCB布线设计。同时支持 2D 原理图和 3D 装配交互设计方式,设计数据可实时同步

♦ 模拟 / 混合电路仿真:PADS 提供板级模拟 / 混合电路仿真功能,支持 SPICE 模型,提供静态工作点计算、直流扫描分析、时域 / 频域分析、傅立叶分析、蒙特卡罗 / 最差状况分析等,可对电路各点工作波形进行模拟测试

♦ 板级热分析:PADS 提供板级热分析功能,可对器件布局、局部布线、全局布线进行散热问题分析

♦ 信号完整性分析:利用的是 HyperLynx 仿真技术,分析功能集成到设计流程中,自动提取原理图网络的拓扑结构,对PCB 网络拓扑结构、传输线参数和叠层结构进行模拟和优化,支持传输线特征阻抗与传输延迟的计算,通过仿真及时发现网络中可能出现的反射、串扰、延迟等隐患,并提供修改建议,完善设计规则

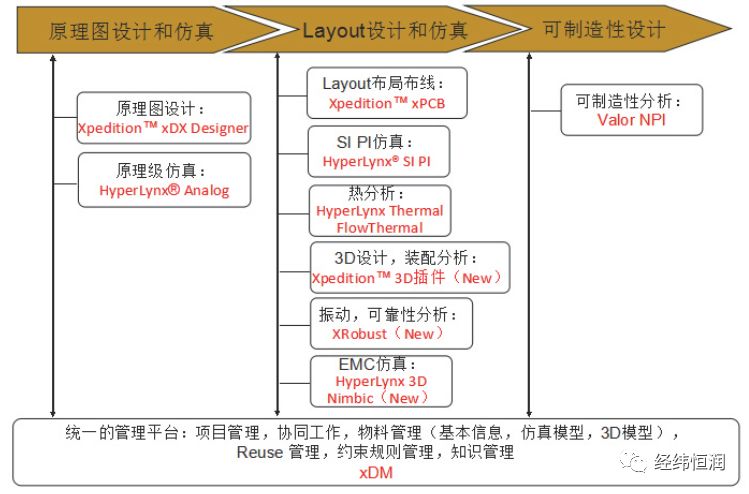

作为世界 PCB 领域首选的设计仿真平台,Mentor 公司为设计者提供了一个从概念设计到生产制造的的硬件全流程解决方案。它涉及到 PCB 设计从系统定义、原理仿真、约束定义、Layout 布线,到后续生产制造的 DFM 分析、以及物流及知识管理等,都在设计平台中得以完美实现,如下图所示:

产品介绍

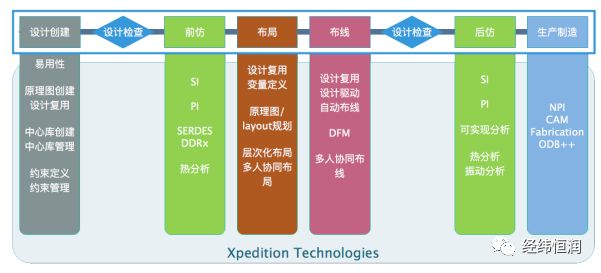

Mentor 公司 Xpedition 企业级电子设计平台解决方案集成以下模块或工具:

• 元器件中心库管理工具:xDM Library

• 原理图设计工具:xDX Designer

• PCB Layout 工具:xPCB Layout

• FPGA/IO 协同工具:xDX I/O Designer

• 仿真分析工具:HyperLynx

• DFM 分析工具:Valor NPI

• PCB 综合设计工具:PADS

• xDM 数据管理

♦ 将PCB设计所涉及的企业标准、设计规范、物料库、元器件库、器件手册、各阶段设计文件、生产数据等都是保存在服务器的数据库中

♦ xDM Library 是专门的元器件库管理工具,除了符号、封装等,设计复用模块、仿真模型都可以在工具进行管理

• 原理图设计 xDX Designer

♦ xDX Designer 是专门的原理图绘制工具,它为设计团队提供了便利易用的设计环境,支持多人协同设计,支持设计复用,同时它提供了与企业其它管理系统接口,实现了元器件、设计数据和生产文件高度一致

• 布局布线 xPCB Layout

♦ xPCB Layout 运用多种技术,规则约束、元件布局和网络规划及优化,同时通过多人协同设计,帮助设计人员完成任何复杂 PCB 设计,加速 PCB 设计进程

♦ 针对复杂、高密度的电子设计,工具加入了高级自动设计规划、布局和布线功能,包括动态覆铜、泪滴焊盘生成、高性能差分对布线,HDI/ 微孔技术、盲埋孔技术等,减少产品开发周期

• FPGA I/O 协同工具:xDX I/O Designer

♦ I/O Designer“跨接”在 FPGA 设计流程与 PCB 设计流程之间,使得工程师们可以通过多种方式来实现 FPGA 的管脚分配,并能保证全流程中设计数据的严格同步

• 仿真分析工具 Hyperlynx

♦ HyperLynx 仿真工具是目前业界内功能最全、技术最先进的解决方案。主要有模拟电路仿真分析、信号完整性分析(SI)、电源完整性分析(PI)、板级热分析、3D 电磁场建模分析等

• DFM 分析工具 Valor

♦ Valor NPI 提供了设计阶段的 DFM 验证功能,它内嵌 800 余条检查规则,支持所有 PCB 设计工具的数据格式,可将设计错误同步到 PCB 设计环境中以便错误定位

• 其他特性

♦ 统一、标准的元件库管理机制,在多人协同的团队设计中,保证了数据的唯一性,降低了分歧产生的可能,大大缩短了设计时间

♦ 集成的参数化 3D 模型、约束管理和 DRC 检查,在设计阶段能够有效的检测设计干涉,研制可装配性等内容

• PCB 硬件设计套件—PADS

PADS 是 Mentor 公司针对小规模硬件设计团队,它使用Xpedition 的软件架构,整合 Hyperlynx 相关模块,形成完善的PCB 电子硬件设计仿真平台。

♦ Library 中心库和元件信息管理:PADS 提供中心库管理模块,包含符号、封装和 Part 映射关系。符合 IPC-7351B 标准,包含原理图符号、PCB 封装

♦ 设计定义和归档管理:PADS 支持数字、模拟 / 混合信号和RF 电路的表格驱动设计方式及变体设计,支持归档管理及变体管理。提供 Databook 功能,支持元件信息的快速搜索和图形示例

♦ DRC 设计规则检查:提供全面的 DRC 设计规则检查,可验证EMI/EMC 问题

♦ Constraint 约束管理:定义设计规则,提供满足约束下的设计方法,保证设计质量

♦ 2D/3D 综合布线和 Sketch Router:使用Sketch Router 机制,实现自动布线,成功率高(> 90%),特别适合复杂 PCB布线设计。同时支持 2D 原理图和 3D 装配交互设计方式,设计数据可实时同步

♦ 模拟 / 混合电路仿真:PADS 提供板级模拟 / 混合电路仿真功能,支持 SPICE 模型,提供静态工作点计算、直流扫描分析、时域 / 频域分析、傅立叶分析、蒙特卡罗 / 最差状况分析等,可对电路各点工作波形进行模拟测试

♦ 板级热分析:PADS 提供板级热分析功能,可对器件布局、局部布线、全局布线进行散热问题分析

♦ 信号完整性分析:利用的是 HyperLynx 仿真技术,分析功能集成到设计流程中,自动提取原理图网络的拓扑结构,对PCB 网络拓扑结构、传输线参数和叠层结构进行模拟和优化,支持传输线特征阻抗与传输延迟的计算,通过仿真及时发现网络中可能出现的反射、串扰、延迟等隐患,并提供修改建议,完善设计规则