1.点对点拓扑 point-to-point scheduling

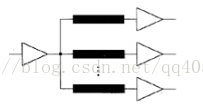

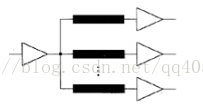

该拓扑结构简单,整个网络的阻抗特性容易控制,时序关系也容易控制,常见于高速双向传输信号线;常在源端加串行匹配电阻来防止源端的二次反射。

2.菊花链结构 daisy-chain scheduling

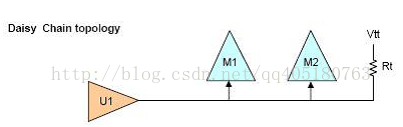

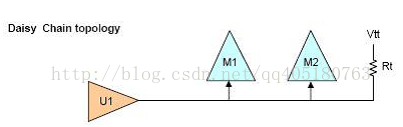

如下图所示,菊花链结构也比较简单,阻抗也比较容易控制。菊花链的特征就是每个接收端最多只和2个另外的接收端/发送端项链,连接每个接收端的stub线需要较短。该结构的阻抗匹配常在终端做,用戴维南端接比较合适。

3. fly-by scheduling 该结构是特殊的菊花链结构, stub线为0的菊花链。不同于DDR2的T型分支拓扑结构,DDR3采用了fly-by拓扑结构,以更高的速度提供更好的信号完整性。fly-by信号 是命令、地址,控制和时钟信号。如图1所示,源于存储器控制器的这些信号以串行的方式连接到每个DRAM器件。通过减少分支的数量和分支的长度改进了信号 完整性。然而,这引起了另一个问题,因为每一个存储器元件的延迟是不同的,取决于它处于时序的位置。通过按照DDR3规范的定义,采用读调整和写调整技术 来补偿这种延迟的差异。fly-by拓扑结构在电源开启时校正存储器系统。这就要求在DDR3控制器中有额外的信息,允许校准工作在启动时自动完成。 在写调整期间,存储器控制器需要补偿额外的跨越时间偏移(对每个存储器器件,信号延迟是不同的),这是由于fly-by拓扑结构及选通和时钟引入 的。如图2所示,源CK和DQS信号到达目的地有延迟。对于存储器模块的每个存储器元件,这种延迟是不同的,必须逐个芯片进行调整,如果芯片有多于一个字节的数据,甚 至要根据字节来进行调整。该图说明了一个存储器元件。存储器控制器延迟了DQS,一次一步,直到检测到CK信号从0过渡到到1。这将再次对齐DQS和 CK,以便DQ总线上的目标数据可以可靠地被捕获。由于这是由DDR3存储器控制器自动做的,电路板设计人员无须担心实施的细节。设计人员会从额外的裕度

中得到好处,这是由DDR3存储器控制器中的写调整的特性所创建的。

在写调整期间,存储器控制器需要补偿额外的跨越时间偏移(对每个存储器器件,信号延迟是不同的),这是由于fly-by拓扑结构及选通和时钟引入 的。如图2所示,源CK和DQS信号到达目的地有延迟。对于存储器模块的每个存储器元件,这种延迟是不同的,必须逐个芯片进行调整,如果芯片有多于一个字节的数据,甚 至要根据字节来进行调整。该图说明了一个存储器元件。存储器控制器延迟了DQS,一次一步,直到检测到CK信号从0过渡到到1。这将再次对齐DQS和 CK,以便DQ总线上的目标数据可以可靠地被捕获。由于这是由DDR3存储器控制器自动做的,电路板设计人员无须担心实施的细节。设计人员会从额外的裕度

中得到好处,这是由DDR3存储器控制器中的写调整的特性所创建的。

4. 星形结构 star scheduling

结构如上图所示,该结构布线比较复杂,阻抗不容易控制,但是由于星形堆成,所以时序比较容易控制。星形结构需要特别注意D点到适合于单项数据传输,从D-R,而不适合于从R-D。匹配方式一般在R端做匹配,消除终端反射。 5.远端簇结构 far-end cluster scheduling

远端簇结构可以算是星形结构的变种,要求是D到中心点的长度要远远长于各个R到中心连接点的长度。各个R到中心连接点的距离要尽量等长,匹配电阻放置在D附近,常用语DDR的地址、数据线的拓扑结构。

在DDR的PCB设计中,一般需要考虑等长和拓扑结构。等长比较好处理,给出一定的等长精度通常是PCB设计师是能够完成的。但对于不同的速率的DDR,选择合适的拓扑结构非常关键,在DDR布线中经常使用的T型拓扑结构和菊花链拓扑结构,下面主要介绍这两种拓扑结构的区别和注意要点。 T型拓扑结构,也称为星型拓扑结构,其结构如图一所示。星型拓扑结构每个分支的接收端负载和走线长度尽量保持一致,这就保证了每个分支接收端负载同时收到信号,每条分支上一般都需要终端电阻,终端电阻的阻值应和连线的特征阻抗相匹配。星形拓扑结构可以有效地避免时钟、地址和控制信号的不同步问题。

图一 菊花链拓扑结构,如图二所示。和星型拓扑结构不同,菊花链拓扑结构没有保持驱动端到各个负载走线长度尽量一致,而是确保各个驱动端到信号主干道的长度尽量短。菊花链拓扑结构走线的特点,牺牲了时钟、地址和控制信号的同步,但最大的特点是尽可能降低各负载分支走线长度,避免分支信号对主干信号的反射干扰。

图二 在信号频率低于800MHz的情况下,上面两种拓扑结构均能满足系统性能需要。但是当信号速率到达1000MHz甚至更高,T型拓扑结构就不能满足性能需要。原因就在于T型拓扑结构过长的支路走线长度,在不添加终端电阻的情况下很难和主干道实现阻抗匹配,而为了实现各个支路的阻抗匹配添加终端电阻,又加大了电路设计的工作量和成本,是我们不愿意看到的。因此高速信号使用T型拓扑结构,特别是Stub>4的时候,支路信号对主干信号的反射干扰是很严重的。通常DDR2使用和速率要求不高的DDR3使用T型拓扑结构。菊花链拓扑结构主要在DDR3中使用,菊花链拓扑结构的主要优势是支路走线短,一般认为菊花链支路走线长度小于信号上升沿传播长度的1/10,可以有效削弱支路信号反射对主干信号的干扰,不同的书本上说法也不一样,大体上走线长度小于上升沿传播长度的1/6-1/10都是可以的,实际设计中我们肯定希望这个长度越短越好。菊花链拓扑结构可以有效抑制支路的反射信号,但相对于T型拓扑结构,菊花链拓扑结构的时钟、地址和控制信号并不能同时到达不同的DDR芯片。为了解决菊花链拓扑结构信号不同步的问题,DDR3的新标准中加入了时间补偿技术,通过DDR3内部调整实现信号同步。当信号频率高达1600MHz的时候,T型拓扑结构已经无能为力,只有菊花链或其衍生的拓扑结构能满足这样的性能需求。一般的DDR3都会建议采用菊花链拓扑结构的改进型拓扑结构,Fly-by拓扑结构,如图三所示。Fly-by拓扑结构要求支路布线长度Stub=0,Fly-by具有更好的信号完整性。

图三 在菊花链拓扑的实际应用中,为了抑制Stub过长和分支太多对主干信号的反射干扰,以及加强主干信号驱动能力,一般在末端预留端接电阻电路。末端下拉电阻会增大IO口驱动功耗,所以采用末端上拉电阻的方式进行端接。计算信号驱动部分的戴维南等效电压作为上拉电压Vtt,Rt为驱动部分的等效电阻,通常上拉电压取值为IO驱动电压的一般,即Vtt=Vddr/2。

3. fly-by scheduling 该结构是特殊的菊花链结构, stub线为0的菊花链。不同于DDR2的T型分支拓扑结构,DDR3采用了fly-by拓扑结构,以更高的速度提供更好的信号完整性。fly-by信号 是命令、地址,控制和时钟信号。如图1所示,源于存储器控制器的这些信号以串行的方式连接到每个DRAM器件。通过减少分支的数量和分支的长度改进了信号 完整性。然而,这引起了另一个问题,因为每一个存储器元件的延迟是不同的,取决于它处于时序的位置。通过按照DDR3规范的定义,采用读调整和写调整技术 来补偿这种延迟的差异。fly-by拓扑结构在电源开启时校正存储器系统。这就要求在DDR3控制器中有额外的信息,允许校准工作在启动时自动完成。

在写调整期间,存储器控制器需要补偿额外的跨越时间偏移(对每个存储器器件,信号延迟是不同的),这是由于fly-by拓扑结构及选通和时钟引入 的。如图2所示,源CK和DQS信号到达目的地有延迟。对于存储器模块的每个存储器元件,这种延迟是不同的,必须逐个芯片进行调整,如果芯片有多于一个字节的数据,甚 至要根据字节来进行调整。该图说明了一个存储器元件。存储器控制器延迟了DQS,一次一步,直到检测到CK信号从0过渡到到1。这将再次对齐DQS和 CK,以便DQ总线上的目标数据可以可靠地被捕获。由于这是由DDR3存储器控制器自动做的,电路板设计人员无须担心实施的细节。设计人员会从额外的裕度

中得到好处,这是由DDR3存储器控制器中的写调整的特性所创建的。

在写调整期间,存储器控制器需要补偿额外的跨越时间偏移(对每个存储器器件,信号延迟是不同的),这是由于fly-by拓扑结构及选通和时钟引入 的。如图2所示,源CK和DQS信号到达目的地有延迟。对于存储器模块的每个存储器元件,这种延迟是不同的,必须逐个芯片进行调整,如果芯片有多于一个字节的数据,甚 至要根据字节来进行调整。该图说明了一个存储器元件。存储器控制器延迟了DQS,一次一步,直到检测到CK信号从0过渡到到1。这将再次对齐DQS和 CK,以便DQ总线上的目标数据可以可靠地被捕获。由于这是由DDR3存储器控制器自动做的,电路板设计人员无须担心实施的细节。设计人员会从额外的裕度

中得到好处,这是由DDR3存储器控制器中的写调整的特性所创建的。

4. 星形结构 star scheduling

结构如上图所示,该结构布线比较复杂,阻抗不容易控制,但是由于星形堆成,所以时序比较容易控制。星形结构需要特别注意D点到适合于单项数据传输,从D-R,而不适合于从R-D。匹配方式一般在R端做匹配,消除终端反射。 5.远端簇结构 far-end cluster scheduling

远端簇结构可以算是星形结构的变种,要求是D到中心点的长度要远远长于各个R到中心连接点的长度。各个R到中心连接点的距离要尽量等长,匹配电阻放置在D附近,常用语DDR的地址、数据线的拓扑结构。

DDR布线要求及拓扑结构分析

在DDR的PCB设计中,一般需要考虑等长和拓扑结构。等长比较好处理,给出一定的等长精度通常是PCB设计师是能够完成的。但对于不同的速率的DDR,选择合适的拓扑结构非常关键,在DDR布线中经常使用的T型拓扑结构和菊花链拓扑结构,下面主要介绍这两种拓扑结构的区别和注意要点。 T型拓扑结构,也称为星型拓扑结构,其结构如图一所示。星型拓扑结构每个分支的接收端负载和走线长度尽量保持一致,这就保证了每个分支接收端负载同时收到信号,每条分支上一般都需要终端电阻,终端电阻的阻值应和连线的特征阻抗相匹配。星形拓扑结构可以有效地避免时钟、地址和控制信号的不同步问题。

图一 菊花链拓扑结构,如图二所示。和星型拓扑结构不同,菊花链拓扑结构没有保持驱动端到各个负载走线长度尽量一致,而是确保各个驱动端到信号主干道的长度尽量短。菊花链拓扑结构走线的特点,牺牲了时钟、地址和控制信号的同步,但最大的特点是尽可能降低各负载分支走线长度,避免分支信号对主干信号的反射干扰。

图二 在信号频率低于800MHz的情况下,上面两种拓扑结构均能满足系统性能需要。但是当信号速率到达1000MHz甚至更高,T型拓扑结构就不能满足性能需要。原因就在于T型拓扑结构过长的支路走线长度,在不添加终端电阻的情况下很难和主干道实现阻抗匹配,而为了实现各个支路的阻抗匹配添加终端电阻,又加大了电路设计的工作量和成本,是我们不愿意看到的。因此高速信号使用T型拓扑结构,特别是Stub>4的时候,支路信号对主干信号的反射干扰是很严重的。通常DDR2使用和速率要求不高的DDR3使用T型拓扑结构。菊花链拓扑结构主要在DDR3中使用,菊花链拓扑结构的主要优势是支路走线短,一般认为菊花链支路走线长度小于信号上升沿传播长度的1/10,可以有效削弱支路信号反射对主干信号的干扰,不同的书本上说法也不一样,大体上走线长度小于上升沿传播长度的1/6-1/10都是可以的,实际设计中我们肯定希望这个长度越短越好。菊花链拓扑结构可以有效抑制支路的反射信号,但相对于T型拓扑结构,菊花链拓扑结构的时钟、地址和控制信号并不能同时到达不同的DDR芯片。为了解决菊花链拓扑结构信号不同步的问题,DDR3的新标准中加入了时间补偿技术,通过DDR3内部调整实现信号同步。当信号频率高达1600MHz的时候,T型拓扑结构已经无能为力,只有菊花链或其衍生的拓扑结构能满足这样的性能需求。一般的DDR3都会建议采用菊花链拓扑结构的改进型拓扑结构,Fly-by拓扑结构,如图三所示。Fly-by拓扑结构要求支路布线长度Stub=0,Fly-by具有更好的信号完整性。

图三 在菊花链拓扑的实际应用中,为了抑制Stub过长和分支太多对主干信号的反射干扰,以及加强主干信号驱动能力,一般在末端预留端接电阻电路。末端下拉电阻会增大IO口驱动功耗,所以采用末端上拉电阻的方式进行端接。计算信号驱动部分的戴维南等效电压作为上拉电压Vtt,Rt为驱动部分的等效电阻,通常上拉电压取值为IO驱动电压的一般,即Vtt=Vddr/2。