项目硬件基于ARM+FPGA,因此选择Zynq Soc,ARM处理器和FPGA架构紧密集成,比之前分离芯片方便许多。有现成的Zynq核心板可以选择,集成了DDR等模块,不用考虑设计核心电路部分。软件方面,需要基于嵌入式Linux系统,编写应用程序。项目是数据采集及控制,需要较大存储空间。配置TF卡可以启动Linux,但考虑需要抗震动,核心板选择带eMMC。TF卡则可以布置底板上。最终选择的Xilinx Zynq-7020核心板是MYC-C7Z020。以下是转贴的介绍。

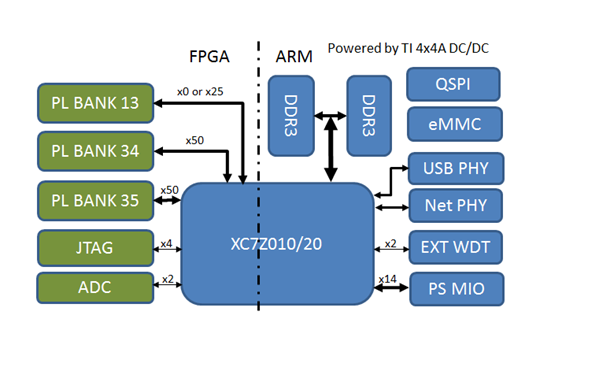

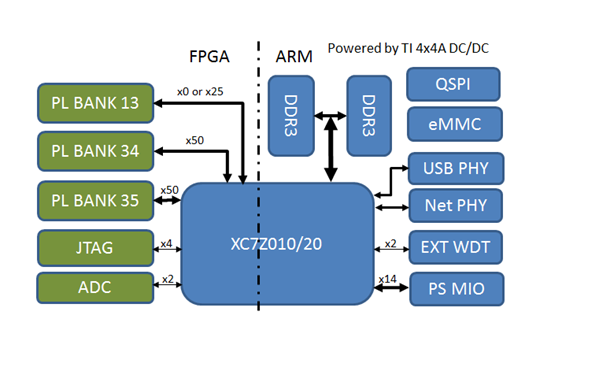

MYC-C7Z020是一款以Xilinx Zynq-7020作为核心的嵌入式核心板。采用了Xilinx新的基于28nm工艺流程的Zynq-7000 All Programmable SoC平台,将ARM处理器和FPGA架构紧密集成,PS单元拥有双核ARM Cortex-A9MPCore的高性能,低功耗特性,在设计中能更好的满足各种工业需要。

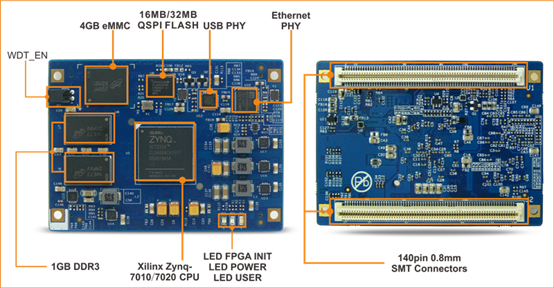

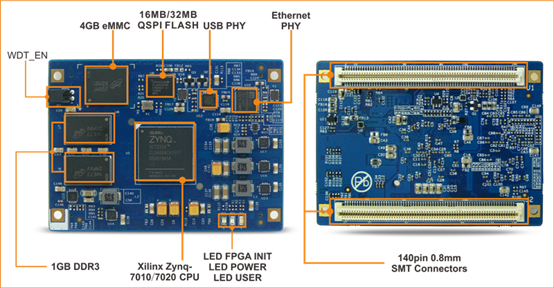

QSPI 默认32MB,16MB可选 PHY 1路千兆网口PHY

1路USB PHY 看门狗 外置看门狗电路 指示灯 一个电源指示灯(蓝 {MOD}),一个FPGA烧写完成指示(红 {MOD})和一个用户指示灯(绿 {MOD})

核心板功能

项目 参数 CPU 处理器系统单元(PS):- 基于高性能双核ARM Cortex-A9处理系统

- 双通道高速缓存

- 最高支持1GB DDR

- 最高支持866MHz主频

- 支持10/100/1000M Ethernet

QSPI 默认32MB,16MB可选 PHY 1路千兆网口PHY

1路USB PHY 看门狗 外置看门狗电路 指示灯 一个电源指示灯(蓝 {MOD}),一个FPGA烧写完成指示(红 {MOD})和一个用户指示灯(绿 {MOD})

接口信号

项目 参数 网口 1路千兆网口 USB 1路USB OTG2.0 串口 2路串口(串口,I2C,CAN在PS会有复用,或通过PL引脚实现) I2C 2路I2C接口(串口,I2C,CAN在PS会有复用,或通过PL引脚实现) CAN 2路CAN总线(串口,I2C,CAN在PS会有复用,或通过PL引脚实现) SPI 2路SPI(通过PL引脚实现) ADC 1路独立差分ADC,16路ADC从PL引脚引出 SDIO 1路SDIO,接TF卡

产品结构图