Agenda:

差分信号的优点

- 抗干扰能力强,因为两根差分走线之间的耦合很好,当外界存在噪声干扰时,几乎是同时被耦合到两条线上,而接收端关心的只是两信号的差值,所以外界的共模噪声可以被完全抵消。差分电路对于类似地弹以及其它可能存在于电源和地平面上的噪音信号是不敏感的。

- 能有效抑制 EMI,由于两根信号的极性相反,他们对外辐射的电磁场可以相互抵消,耦合的越紧密,泄放到外界的电磁能量越少。

- 时序定位精确,由于差分信号的开关变化是位于两个信号的交点,而不像普通单端信号依靠高低两个阈值电压判断,因而受工艺,温度的影响小,能降低时序上的误差,同时也更适合于低幅度信号的电路。目前流行的LVDS(low voltage differential signaling)就是指这种小振幅差分信号技术。

高速PCB layout设计应考虑的点

SerDes/Differential Pair-- The Feature of High Speed Design- PCB material

- Stackup

- Crosstalk

- FWE(Fiber Wave Effect)

- Stubs & backdrilling

- Surface roughness

- IL/RL/FEXT/NEXT(Insertion/Return Loss/Crosstalk)

- BOR(Break Out Region) or signal launch

- DC blocking cap planes

- Bypass/Decoupling mounting inductance

PCB Material

Design Misc–PCB板材差分信号的回流

Reference Connectivity Stitching Via s for Return Currents电流流经封闭回路的磁场,会构成磁通量,其磁通量与电流的比值,便构成了电感,而电感又与感抗有关。回路面积与感抗成正比,若回路面积越小,则感抗就越小。亦即高频讯号的回流电流,会走可以构成最小回路面积的路径。

- 低频讯号的回流电流,会走最小电阻路径

(当讯号为低频时,其回流电流只集中在Load到Source这段路径) - 而高频讯号的回流电流,会走最小感抗路径

(但当讯号为高频时,其回流电流会集中在原路径下方)

以Any Layer的十层板为例,其讯号走线与GND的距离为2.8 mil,就算下层挖空,也只有5.6 mil。但表层走线若要达到100奥姆,其间距差不多要10 mil,

因为与GND的距离较近,亦即GND能提供较小的回路面积,这表示以GND为回流路径的机会大得多。瞬时时,其回流电流都集中在差分讯号原路径下方的GND。

- 差分讯号的回流电流,确实是存在于GND => 这是指瞬时

- 差分对如果完全对称的话,回流电流为0 => 这是指稳态

阻抗的连续性

在实现高速设计时,高速信号的输路径中的物理几何结构的任何微小的不连续都会显着降低信号质量。 这种降级包括信号幅度的损失,信号上升时间的减少和抖动的增加。 因此,必须识别高速通道中的这些不连续,并提供减轻其影响的方法,以实现更好的信号传输。其中,元器件封装焊盘,连接器和信号打孔换层都会会造成阻抗不连续及回流路径的变化stitching via

基于之前回流路径的分析以及信号打孔换层都会会造成阻抗不连续及回流路径的变化的事实,需要为信号的过孔提供额外的接地过孔为其提供连续的回流路径。

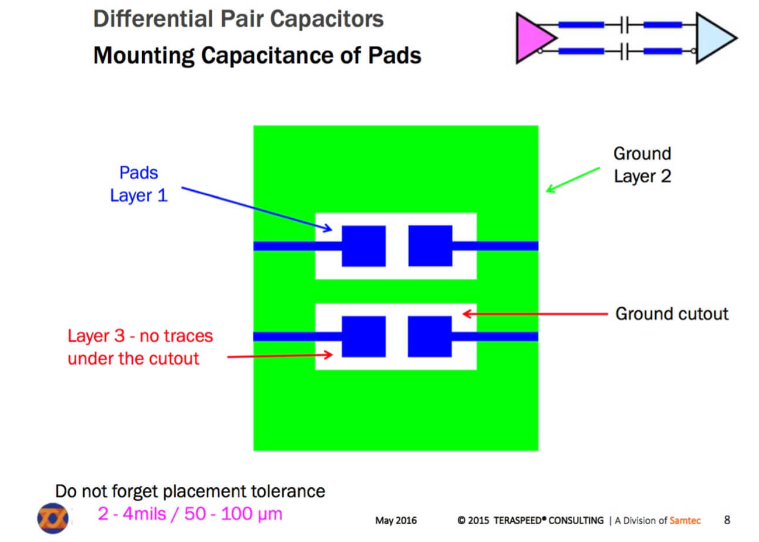

焊盘参考平面挖空

同样是为了阻抗的连续性,为了减少焊盘与参考平面的寄生电容,隔直电容是高速串行通道中阻抗不连续的常见来源。关于优化焊盘阻抗不连续问题,可以参考 Altera的Application Note 530《Optimizing Impedance Discontinuity Caused by Surface Mount Pads for High-Speed Channel Designs》,依据叠层的不同,挖空尺寸也不同(要simulation)

背钻 back drilling

背钻是一种有效减小stub的高性价比方案(相比blind/buried via)背钻技术——可控深度钻孔(CDD),也称为背钻孔。它可以将未使用的铜质筒体或分叉短线从印刷电路板通孔中去除。当高速信号在PCB板层之间传输时穿过了一个铜质筒体,就会产生失真。如果信号层中存在分叉短线,并且该短线较长,失真将会成为严重的问题。在制造完成后,可使用稍大的钻头重钻这些孔,去除分叉短线。将孔背钻至可控的深度,接近但不触及过孔使用的最后一层。考虑到制造和材料差异,好的制作商可使背钻孔的遗留短线达到7mil,理想的剩余短线长度应小于10mi。

如下图示例:layer 8可以不用背钻,原因在于离bottom很近,stub影响很小,且加工控制不易

由于STUB本身的电感,以及信号孔与接地孔两者之电容,另加上下两孔环间的电容,均将严重影响到信号的完整性,stub经过背钻扩孔二消除后,其插入损耗将显著降低

FWE(PCB 玻纤效应)

PCB基材是由树脂、玻纤、铜箔、填料等压合而成,玻纤布的编号是按照纬纱宽度、经纱的宽度,纬纱之间的间隙,以及经纱之间的间隙,进行编号定义的。如下图,差异最大的地方在于X-Y轴的玻纤布交织的窗口大小不一样,像106,,1080都属于窗口比较大,像1067,1086窗口是很小的。

窗口大会有很多坏处,走在窗口里面和外面的信号阻抗和延时都会有较大的差异,主要原因是由于玻璃布和树脂的介电常数相距甚远(玻璃布一般在6左右,树脂在2.5)。

通过视频中的PPT,我们可以看到一对儿差分线,其中一根儿走在玻璃纤维上,一根儿走在纤维空隙中。因为介质的介电常数不一样,造成两根传输线的阻抗不一样,这导致俩风险: 一是阻抗不匹配,二是信号传输速度不一样,对于25Gbps以上的信号会导致严重的信号失真。 应对措施

- 使用扁平开纤布来减小窗口,提升性能。实际上扁平和开纤是两个概念,它们的示意图如下,开纤就是把玻璃纤维打散,扁平就是把它们压扁,要达到的效果都是为了减小窗口的大小。

- 不同的材料等级的板材除了损耗因子DF不一样之外,实际上介电常数DK也是不同,DK的差异主要就是表现为玻璃布的DK差异,越好的板材DK越小,实际上也就是玻璃布的DK做得越小,这样的话玻璃布就与树脂的DK越接近,即使有窗口影响也会减弱。

- 另外我们知道一块大料,玻纤是沿X轴和Y轴交织的,因此往这两个方向走线势必或多或少受到玻纤效应的影响,如果走线能不沿着两个方向传输的话,也会有一定的效果,这里的做法有两个,一个是把线按一定的角度来走,3度、7度、11度,或者把主要器件旋转(例如45度方向);另外一个可以把PCB旋转,不过会浪费一定的板材利用率。

- 另外还有一个方法,根据概率的原理,即使一张玻璃布窗口很大,如果我们叠两张的话,实际上这时窗口露出来的概率会大大降低,例如用1080,我们叠两张的话也能起到很好的作用。

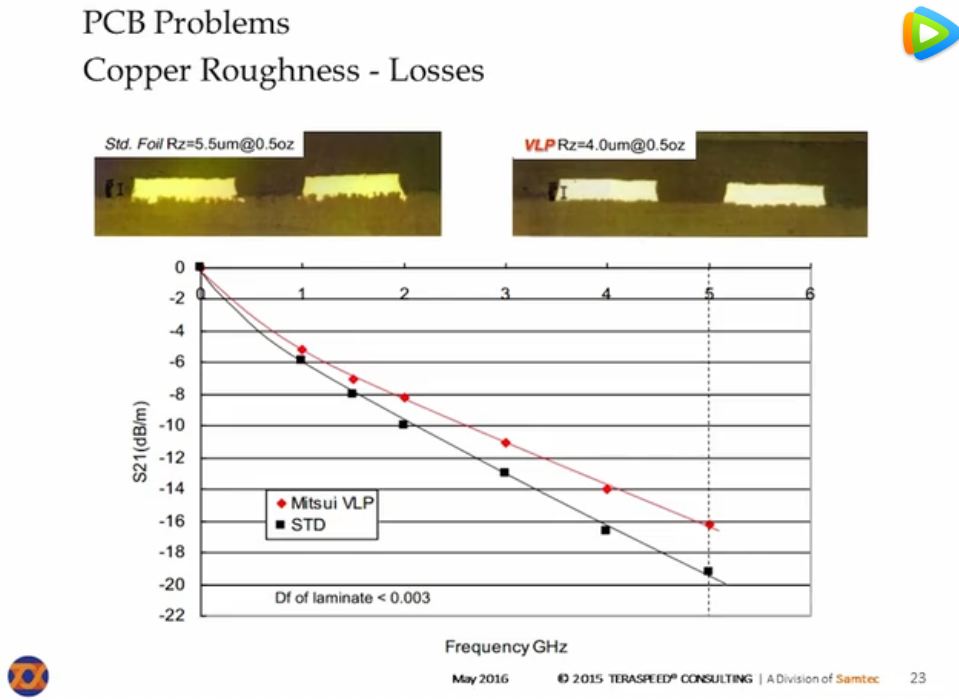

Surface roughness

趋肤效应:信号高速/高频化是信号传输越来越集中于导线“表层”- 当频率达1GHz时,其信号在导线表面的传输厚度仅为2.1μm,如果导体表面粗糙度为3-5μm,信号传输仅在粗糙度的厚度范围内进行;

- 当信号传输频率提高到10GHz时,其信号在导体表面的传输厚度为0.7μm,信号传输更是在粗糙度范围内进行。

由于趋肤效应的存在,高速PCB如果继续使用常规(STD)铜箔,其结果是:随信号传输频率增加,趋肤效应导致的信号“失真”愈发严重。因此,当前的高速材料上低粗糙度铜箔的应用越来越广泛:

通过扫描电镜和金相显微镜可看出STD、RTF和HVLP铜箔(厚0.5oz)的表面形貌(见图2)。

- Mid Loss材料和Low Loss材料都采用反转(RTF)铜箔作为标配铜箔;

- Very Low Loss材料虽然也是标配RTF铜箔,但客户设计多是采用超低轮廓(HVLP)铜箔;

- 对于Ultra low loss材料,HVLP铜箔已成为标配。

- STD铜箔毛面粗糙度(Rz)约为5μm,光面粗糙度3μm;

- RTF铜箔毛面、光面粗糙度约3μm;

- HVLP铜箔光面、毛面粗糙度均在2μm以内。

PCB中传输线损耗主要包括介质损耗和导体损耗两个部分。对应常规FR4材料,1GHz是介质损耗和导体损耗的分水岭(见图3),1GHz以下时导体损耗占主要;频率超过1GHz后,介质损耗占主要。

然而,对应Very Low Loss材料,介质损耗已不是主要损耗,10GHz频率下导体损耗约占传输线整体损耗的60%。图4是基于联茂IT-968材料模拟计算出的微带线、带状线导体损耗(导损)和介质损耗(介损)情况。由图可以看出,带状线理论计算的损耗与实测损耗基本一致;不管是微带线还是带状线,介质损耗都远小于导体损耗。

从Mid Loss到Ultra Low Loss材料,导体损耗所占的比重逐渐增加。高速材料采用不同类型铜箔后,测得的损耗也存在明显差异。图5是IT-968材料采用STD、RTF和HVLP铜箔时,制作的带状线信号损耗测试结果。

Crosstalk

串扰是通过容性、感性或者传导耦合引起的一种现象,那这种耦合或者传导的现象在PCB电路板上是不可避免的,所以只要不影响到产品正常工作的串扰都是可以接受的比如下列是OIF CEI对串扰的要求:经验是什么呢?对于串扰而言,没有特殊要求的情况下,就按照信号幅值或者电源电压大小的5%或者-26dB计算,如果信号幅值或者电源电压比较小,则把要求再定紧一些,比如1%或者-40dB。

- The Integrated Crosstalk Noise (ICN) is less than 3.9 mV.

- MDNEXT shall be less than 1.35 mV RMS.

- MDFEXT shall be less than 3.6 mV RMS

等长 or 平行匹配

在实际的 PCB 布线中,往往不能同时满足差分设计的要求。由于管脚分布,过孔,以及走线空间等因素存在,必须通过适当的绕线才能达到线长匹配的目的,但带来的结果必然是差分对的部分区域无法平行。PCB 差分走线的设计中最重要的规则就是匹配线长,其它的规则都可以根据设计要求和实际应用进行灵活处理。让差分走线靠近无非是为了增强他们的耦合,既可以提高对噪声的免疫力,还能充分利用磁场的相反极性来抵消对外界的电磁干扰。k可以有多种途径实现,增大与其它信号走线的间距是最基本的途径之一,电磁场能量是随着距离呈平方关系递减的,一般线间距超过4 倍线宽时,它们之间的干扰就极其微弱了,基本可以忽略。此外,通过地平面的隔离也可以起到很好的屏蔽作用,这种结构在高频的(10G 以上)IC 封装PCB 设计中经常会用采用,被称为 CPW 结构,可以保证严格的差分阻抗控制(2Z0)

Misc

AC Losses

Via Properties

modify via Pad stack for high speed using—remove all those unused pads

Capacitor Mounting

要关注capacitor mounting inductance,两个过孔尽量靠近;via on pad的效果最好,但是由于会有漏锡等情况的发生,生产上一般不推荐,

reference list

– link 应对未来高速SerDes应用的PCB设计要点– 差分信号的回流路径问题讨论

– 如何应对未来高密SerDes设计的挑战

– Altera: AN 530

– 高速先生教你如何轻松对付玻纤效应

– 铜箔粗糙度在高速PCB中的应用

– S-081-100G以上骨干网用高速PCB孔损耗技术研究

– 在电路设计中,什么样的串扰是可以接受的??