设置板型边界就是禁止布线层的边界:

先到禁止布线层绘制,边界。然后选中这些边界。然后到设计菜单的板子外形,选择根据选择的对象定义板子外形。

检查没有连接的飞线(布线是否完成):

DRC(designrule check)检查会自动检查飞线,如果有的话,会显示有没布通的网络。

在规则里设置未布线网络,打开tool-> design rule check (DRC),在Electrical中选中(Un-RoutedNet)和(Un-Connected Pin)违规即可看到有无未布的导线

线改成其它层后消失

这是因为现在的线所处的位置已经不是在板型之内了,最简单的办事暂时把板型加宽,最后在恢复板型即可

高亮部分的对比度

在用交互布线(P+T)的时候发现界面有时会像下面这样:

其他部分太模糊了,不好布线,在QQ群里找到了这样的办法,点击上图右下角的Mask Level(圈住的部分),弹出下面的窗口:

其他部分太模糊了,不好布线,在QQ群里找到了这样的办法,点击上图右下角的Mask Level(圈住的部分),弹出下面的窗口:

上面的第一项就是对比度设置,做如下调整:

上面的第一项就是对比度设置,做如下调整:

这时候再次交叉布线,得打这样的结果:

这时候再次交叉布线,得打这样的结果:

这个才是比较好的界面

这个才是比较好的界面

-------从可用的库中更新元件封装。

在 PCB 编辑器中执行命令 Tools » Update from PCBLibraries。这个命令会为每个元件封装做一个详细的比较,用户可以完全控制更新哪些封装。这个工具也可作为设计验证和发布过程的一部分,在 Output Job 文件中包含 Footprint Validation Report。

(图1)

2.为差分对添加差分符号,如(图2)。Place-->directives-->differential pair (放置、指令符、差分对),然后放到差分线上即可(可以不需要调整任何值)

(图1)

2.为差分对添加差分符号,如(图2)。Place-->directives-->differential pair (放置、指令符、差分对),然后放到差分线上即可(可以不需要调整任何值)

(图2)

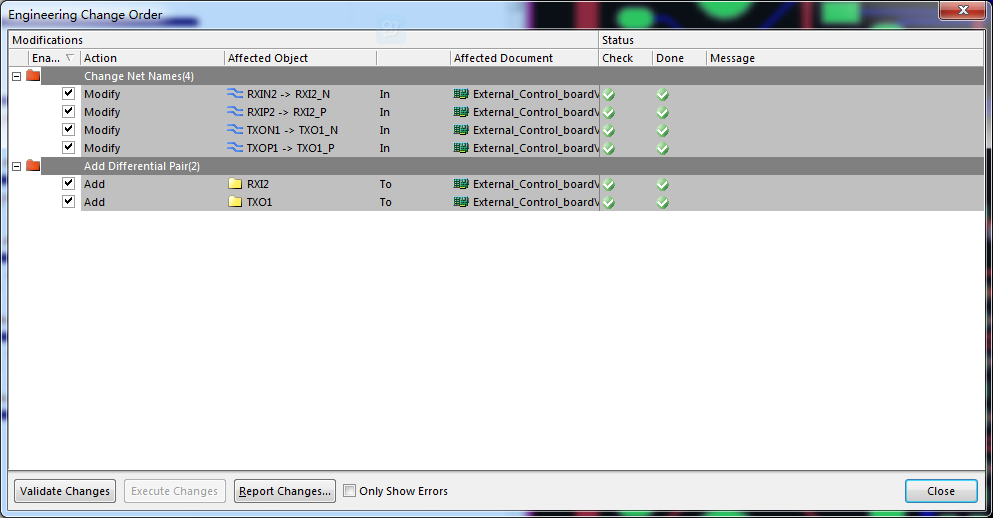

3.更新到PCB。Design-->Update PCB……如(图3)

(图2)

3.更新到PCB。Design-->Update PCB……如(图3) (图3)

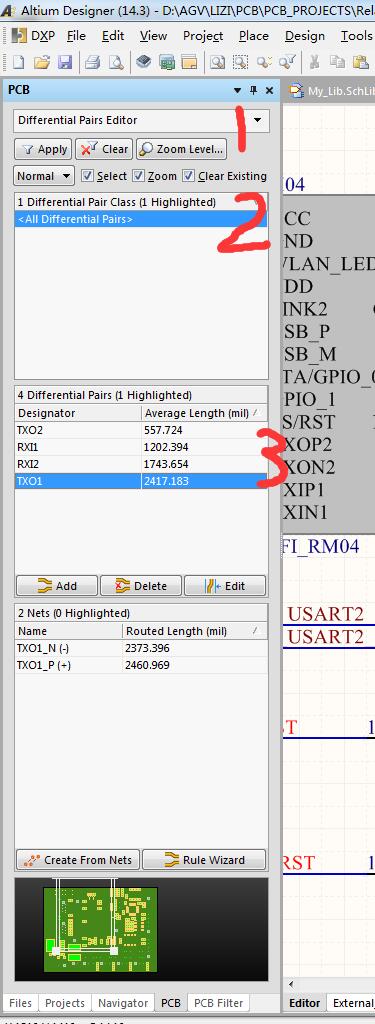

4.更新PCB后可在左边栏的PCB上按(图4)步骤即可看到设置的差分对。

(图3)

4.更新PCB后可在左边栏的PCB上按(图4)步骤即可看到设置的差分对。

(图4)

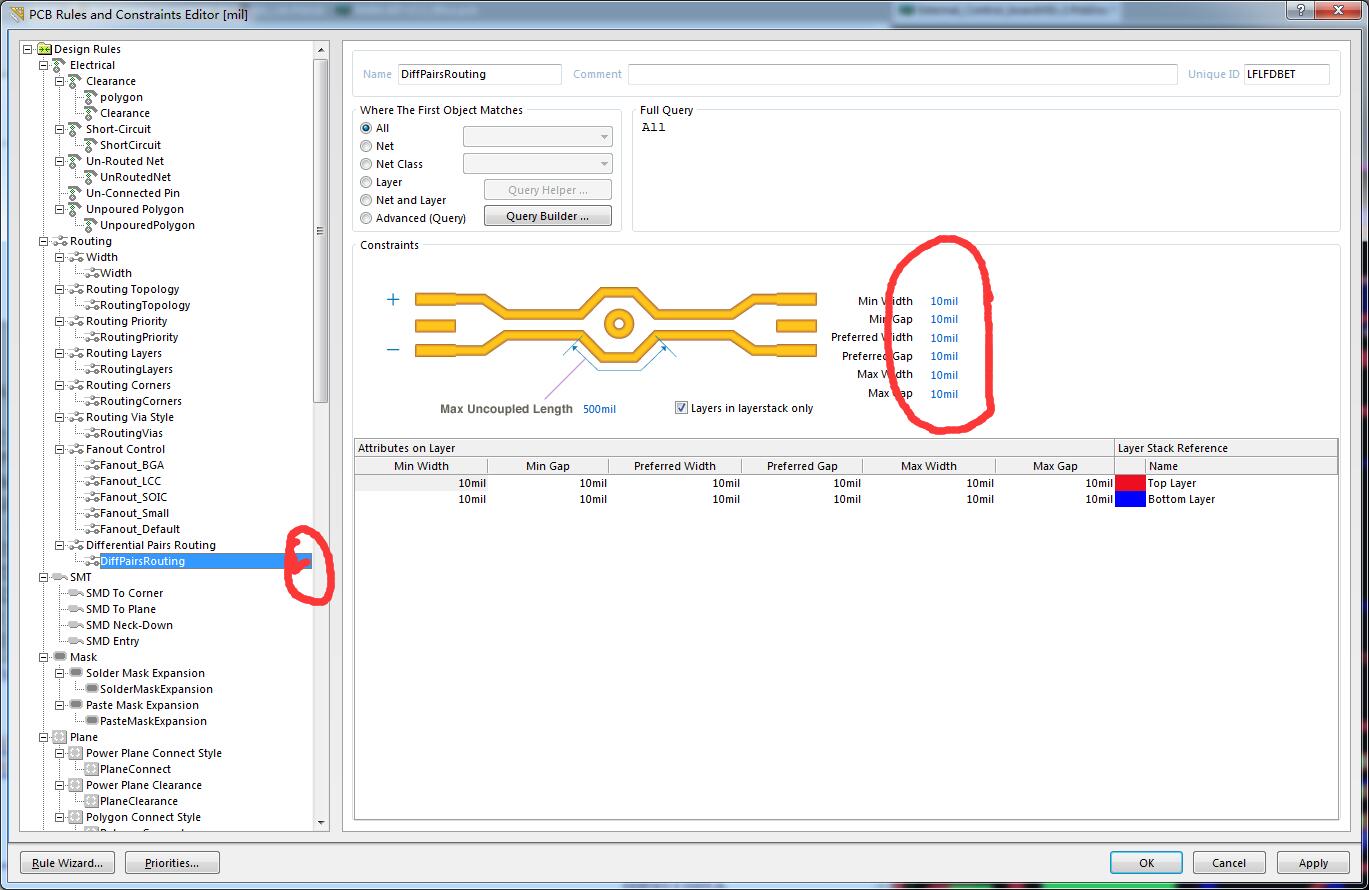

5.设置差分对的规则 Design-->Rules,如(图5)

(图4)

5.设置差分对的规则 Design-->Rules,如(图5)

(图5)

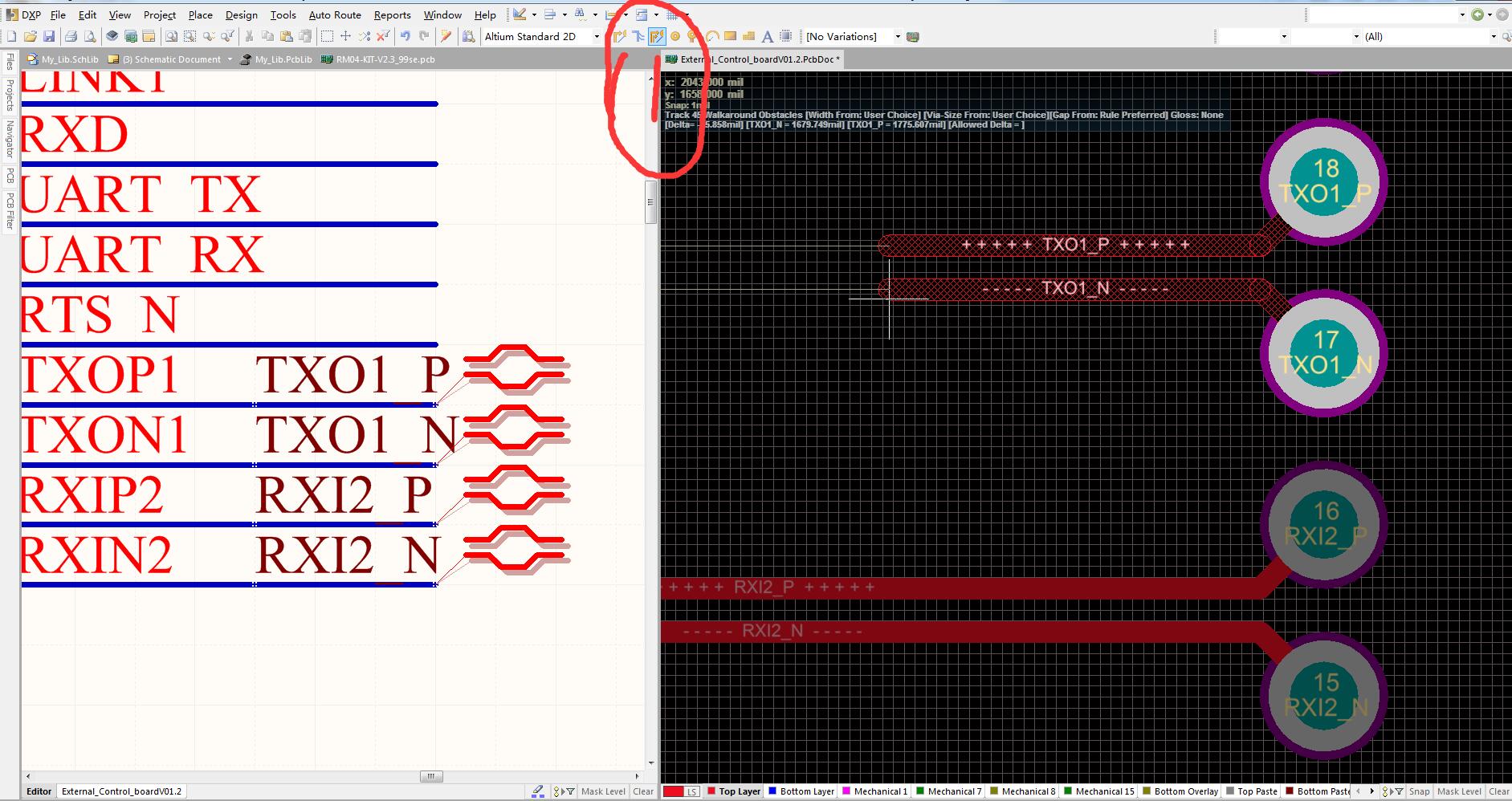

6.下面就是画差分线了 Place-->interactive differential pair routing ,如(图6)

(图5)

6.下面就是画差分线了 Place-->interactive differential pair routing ,如(图6)

(图6)

这一路下来,看,是不是很简单。当然啦,对于一些差分布线的规范什么的,这里就不再献丑了,毕竟不是一句两句就说的明白(其实我是怕误导别人)。总之,对于硬件设计就是多动手,仿真也好实物也好,要多做调试。

(图6)

这一路下来,看,是不是很简单。当然啦,对于一些差分布线的规范什么的,这里就不再献丑了,毕竟不是一句两句就说的明白(其实我是怕误导别人)。总之,对于硬件设计就是多动手,仿真也好实物也好,要多做调试。

任意角度:

摘录于:https://jingyan.baidu.com/article/49711c61853139fa451b7c61.html

任意角度:

摘录于:https://jingyan.baidu.com/article/49711c61853139fa451b7c61.html

其他部分太模糊了,不好布线,在QQ群里找到了这样的办法,点击上图右下角的Mask Level(圈住的部分),弹出下面的窗口:

其他部分太模糊了,不好布线,在QQ群里找到了这样的办法,点击上图右下角的Mask Level(圈住的部分),弹出下面的窗口:

上面的第一项就是对比度设置,做如下调整:

上面的第一项就是对比度设置,做如下调整:

这时候再次交叉布线,得打这样的结果:

这时候再次交叉布线,得打这样的结果:

这个才是比较好的界面

这个才是比较好的界面

更新修改后的元件封装

本文摘录于:http://www.51hei.com/bbs/dpj-98161-1.html Altium Designer当PCB库中零件的封装修改后,要更新到PCB文件中:有两种方式来更新这修改后的元件封装: 1从打开的元件库更新元件封装到PCB文件。 2在PCB文件中更新来自库的元件封装。 要从打开的库将每个封装实例更新到当前打开的PCB文件:在PCB库编辑器的库面板中右击封装名称------选择命令 Update PCB with放置差分信号

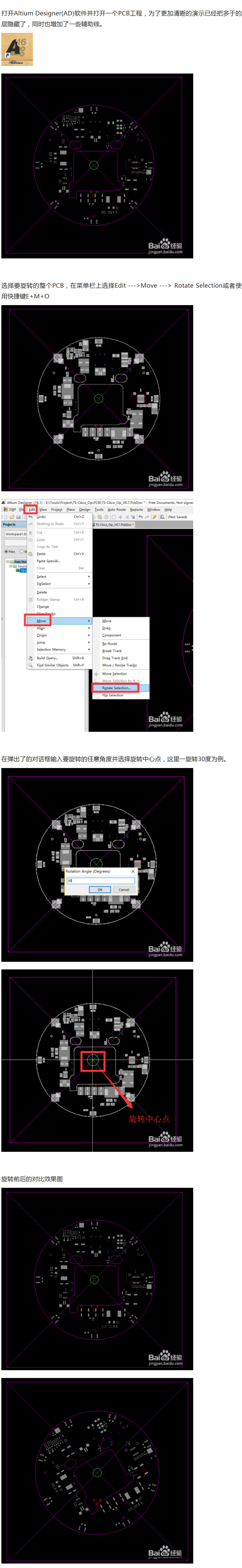

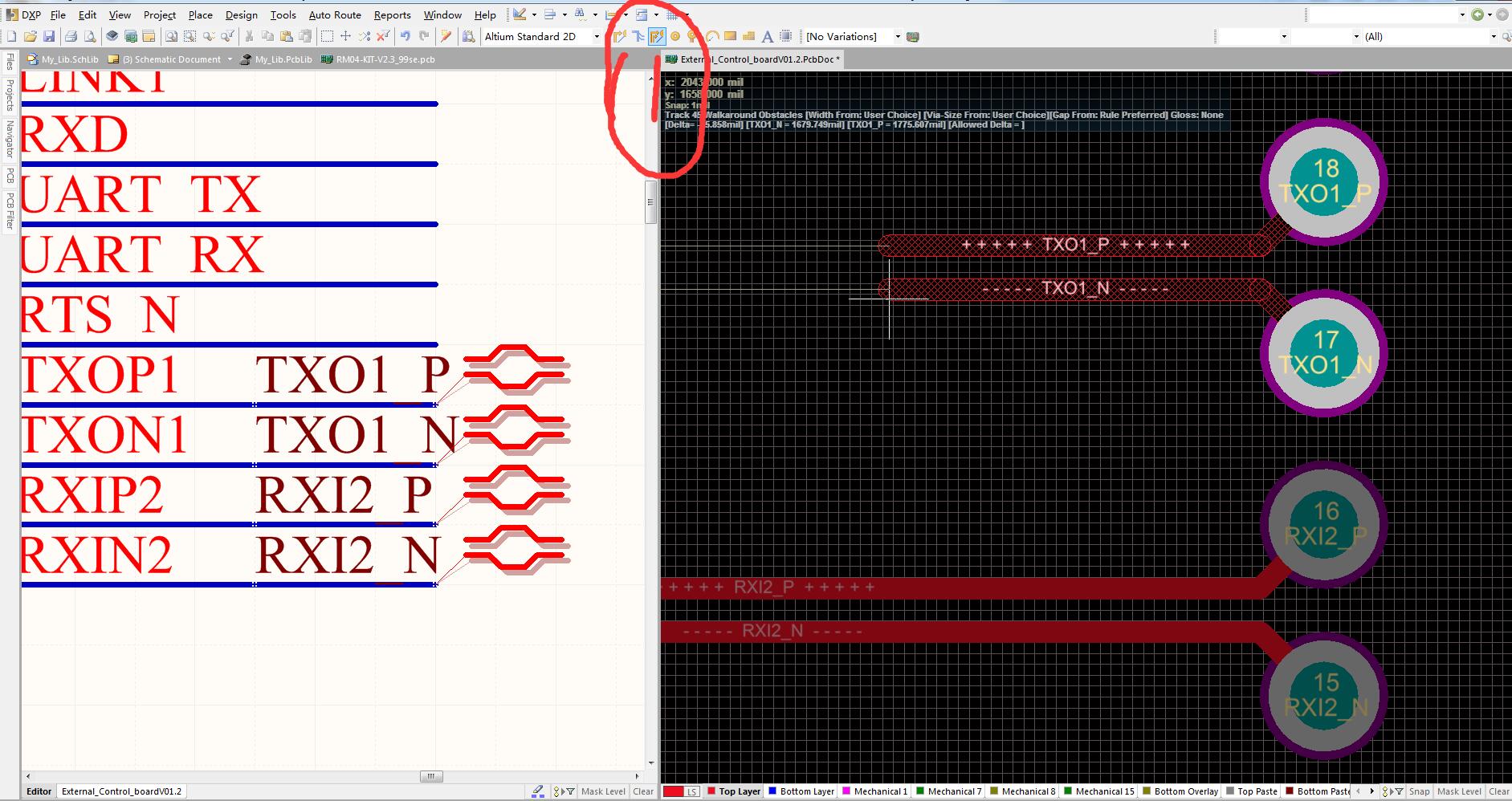

网上看到Altium Designer画差分线的用法,简直就是在误导人!居然在PCB文件上直接添加差分线做差分处理!且不说这个设计的步骤就是错的,而且很有个很重要的问题,那就是当你再次改变原理图,然后更新PCB的时候你会发现:你在PCB上设置的差分对没了!(本人使用AD14验证过,其余版本未知) 在此,贴图做一个从原理图到PCB的差分信号设置方法。 1.正确设置差分信号的名称:两条差分信号的名称是有要求的,要求后缀必须是 "_P"与“_N”,即代表差分对的“+”与“-”,如(图1) 把标号为TXOP1的线再增加一个名称TXO1_P(也可直接把TXOP1改成TXO1_P),既然是差分对,那就是成对出现, 所以再把TXON1增加名称TXO1_N,前面说过,差分对的名称必须是一样的,但后缀不一样,分别是“_P”与“_N”, 所以TXO1_P、TXO1_N就是一对差分对了。 (图1)

2.为差分对添加差分符号,如(图2)。Place-->directives-->differential pair (放置、指令符、差分对),然后放到差分线上即可(可以不需要调整任何值)

(图1)

2.为差分对添加差分符号,如(图2)。Place-->directives-->differential pair (放置、指令符、差分对),然后放到差分线上即可(可以不需要调整任何值)

(图2)

3.更新到PCB。Design-->Update PCB……如(图3)

(图2)

3.更新到PCB。Design-->Update PCB……如(图3) (图3)

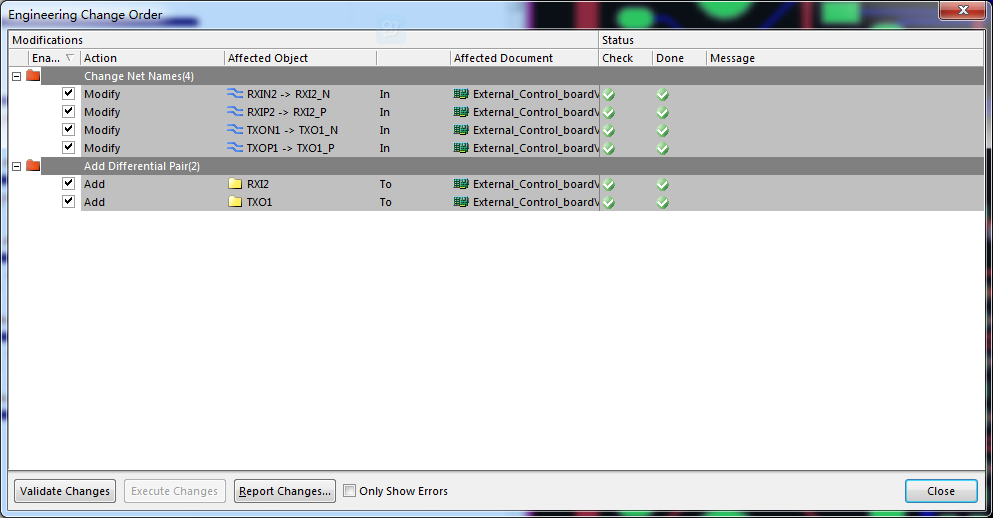

4.更新PCB后可在左边栏的PCB上按(图4)步骤即可看到设置的差分对。

(图3)

4.更新PCB后可在左边栏的PCB上按(图4)步骤即可看到设置的差分对。

(图4)

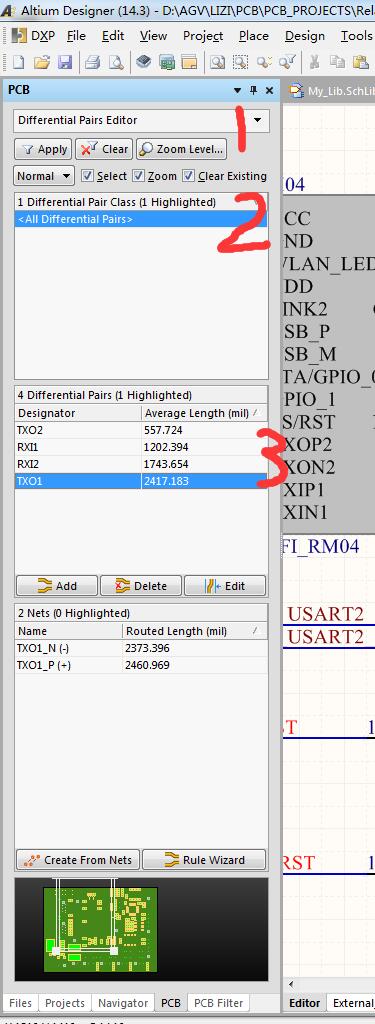

5.设置差分对的规则 Design-->Rules,如(图5)

(图4)

5.设置差分对的规则 Design-->Rules,如(图5)

(图5)

6.下面就是画差分线了 Place-->interactive differential pair routing ,如(图6)

(图5)

6.下面就是画差分线了 Place-->interactive differential pair routing ,如(图6)

(图6)

这一路下来,看,是不是很简单。当然啦,对于一些差分布线的规范什么的,这里就不再献丑了,毕竟不是一句两句就说的明白(其实我是怕误导别人)。总之,对于硬件设计就是多动手,仿真也好实物也好,要多做调试。

(图6)

这一路下来,看,是不是很简单。当然啦,对于一些差分布线的规范什么的,这里就不再献丑了,毕竟不是一句两句就说的明白(其实我是怕误导别人)。总之,对于硬件设计就是多动手,仿真也好实物也好,要多做调试。

删除没有网络的连线

当画好一个PCB后想修改某系网络,在原理图修改后更新到PCB发现要修改的那些走线都变成了NOT-NET,这时候不管怎么选择都不能够选择完整的线路拓扑,也就是完整的连线了; 这时候通过“CTRL+H”快捷键(AD的快捷键请看:https://blog.csdn.net/chengdong1314/article/details/52299362),然后选择要修改的走线,知识后该条走线就被选中,然后取消掉焊盘的选中,最后修改网络即可!将PCB板子旋转90°

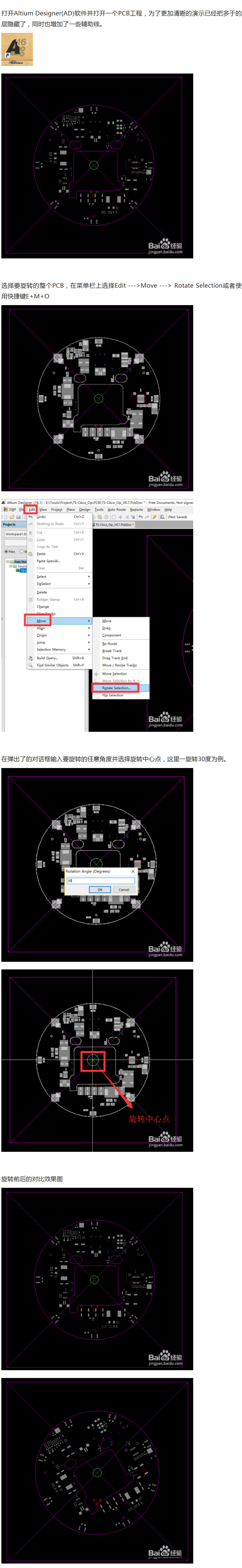

摘录于:https://zhidao.baidu.com/question/1370696219146865099.html 任意角度:

摘录于:https://jingyan.baidu.com/article/49711c61853139fa451b7c61.html

任意角度:

摘录于:https://jingyan.baidu.com/article/49711c61853139fa451b7c61.html