前言:本文使用AD版本为AD16,不同版本的AD,在一些细节上可能不同。

文章目录

I、工程创建至完成

一、创建

①File → New → Project②Preject Types,为工程类型选择,选择PCB Project

③Project Templates,为模板选择,一般Default即可

④Name:工程名

⑤Location:文件位置(右侧“Create Project Folder”意思是创建一个新文件夹,若勾选,则将在指定路径下新建一个与“Name”同名的文件夹)

二、环境搭建

①添加原理图文件:Preject → Add New to Project → Schematic → 保存(文件名推荐使用工程名)②添加PCB文件:Preject → Add New to Project → PCB → 保存(文件名推荐使用工程名)

③添加原理图库文件:Preject → Add New to Project → Schematic Library → 保存

④添加PCB库文件:Preject → Add New to Project → PCB Library → 保存

注:

Add Existing to Preject,意思是添加已存在的文件;

通常原理图文件和PCB文件需要新建;

原理图库和PCB库,因重复性高,可以考虑自己创建、制作个人专用版库文件;

在库文件中没有自己需要的器件时,直接动手绘制,并添加进库文件,以丰富库文件。

三、原理图库与PCB库

“原理图库中,元器件引脚的Designator”、“PCB库中,元器件对应封装的引脚Designator”,两者要一致。两者若不一致,将导致原理图处的连线,不能对应到相应封装上,最终PCB板子上将没有这条连线。

解释:

绘制元器件时,元器件的引脚参数中,Designator是引脚的电气名称;

该名称与对应元器件封装的相应引脚的电气名称相同;从而将原理图中的虚拟引脚,与PCB板中的实际引脚互相连接对应。

此外还有个“Display Name”,用于绘制、查阅原理图时,方便的看出导线连接的对象。

另,在使用软件自带的原理图库、自己画封装库的情况下,元器件引脚的Designator通常是隐藏的。查看方法如下:

双击需要查看引脚Designator的元器件,然后点击“Edit Pins…”,在弹出的对话框中,将“Number”一列勾上;

这样该元器件引脚的Designator就会显示出来了。

四、原理图绘制

①元器件放置、连线②统一修改或添加元器件封装,Tools → Footprint Manager

③生成PCB,Design → Update PCB Document…

五、PCB绘制

①PCB板大小裁定,KeepOut Layer层,Place – Line,画出PCB板轮廓;然后Ctrl + A全选,Design → Board Shape →Define from selected objects②元器件位置布局

③连接各元器件之间的线路

④线路优化处理(泪滴、铺铜等)

⑤规则检查,Tools → Design Rule Check → Run Design Rule Check

.

.

.

然后…0 error 就可以完工啦!

.

.

.

II、常见问题、技巧汇总

一、系统环境配置类

1.汉化的开启与关闭

在有汉化包的前提下 DXP → Preferences → System → General → Localization下的“Use localized resources” 勾上即显示汉化菜单;去掉即显示英文菜单。2.PCB绘制时,把网格线换成网格点

右键 → Snap Grid → Grid Properties,在弹出的对话框中,把“Fine、Coarse”选项都设置成“Dos”即可。二、原理图类

1.元器件变动,更新至原理图

SCH Library处,找到需要更新的元器件,右键选择“Update Schematic Sheets”。三、PCB类

1.原理图变动,更新至PCB

Design → Update PCB Document…若出现Unknown Pin的问题,则在PCB绘制界面,清除原有网络后再重现更新即可(Design → Netlist → Clear All Nets)。

2.怎样快速清除布线?

Tools → Un-Route →①All(所有)

②Net(网络)

③Connection(连接)

④Component(元器件)

3.怎样使VCC网络布线自动加粗?

Design → Rules找到Routing下的Width,在Width下新建相应规则。

4.封装变动,更新至原理图和PCB

首先需要更新至原理图,在原理图处增删封装即可;原理图处更新完毕后,Design → Update PCB Document…,将原理图变动传递给PCB。

5.泪滴处理

Tools → Teardrops,点OK即可。6.铺铜处理

首先先划出不需要铺铜的区域(固定孔周围等),Place → Polygon Pour Cutout; 然后Place → Polygon Pour在弹出的对话框中需要对“Layer(需要铺铜的层)、Connect to Net(铺铜连接的网络)”两者进行配置,配置完毕后点击“OK”开始绘制铺铜区域。

7.自定义零点坐标位置

Edit → Origin → Set,然后点自己想要设置成零点的地方即可。8.GND网络名变成了和GND相连的一个NET名,怎样使该网络以GND为名?

网络标号和GND相连,即默认改变GND网络名。 可以在标号到GND之间添加一个0Ω电阻。或者不使用网络标号,直接使用导线连接。两种方法都能使GND网络依旧以GND为名。

9.怎么隐藏某一网络的连接提示线,例如隐藏GND网络

View → Connections → Hide Net然后选择需要隐藏的网络提示线即可(或者使用快捷键N,也能调出)。

10.怎么把铺铜隐藏(不是删除)?

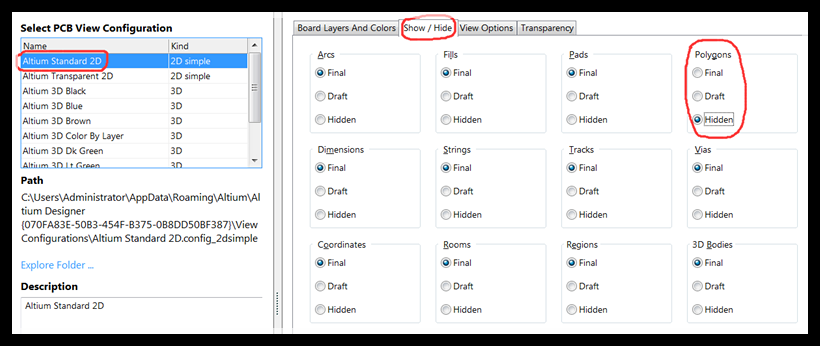

快捷键L,调出界面选择Altium Standard 2D → Show/Hide,然后在Polygons一栏选择Hiden即可