软件版本号:Cadence 16.5

使用工具:Allegro PCB PI Option XL Power Integrity

使用资源:仿真实例下载地址:http://download.csdn.net/detail/wu20093346/7660995

仿真目的:依据单节点仿真的结果去选择去耦电容器,从而使PCB满足所设定的目标阻抗

1.创建新的PCB文件

打开Allegro PCB PI Option XL:

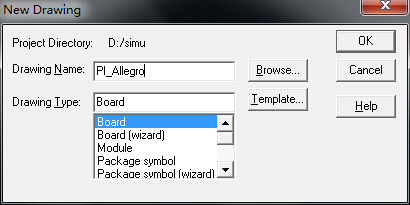

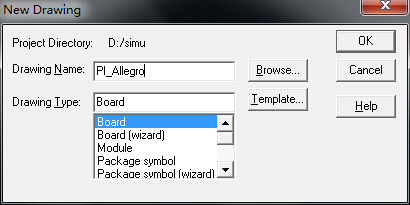

新建一个board,输入名字为PI_Allegro,设置英文路径。

2.启动电源完整性设置向导: 运行 Analyze ->Power Integrity

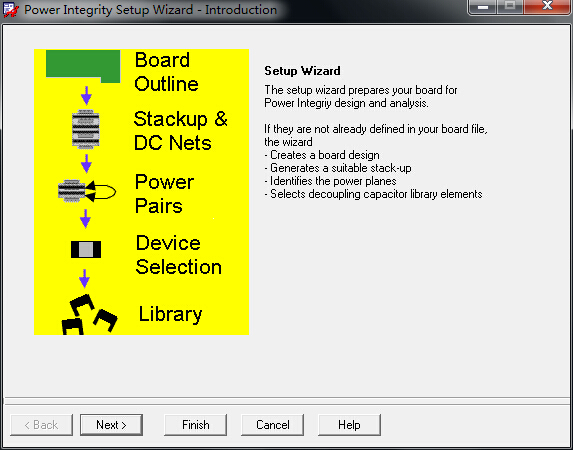

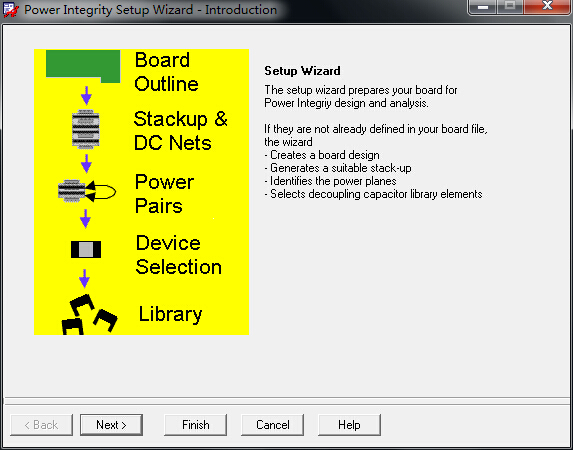

点击确定后,关闭SigNoise Errors/Warnings窗体,弹出电源完整性设置向导窗体

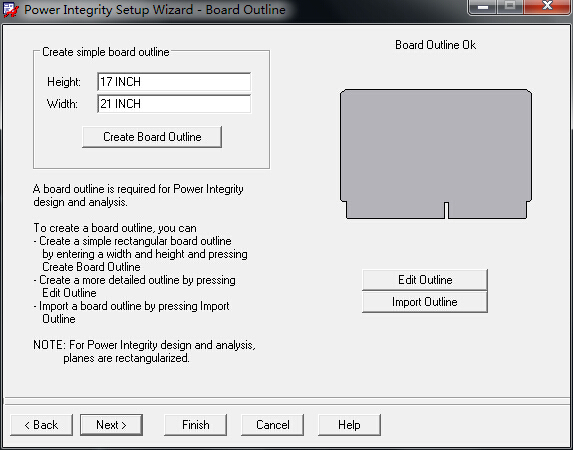

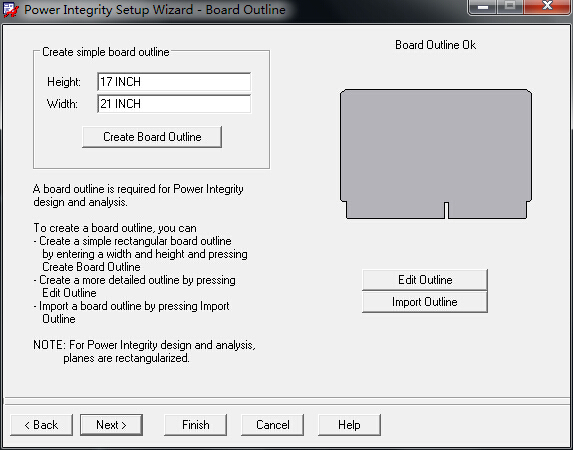

点击Next,接下来导入PCB边框,这样快一些,不用再动手去画,实例在资源里有。 点击Import Outline,选择资源里的lab2.brd。

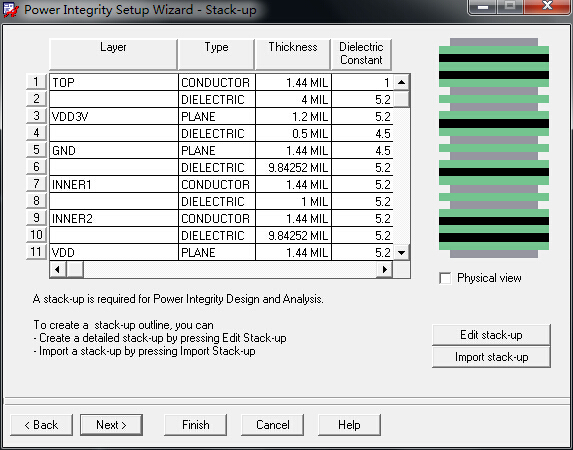

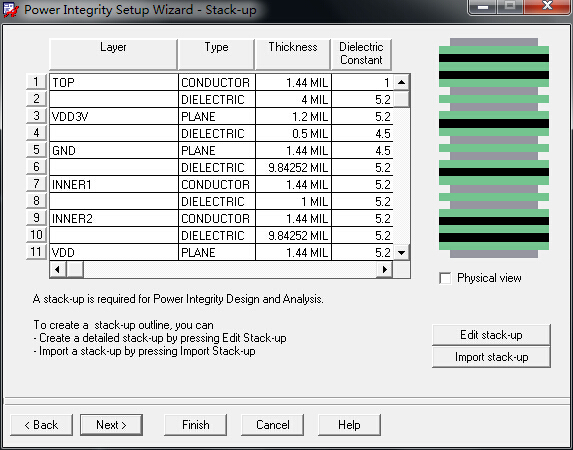

接着导入叠层结构,Next,点击Import stack-up,相同是选择lab2.brd。

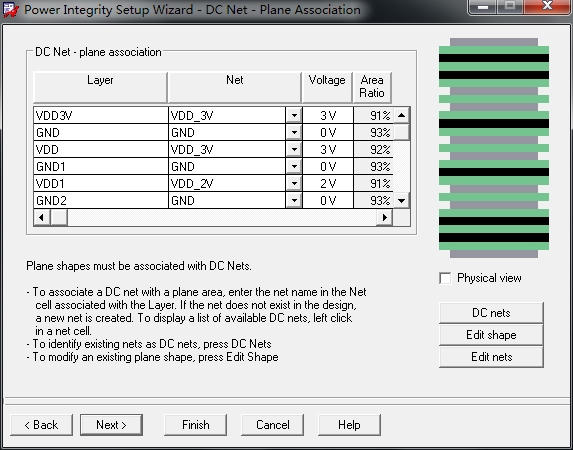

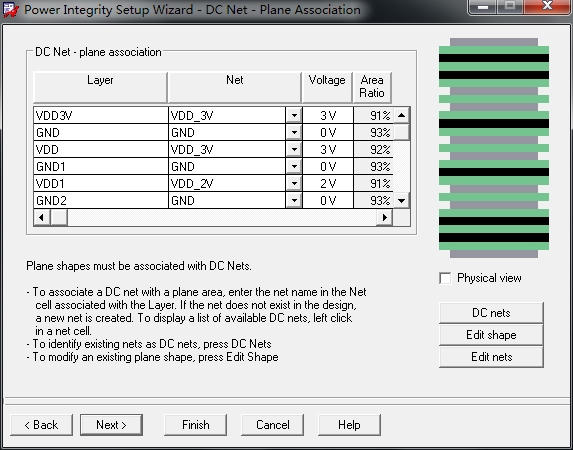

单击Next,进入直流网络和平面关联设置对话框,信息已经被导入,直接再单击Next

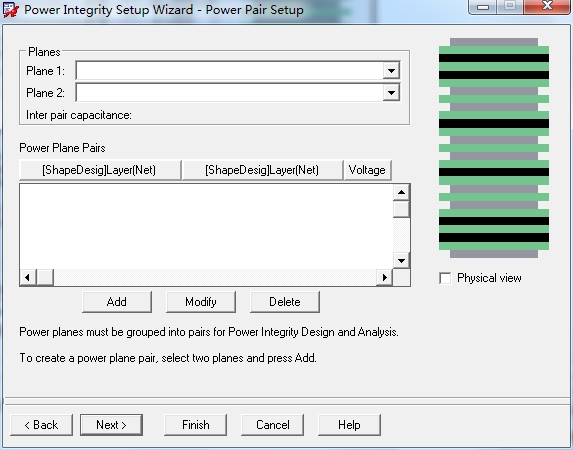

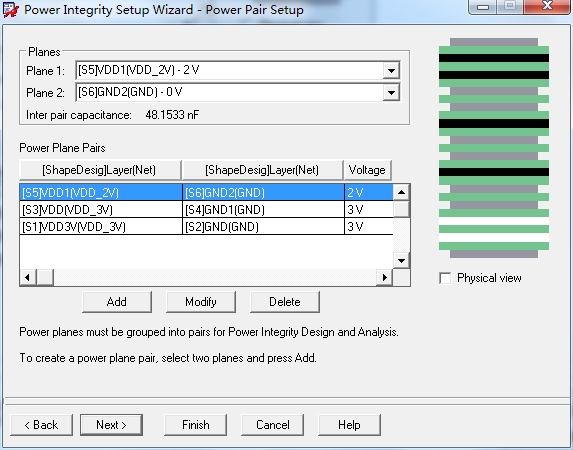

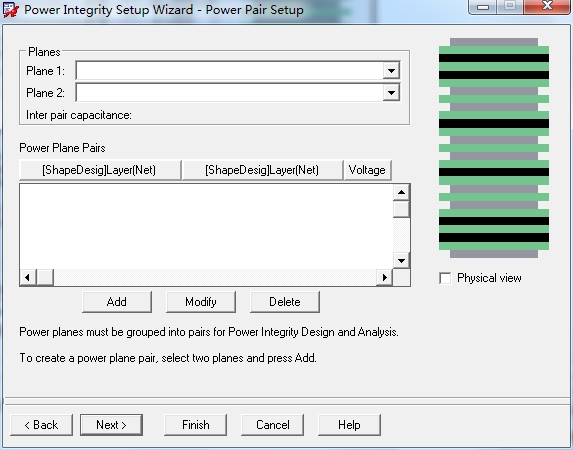

出现Power Pair Setup对话框,设置电源对

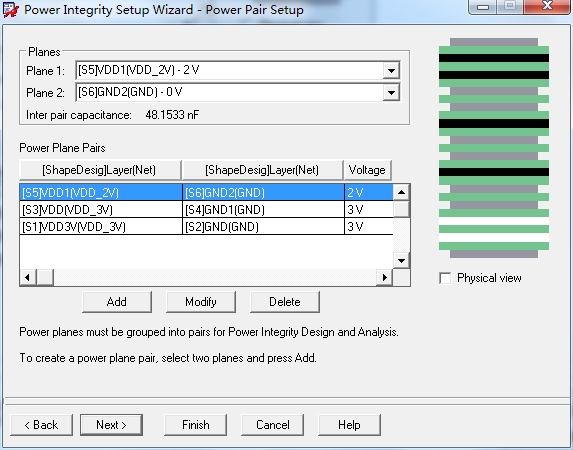

Plane1选择S1,Plane2选择S2,单击add,反复这个步骤 Plane1选择S3,Plane2选择S4,单击add

Plane1选择S5,Plane2选择S6,单击add

这就加入�了三个电源对,如图

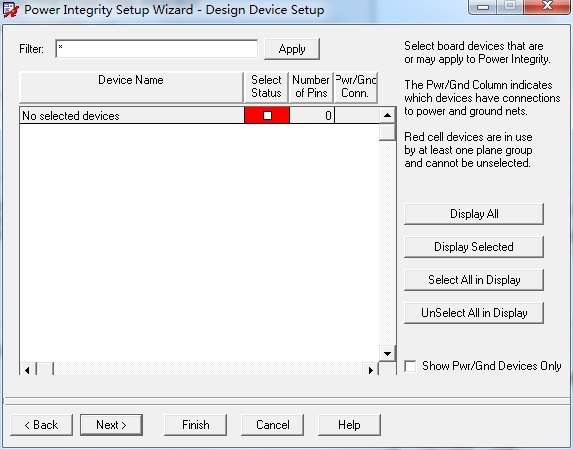

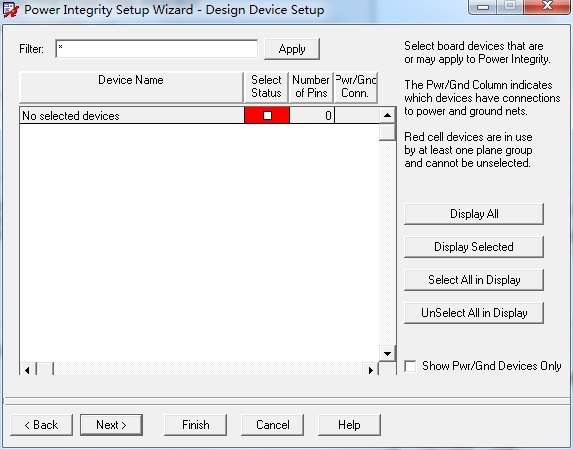

单击Next,这时候这个对话框没有显示不论什么元器件,由于这是个新的PCB,还没有安放元器件。

单击Next

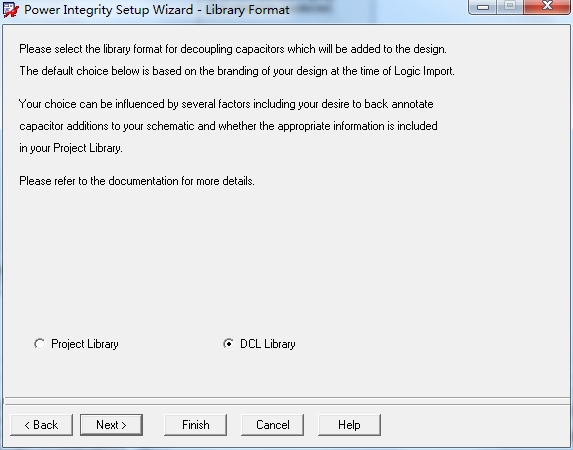

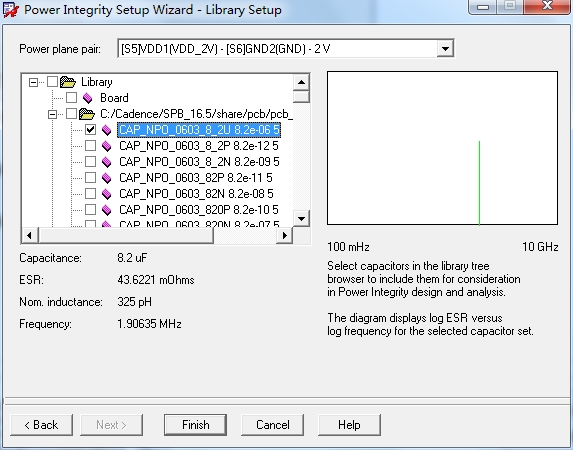

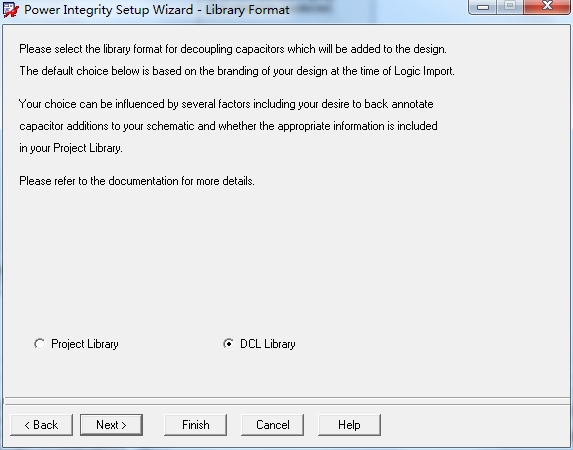

选中DCL library,再Next,进入Library Setup

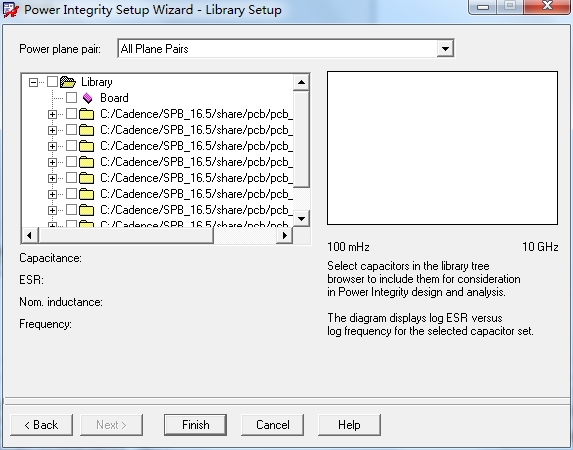

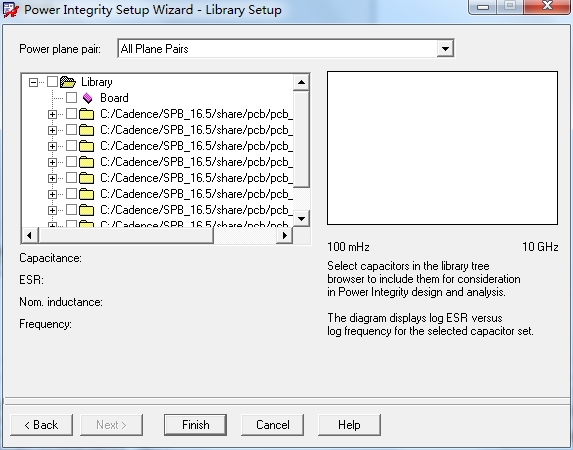

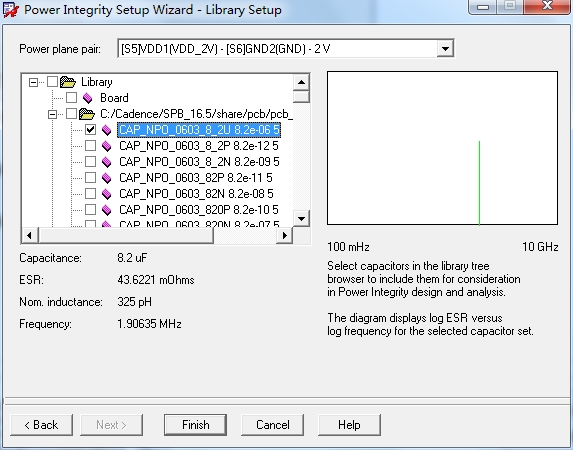

在Power plane pair选择S1-S2的平面对,单击电容库C:/Cadence/SPB_16.5/share/pcb/pcb_lib/npo_0603_caps 选择CAP_NPO_0603_10U 在Power plane pair选择S3-S4的平面对,单击电容库C:/Cadence/SPB_16.5/share/pcb/pcb_lib/npo_0603_caps 选择CAP_NPO_0603_6_8U 在Power plane pair选择S5-S6的平面对,单击电容库C:/Cadence/SPB_16.5/share/pcb/pcb_lib/npo_0603_caps 选择CAP_NPO_0603_8_2U

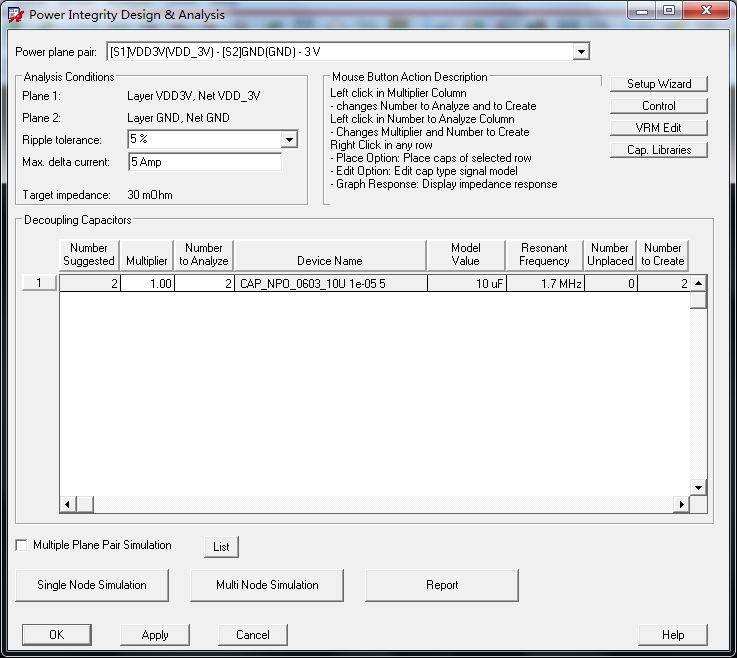

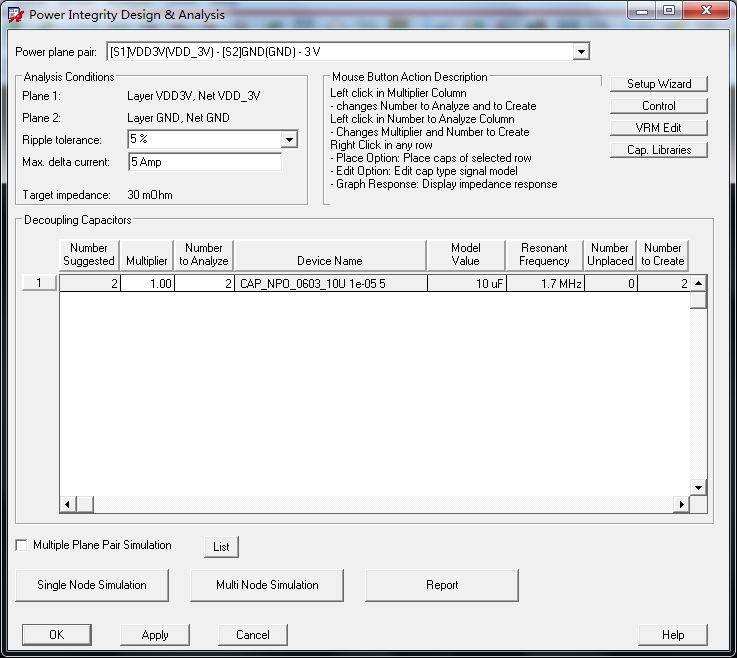

3.设置仿真參数 在Power Plane pair栏选择S1-S2,在Ripple tolerance波动容限栏选择5%,在Max delta current中输入5Amp,这时候对话框中显示当前的目标阻抗为30毫欧。 在Power Plane pair栏选择S3-S4,在Ripple tolerance波动容限栏选择5%,在Max delta current中输入5Amp,这时候对话框中显示当前的目标阻抗为30毫欧。 在Power Plane pair栏选择S5-S6,在Ripple tolerance波动容限栏选择5%,在Max delta current中输入5Amp,这时候对话框中显示当前的目标阻抗为20毫欧。

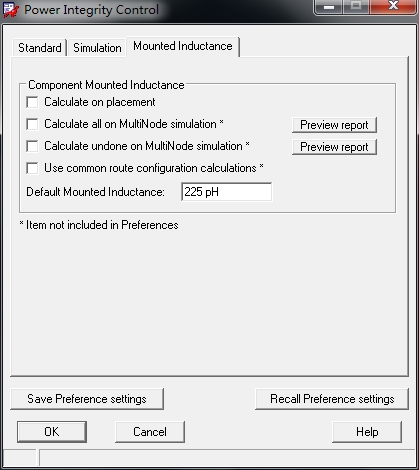

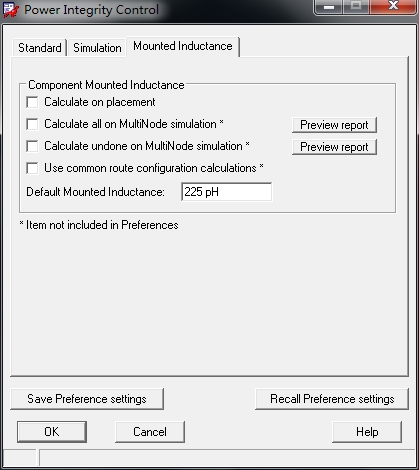

改变默认的贴装电感值,点击对话框中的Controlbutton,在Power Integrity Control中单击Mounted Inductance选项,在Default Mounted Inductance中输入225pH,点击OK。

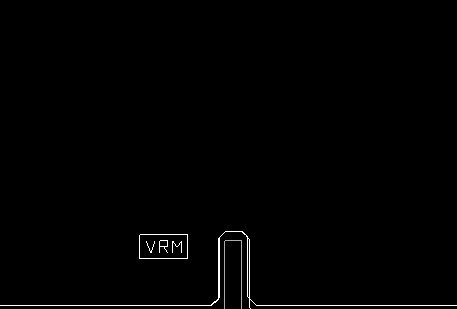

摆放电压调节模块,在要进行单节点仿真的每一个单独平面对上都须要放置一个电压调节模块。 选择S5-S6,点击VRM Edit,OK,摆放VRM

选择S3-S4,S1-S2,相同的步骤分别摆放VRM

4.单节点仿真 选择S1-S2,单击Single Node Simulation,出现SigWave窗体

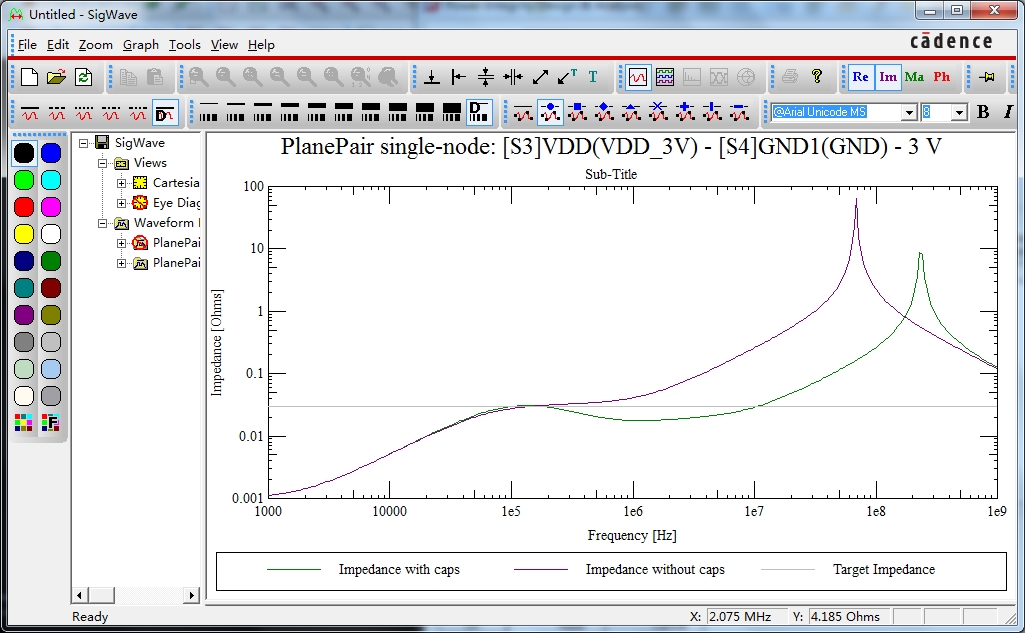

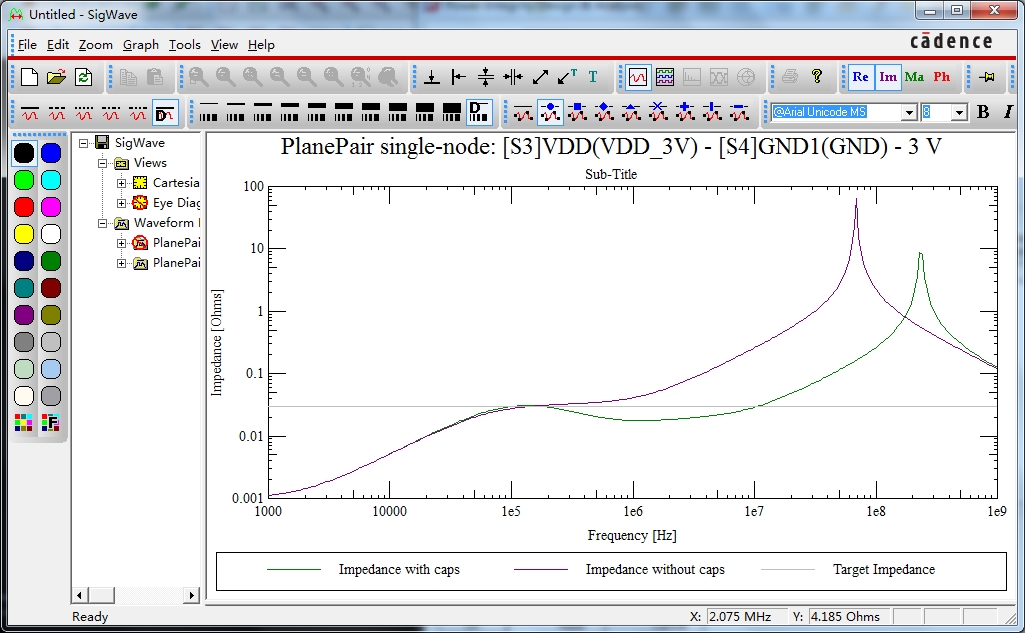

选择S3-S4,点击Single Node Simulation,显示:

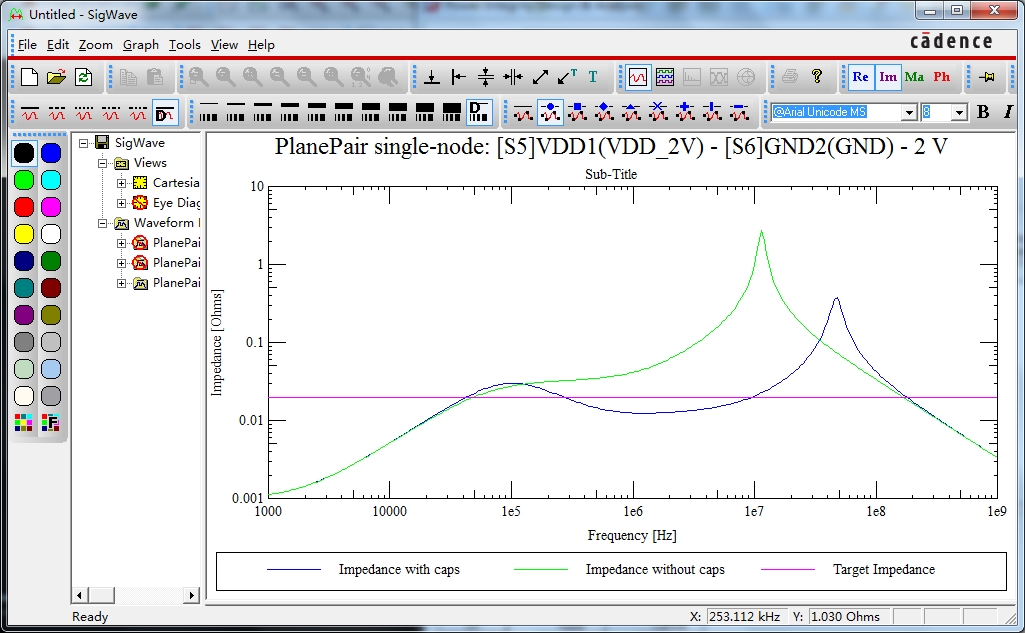

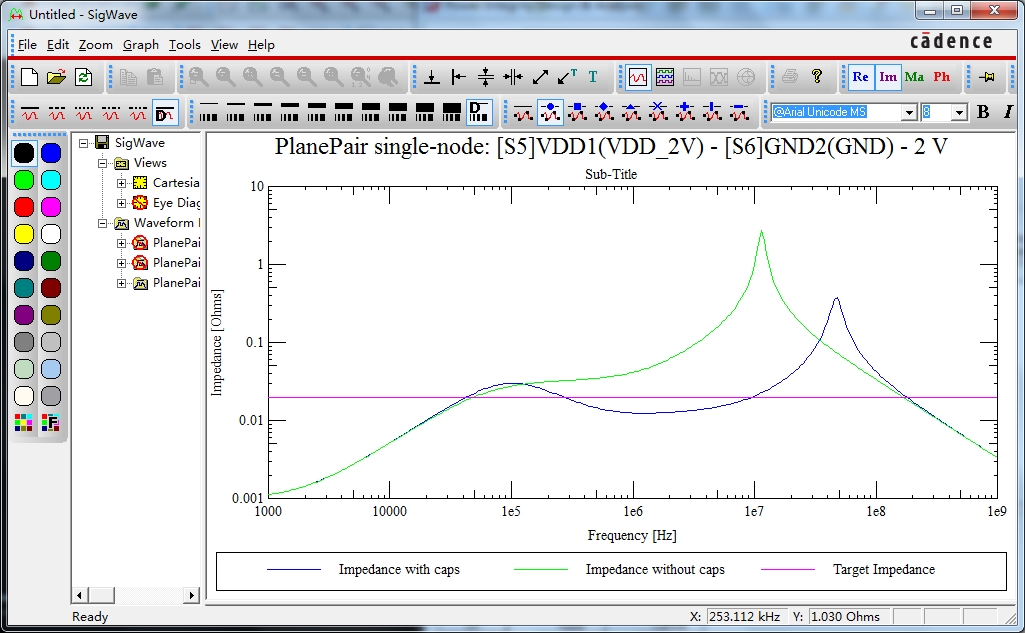

选择S5-S6,点击Single Node Simulation,显示:

分析这三个响应曲线,由于S3-S4平面对的平面间隔(23.32504mils)比S1-S2平面对的平面间隔0.5mils要大,平面间隔大的平面对会产生较小的电容,因此它有着更高的阻抗响应曲线。S1-S2的平面对响应曲线与S5-S6的很接近,这是由于两个平面对有着相近的区域和近乎相等的平面间电容值。含有电容器的阻抗响应曲线不同样的原因是由于之前为每一个平面对指定了不同大小的电容值,而这些电容有着不同的谐振频率值和不同的等效串联电阻值。

新建一个board,输入名字为PI_Allegro,设置英文路径。

2.启动电源完整性设置向导: 运行 Analyze ->Power Integrity

点击确定后,关闭SigNoise Errors/Warnings窗体,弹出电源完整性设置向导窗体

点击Next,接下来导入PCB边框,这样快一些,不用再动手去画,实例在资源里有。 点击Import Outline,选择资源里的lab2.brd。

接着导入叠层结构,Next,点击Import stack-up,相同是选择lab2.brd。

单击Next,进入直流网络和平面关联设置对话框,信息已经被导入,直接再单击Next

出现Power Pair Setup对话框,设置电源对

Plane1选择S1,Plane2选择S2,单击add,反复这个步骤 Plane1选择S3,Plane2选择S4,单击add

Plane1选择S5,Plane2选择S6,单击add

这就加入�了三个电源对,如图

单击Next,这时候这个对话框没有显示不论什么元器件,由于这是个新的PCB,还没有安放元器件。

单击Next

选中DCL library,再Next,进入Library Setup

在Power plane pair选择S1-S2的平面对,单击电容库C:/Cadence/SPB_16.5/share/pcb/pcb_lib/npo_0603_caps 选择CAP_NPO_0603_10U 在Power plane pair选择S3-S4的平面对,单击电容库C:/Cadence/SPB_16.5/share/pcb/pcb_lib/npo_0603_caps 选择CAP_NPO_0603_6_8U 在Power plane pair选择S5-S6的平面对,单击电容库C:/Cadence/SPB_16.5/share/pcb/pcb_lib/npo_0603_caps 选择CAP_NPO_0603_8_2U

3.设置仿真參数 在Power Plane pair栏选择S1-S2,在Ripple tolerance波动容限栏选择5%,在Max delta current中输入5Amp,这时候对话框中显示当前的目标阻抗为30毫欧。 在Power Plane pair栏选择S3-S4,在Ripple tolerance波动容限栏选择5%,在Max delta current中输入5Amp,这时候对话框中显示当前的目标阻抗为30毫欧。 在Power Plane pair栏选择S5-S6,在Ripple tolerance波动容限栏选择5%,在Max delta current中输入5Amp,这时候对话框中显示当前的目标阻抗为20毫欧。

改变默认的贴装电感值,点击对话框中的Controlbutton,在Power Integrity Control中单击Mounted Inductance选项,在Default Mounted Inductance中输入225pH,点击OK。

摆放电压调节模块,在要进行单节点仿真的每一个单独平面对上都须要放置一个电压调节模块。 选择S5-S6,点击VRM Edit,OK,摆放VRM

选择S3-S4,S1-S2,相同的步骤分别摆放VRM

4.单节点仿真 选择S1-S2,单击Single Node Simulation,出现SigWave窗体

选择S3-S4,点击Single Node Simulation,显示:

选择S5-S6,点击Single Node Simulation,显示:

分析这三个响应曲线,由于S3-S4平面对的平面间隔(23.32504mils)比S1-S2平面对的平面间隔0.5mils要大,平面间隔大的平面对会产生较小的电容,因此它有着更高的阻抗响应曲线。S1-S2的平面对响应曲线与S5-S6的很接近,这是由于两个平面对有着相近的区域和近乎相等的平面间电容值。含有电容器的阻抗响应曲线不同样的原因是由于之前为每一个平面对指定了不同大小的电容值,而这些电容有着不同的谐振频率值和不同的等效串联电阻值。