目录 0. 摘要: 1. DDR2布线中面临的困难 1.1 DDR与CPU之间的布局[1] 1.2 如何设置Width(信号线宽)和Clearance(安全间距)? 1.3 网络分类与差分线的设置 1.4 如何确定小T点与大T点的位置? 1.5 BGA自动扇出与手动优化 1.6 如何控制等长误差 2. DDR2等长布线 2.1 区域规则ROOM讲解 2.2 区域规则设置 2.3 过孔、网络CLASS及差分线的设置 2.4 小T点设置 2.5 大T点设置 2.6 CPU自动扇出 2.7 数据互联 2.8 地址线T点互连 2.9 寻找等长目标 2.10 走等长线 2.11 等长输出 3. 个人思考 3.1 为何同一根信号线在不同区域(CPU_ROOM、DDR2_ROOM、其它)的线宽会不一样? 3.2 如何最大化利用好布线空间,同时减小信号线间的串扰? 3.3 相同模块之间的复用 4. 尾巴: 5. PCB工程下载地址 6. 参考:

0. 摘要:

本文首先列出了DDR2布线中面临的困难,接着系统的讲述了DDR2电路板设计的具体方法,最后给出个人对本次电路设计的一些思考。本次设计中CPU的封装为BGA844-SOC-Y,DDR2的封装为FBGA84,DDR2的控制总线采用星形连接,使用的PCB软件为AltiumDesigner10,参考设计教程为《Altium Designer DDR2设计教学视频》[1]!1. DDR2布线中面临的困难

1.1 DDR与CPU之间的布局[1]

(1)DDR2:内存与CPU的边缘间距建议5~8mm; (2)DDR3:排阻自身长度为2mm,排阻与CPU边缘间距建议3mm,排阻与内存边缘间距建议3mm。1.2 如何设置Width(信号线宽)和Clearance(安全间距)?

在封装BGA844-SOC-Y中,焊盘的直径为18.9mil,焊盘间距为39.37mil,两个焊盘之间的间隔为20.47mil,要想从BGA中引出所有的信号线,必须合理的设置Width和Clearance等规则。

1.3 网络分类与差分线的设置

在《DDR2信号分类及等长设计》[3]一文中,DDR2可以分为以下三类:(1)差分时钟信号:CLK_N,CLK_P;

(2)数据线DQ0~DQ15,数据掩码信号DQM0,DQM1,数据选通信号DQS*_N,DQS*_P;

(3)地址线/控制线:除数据,时钟外的其他信号,如A0~A12,WE,CS,BA0~2,CKE等;

可以设置为以下几个class规则:

(1)DATA_L_BUS:Q0~DQ7,DQM0,DQS0_N,DQS0_P;

(2)DATA_H_BUS:Q8~DQ15,DQM1,DQS1_N,DQS1_P;

(3)ADDR_BUS:除数据线外的其他信号;

(4)CLK_DIFF: CLK_N,CLK_P;

1.4 如何确定小T点与大T点的位置?

如图4所示,小T点对应于DDR2焊盘扇出后的过孔C与D,C与D点扇出的走线方式必须保持一致。大T点对应于地址/命令总线的分支点过孔B,在DDR做等长布线时,地址/命令总线Net-Class(网络类)每条网络满足: (1)AB+BC=AB+BD; (2)每条网络的总长度(AB+BC+BD)均相等。 为了降低DDR等长布线的难度,通常将大T点设在C与D的对称轴上,假如大T点没有落在C与D的中轴线上,该怎么办? 在《用Altium Designer实现DDR2的等长布线》[4]和《Altium Designer 中 DDRII SDRAM 的等长布线》[5]中给出了解决办法,文中使用了AD里面的From-To Editor 网络编辑器,将同一个网络在T点处划分为3个部分,然后通过设置焊盘到焊盘之间的等长来实现DDR的等长布线,有兴趣的读者可以查看原文!

1.5 BGA自动扇出与手动优化

在使用AD10给BGA自动扇出时,需要注意一下几点: (1)在执行自动扇出前,BGA上的所有焊盘均不能连线,否则自动扇出无法完成! (2)FBGA84封装的DDR2在进行自动扇出时,扇出的效果非常差,必须使用手工扇出。 对CPU和DDR2进行自动扇出,可分别得到图5和图6所示所示结果。

1.6 如何控制等长误差

在《DDR2信号分类及等长设计》[3]一文中,等长误差如下设置: (1)所有信号线参考差分时钟的长度作等长;(2)DATA_L_BUS共11根走在同层,与差分时钟的长度误差25mil;

(3)DATA_H_BUS共11根走在同层,与差分时钟的长度误差25mil;

(4)ADDR_BUS:与差分时钟的长度误差200~300mil; 在视频《Altium Designer DDR2设计教学视频》中,作者给出了如下的等长误差,记地址/控制网络类(包括差分时钟)的等长目标为L1,数据网络类等长目标为L2,则: (1)在地址/控制网络类中,差分时钟长度设为L1,其它等长误差控制在L1±200mil之内; (2)数据网络类等长误差控制在L2±25mil之内,同一组之间作等长即可; (3)L1与L2满足:0<L1-L2<1000mil!

2. DDR2等长布线

2.1 区域规则ROOM讲解

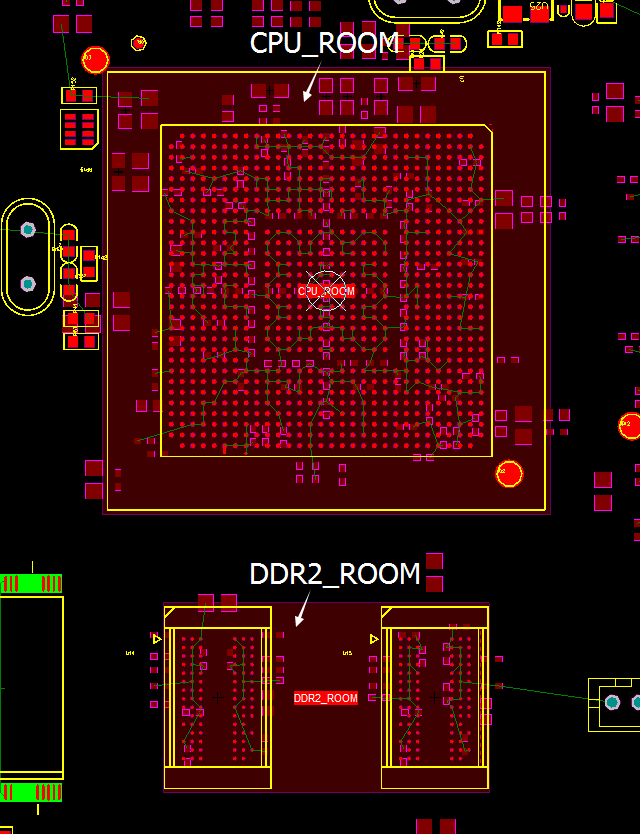

Q:如何放置ROOM? 执行Design→Rooms→Place Rectangular Room,给CPU和DDR2添加ROOM,添加后将ROOM名称分别修改为“CPU_ROOM”、“DDR2_ROOM”,如图7所示。

2.2 区域规则设置

(1)如何设置规则? 执行Design→Rules...即可进入规则编辑菜单。 (2)如何定义ROOM内的规则? 进入规则编辑器后,首先点击需要编辑的规则并右击新建“new rule...”,接着先点击新键的规则,然后在“Where The First Object Matches”一栏选择“Advanced(Query)”,在“Full Query”一栏填入“withinroom('name_ROOM')”,最后Apply并单击OK即可! 上面的name_ROOM为ROOM的名称,输入语法时请切换为英文输入法,如果需要同时给多个ROOM定义规则,其语法为:withinroom('name_ROOM')&withinroom('name1_ROOM')&withinroom('name2_ROOM')。 (3)如何给PCB定义规则? 为了引出BGA内部走线,规则中的Clearance和Width进行如下设置: Clearance设置方案(优先级从下到上依次递增): Clearance_CPU : 4 mil withinroom('CPU_ROOM') Clearance_DDR2 : 4.4 mil withinroom('DDR2_ROOM') Clearance : 5 mil Width(最小 / 推荐 / 最大)设置方案(优先级从下到上依次递增): Width_PWR : 12 / 12 / 120 mil Width_CPU : 4 / 4 / 4 mil withinroom('CPU_ROOM') Width_DDR2 : 4.4 / 4.4 / 4.4 mil withinroom('DDR2_ROOM') Width : 5 / 5 / 5 mil 说明:Width_PWR为电源网络的线宽规则!2.3 过孔、网络CLASS及差分线的设置

(1)如何给PCB定义Via(过孔)的规则? Via(内径 / 外径)设置方案(优先级从下到上依次递增): RoutingVias_DDR2 : 8 / 16 mil withinroom('DDR2_ROOM') RoutingVias : 10 / 22 mil (2)如何设置网络Class DDR2的所有网络,可以分为以下3类: 电源地信号,数据信号,时钟、地址、控制类信号。 执行Design→ Classes...,调出类设置界面,按下方的规则对网络进行分类: 网络类 包含子网络 POWER_CLASS GND、VREF、VCC1V8、VTT DATA_CLASS Data0-7:DRAM0_D0~7、DRAM0_DM0、DRAM0_DQS0_N、DRAM0_DQS0_P; Data8-15:DRAM0_D8~15、DRAM0_DM1、DRAM0_DQS1_N、DRAM0_DQS1_P; Data16-23:DRAM0_D16~23、DRAM0_DM2、DRAM0_DQS2_N、DRAM0_DQS2_P; Data24-31:DRAM0_D24~31、DRAM0_DM3、DRAM0_DQS3_N、DRAM0_DQS3_P; ADD_CLASS DRAM0_A0~13、DRAM0_BA0~2、DRAM0_CAS#、DRAM0_CLKE、DRAM0_CLK_N、DRAM0_CLK_P、DRAM0_CS#、DRAM0_ODT、DRAM0_RAS#、DRAM0_WE# 网络归类后效果如图8所示。

2.4 小T点设置

DDR2手动扇出效果图如图10所示,封装中心处的过孔对应为小T点,两个小T点的中点对应大T点所在的位置。 完成小T点的设置主要分为以下几步: (1) 对左侧的DDR2进行手动扇出; (2)全选DDR2扇出的走线和过孔,对已选对象进行复制并以左上第一个焊盘作为参考点; (3) 将所选对象复制到右侧DDR2上,十字光标对准左上第一个焊盘! 以上操作也可称作走线与过孔的复用!

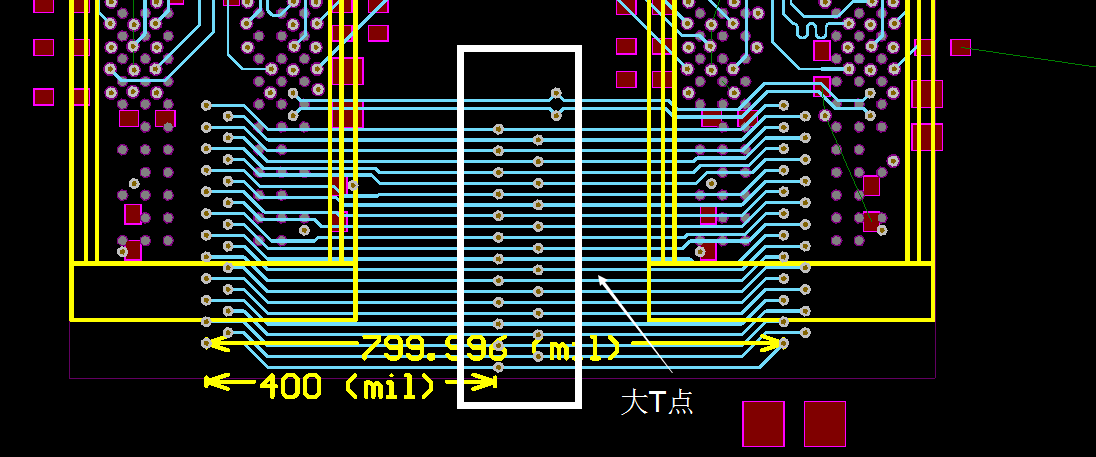

2.5 大T点设置

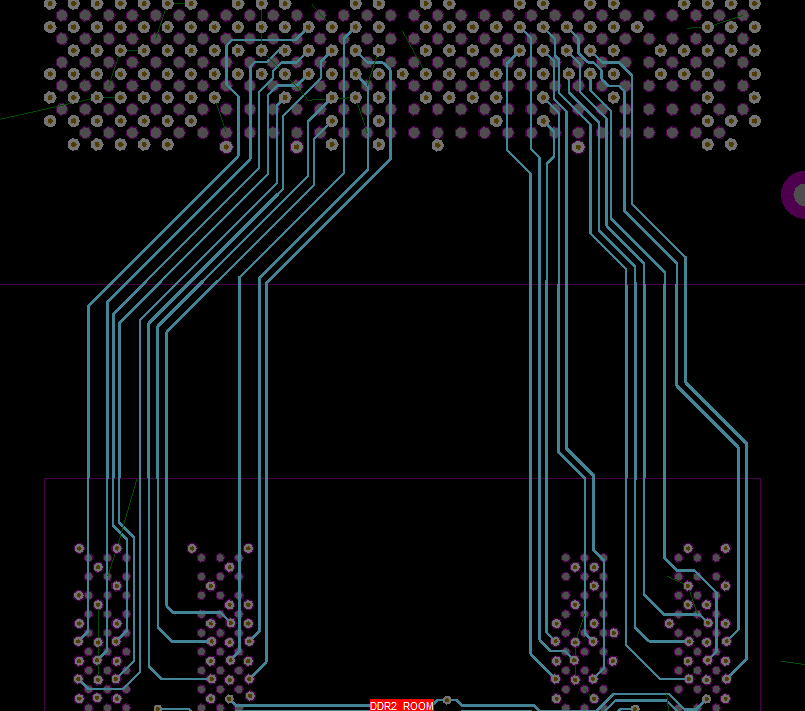

将图10的小T点依次连接,并在两个小T点的中心打上过孔(即大T点),完成后效果如图11所示。在连线时请注意以下细节: (1)大T点的位置是允许一定的误差的,不需要绝对的中心! (2) 绕线时需要优化电源过孔的布局; (3)小T点(过孔)之间的水平与垂直间距需要保持在30mil以上! (4)大T点与小T点放置完后,请进行上锁设置,防止误删!

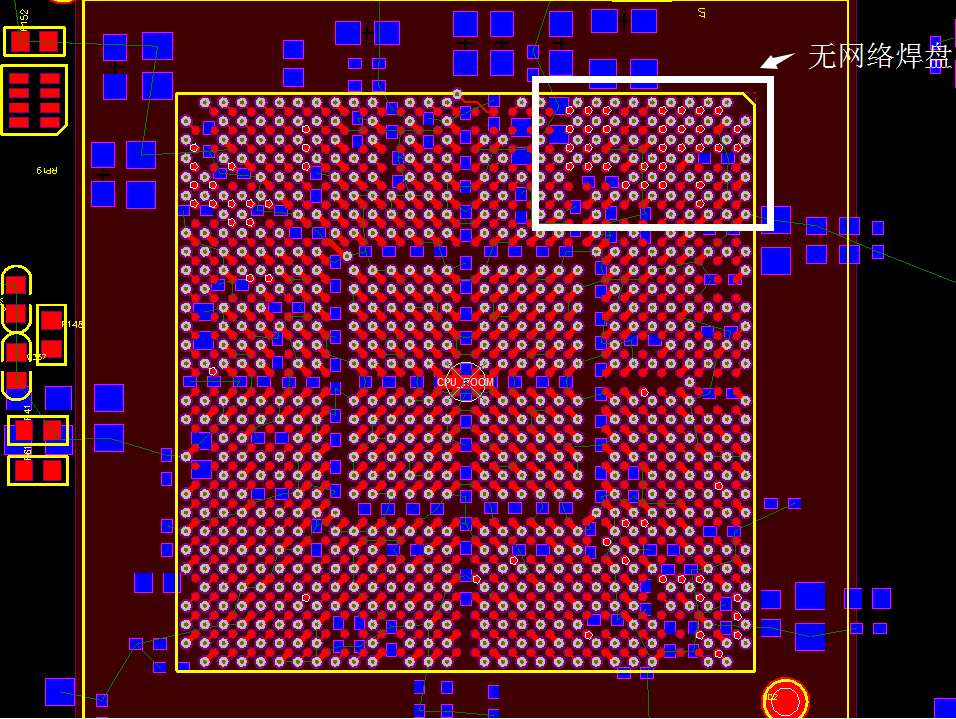

2.6 CPU自动扇出

执行Auto Route→Fanout→Component,点击CPU封装即可完成CPU的自动扇出,扇出效果如图12所示。由于规则的设置,电源类管脚扇出线宽为12mil,信号管脚扇出线宽为4mil,下图中打白 {MOD}圆圈的管脚为无网络的焊盘。

2.7 数据互联

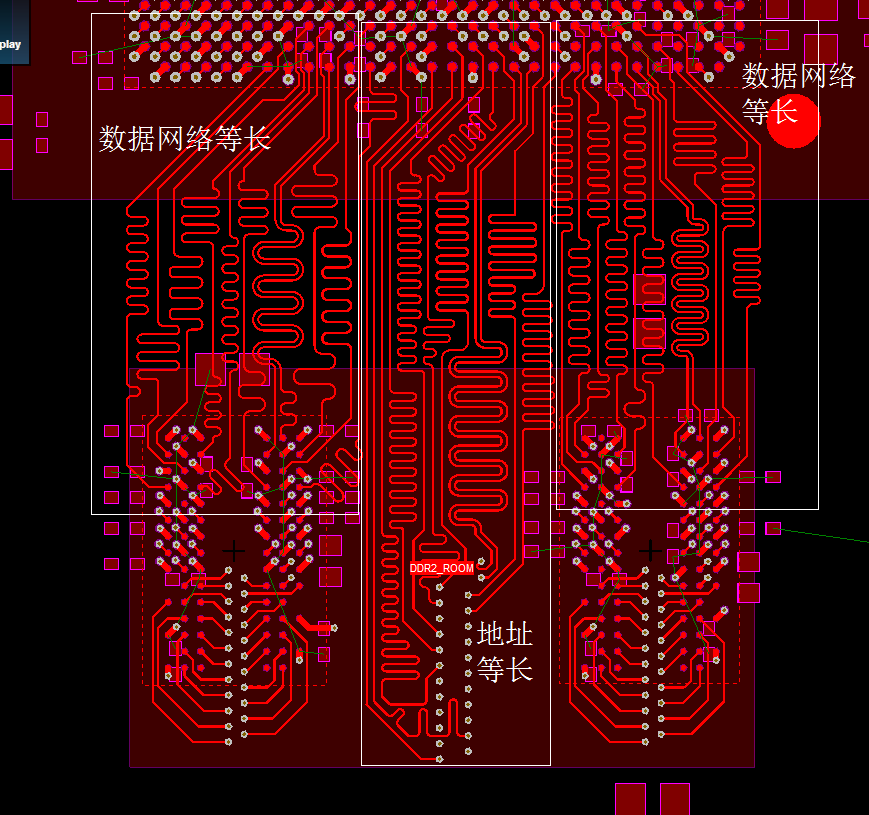

数据类总线分为两部分互连,一部分走顶层,另一部分走L3层!如图13所示,为数据网络类DATA0-[D8-15]和DATA0-[D24-31]在顶层的连线效果图。

2.8 地址线T点互连

地址与控制类总线分为两部分互连,一部分走顶层如图15所示,另一部分走底层如图16所示。

2.9 寻找等长目标

如图16所示,为地址类网络长度分布,根据网络长度分布,选择3000mil作为地址类网络的等长目标,等长误差控制在±200mil以内。根据作者描述,地址类与数据类网络长度差应小于1000mil,所以将数据类网络等长目标控制在2000mil,数据类网络之间的等长误差控制在±25mil以内。2.10 走等长线

(1) 如何走等长线? 普通信号线,按快捷键T+R,差分线按T+I,进入等长布线状态。等长布线时,W键上方的1、2、3、4依次对应拐角弧度减小、拐角弧度增大、蛇形线间距减小、蛇形线间距增大等功能! (2)地址类等长 顶层: