分享一下我老师大神的人工智能教程!零基础,通俗易懂!http://blog.csdn.net/jiangjunshow也欢迎大家转载本篇文章。分享知识,造福人民,实现我们中华民族伟大复兴! 作者:sate210设计团队硬件工程师 整理:gooogleman 时间:2011.10.226. Sate210 PCB设计说明6.1 Sate210 核心板PCB 层叠结构Sate210采用8层板设计,板厚1.2mm。Sate210最高运行频率1GHz,内存总线带宽频率是DDR400MHz所以PCB设计要严格遵守信号完整性与电源完整性设计原则。首先是层叠结构设计,PCB层叠需要考虑多个因素,层叠结构的选择首要考虑的是信号完整性及电源完整性的问题,此外还要考虑工艺及成本等。好的层叠结构不仅让信号失真最小,也能使系统更稳定以及减小EMI。层叠结构的确定可以从下面几个原则出发:l 每个信号层都有参考层,并且靠近参考层l 避免两个信号层直接相邻l 主电源层应靠近地层l 兼顾对称的层压结构基于以上几点考虑,Sate210采用很完美的层叠结构,Sate210的层叠结构如下图  其中L3和L6是内部信号走线层,L2和L5是GND平面,L4是主电源层,L7是副电源层。为了核心板能运行稳定并且EMI要尽量小要对关键走线进行阻抗控制,一般单端走线的阻抗为50Ω,差分走线为100Ω,控制三星S5pv210的PCB设计指导手册单端阻抗从45Ω-55Ω都可以,但是要保证每一层的阻抗变化不大。下面是Sate210的阻抗控制表:

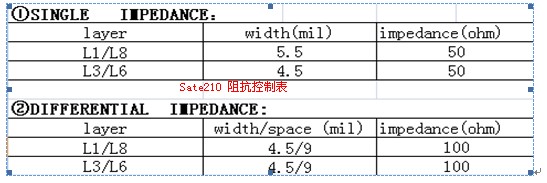

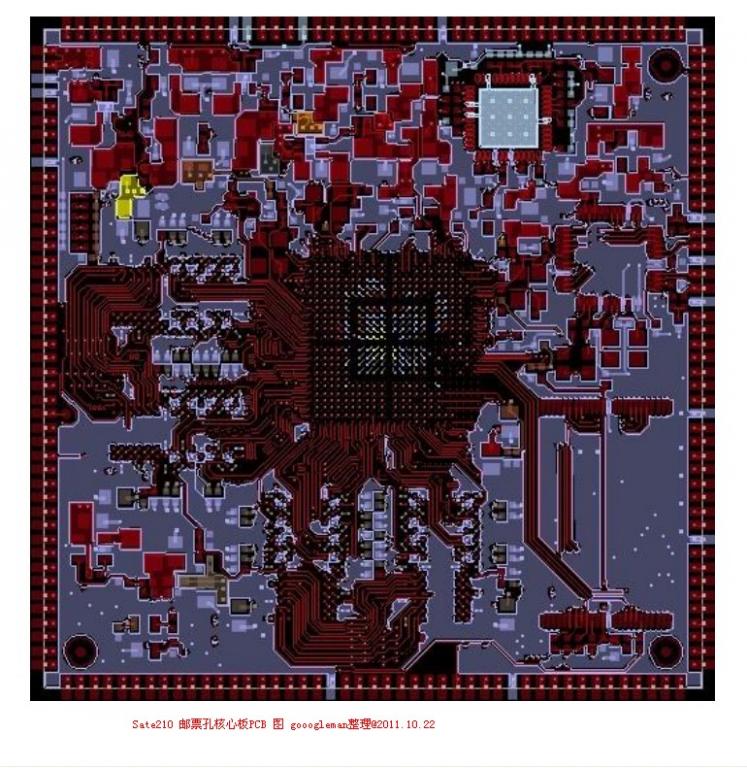

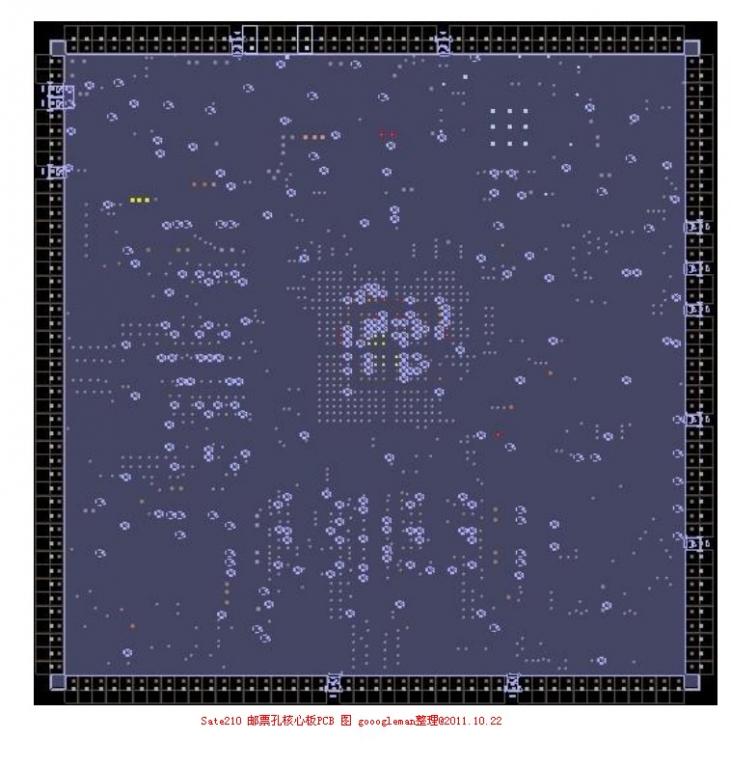

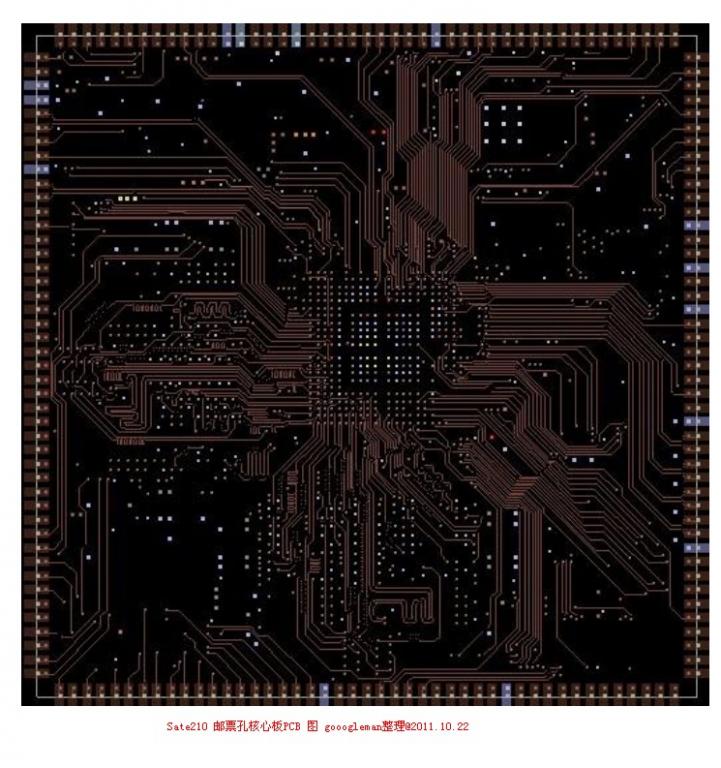

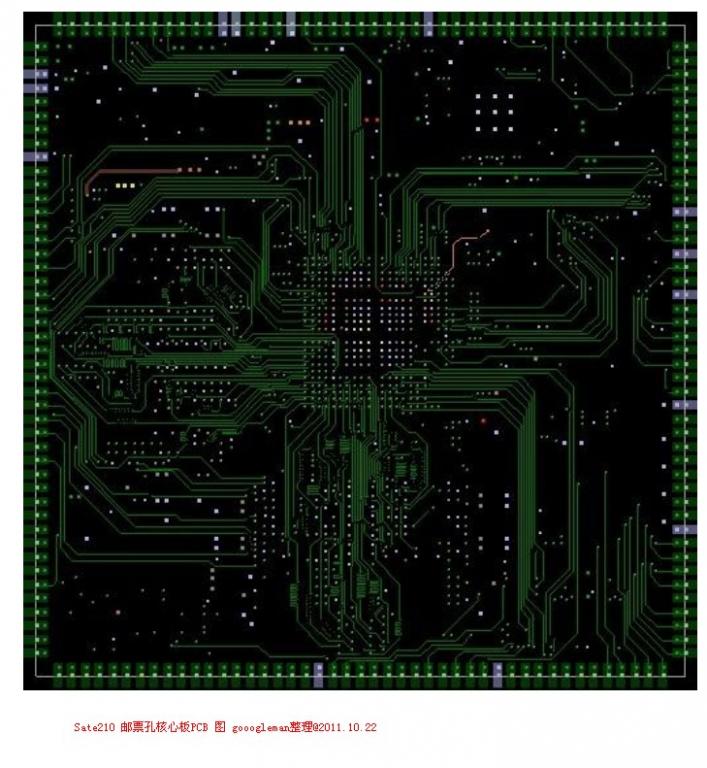

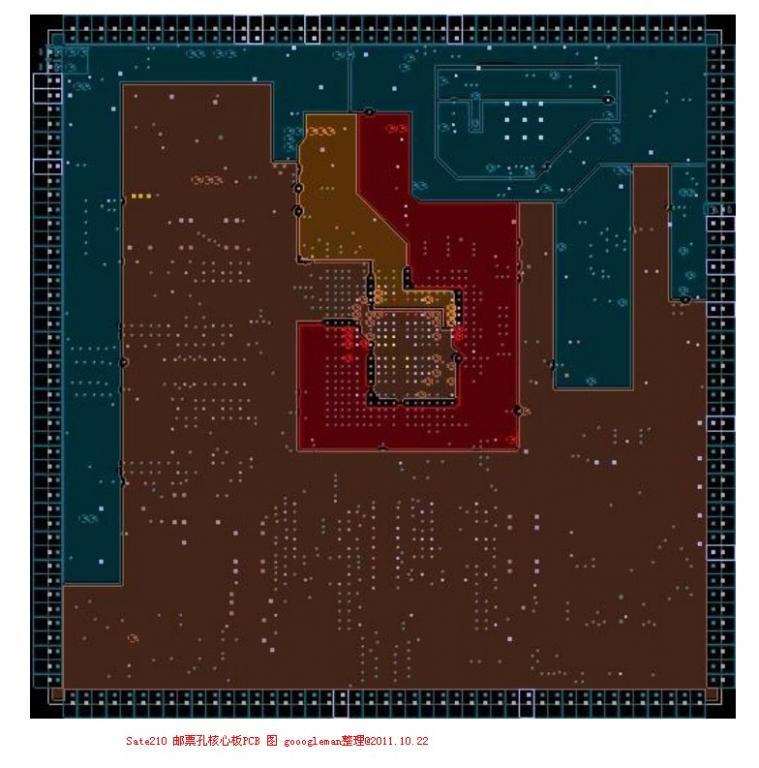

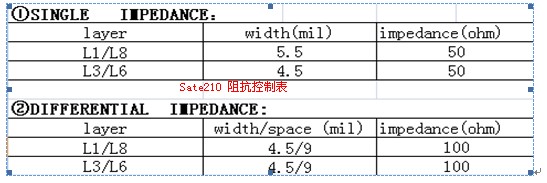

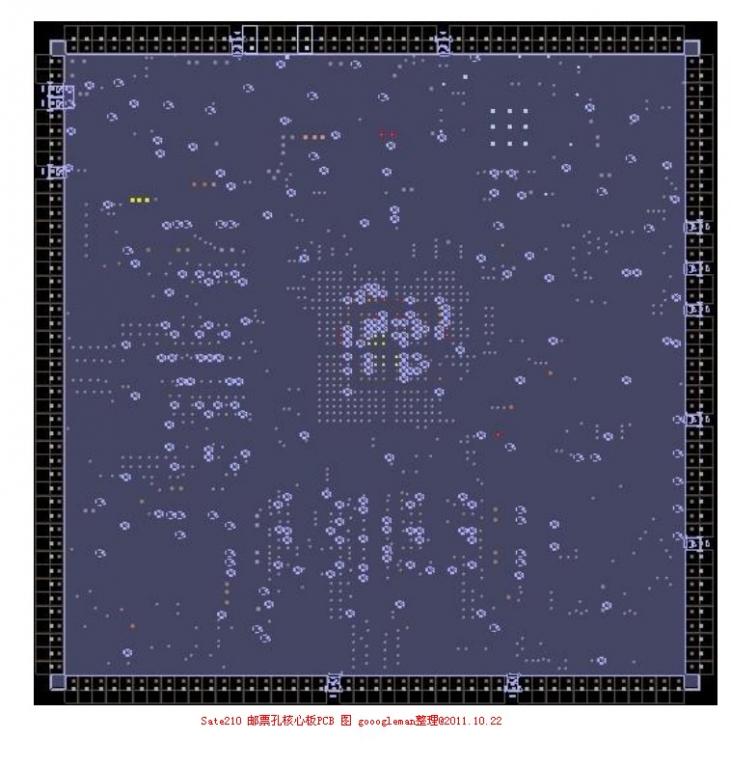

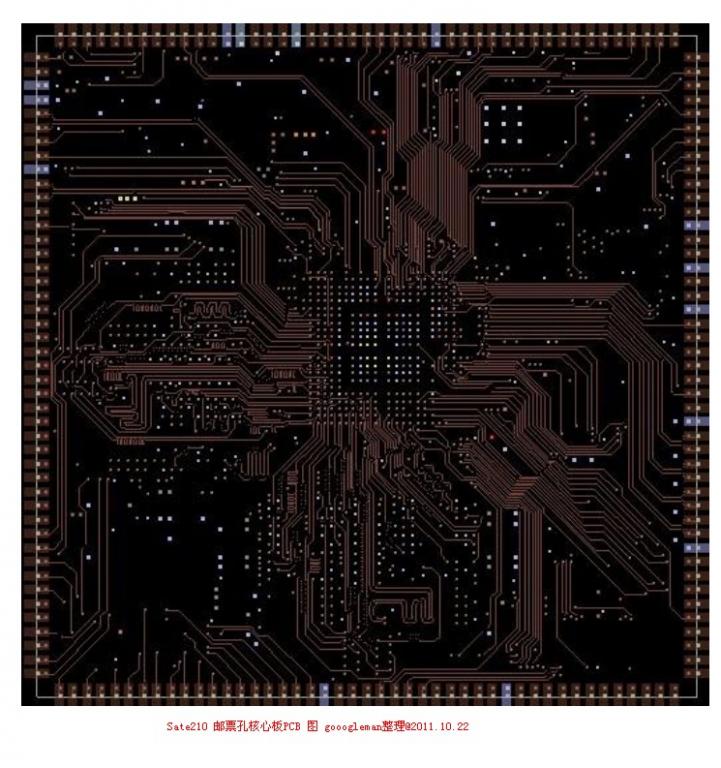

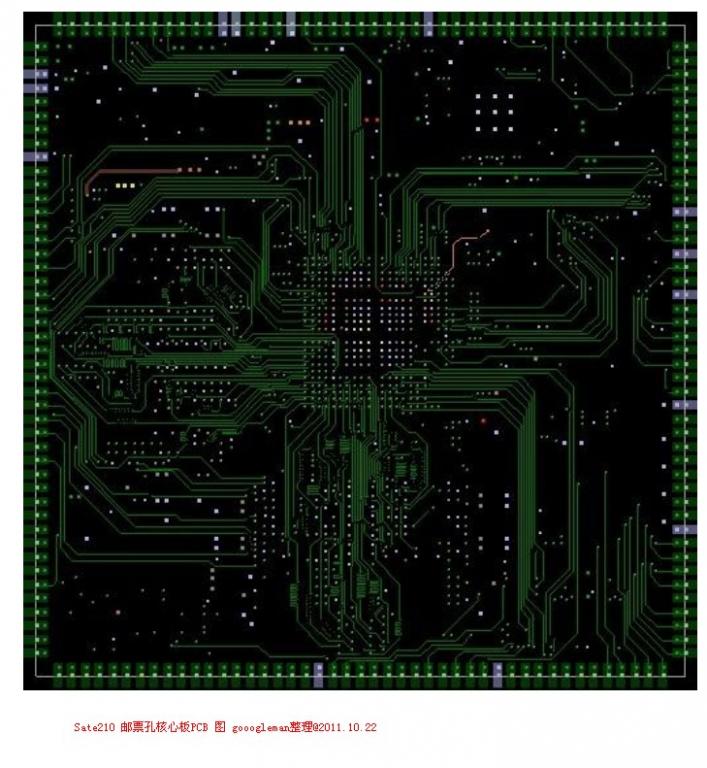

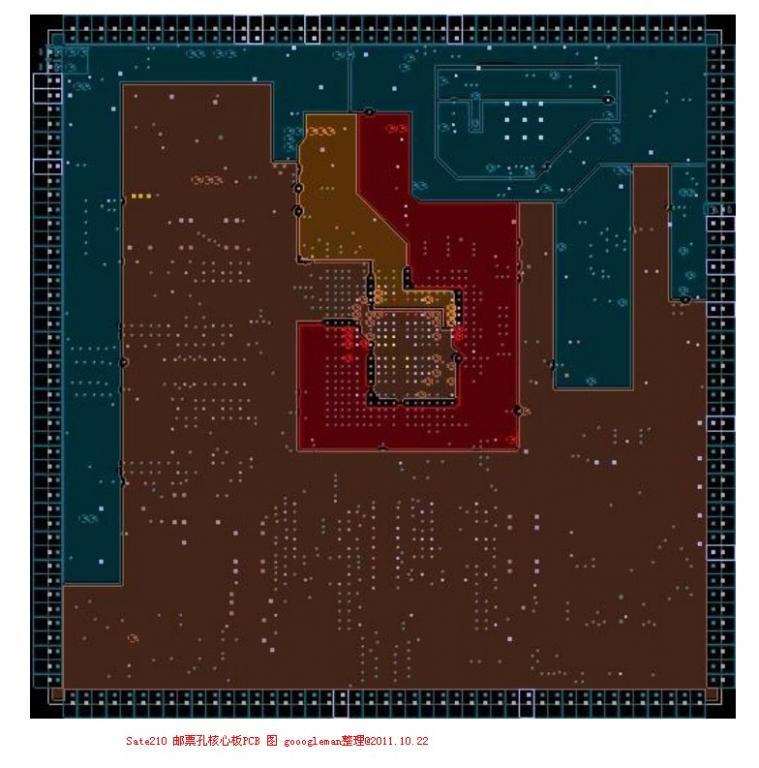

其中L3和L6是内部信号走线层,L2和L5是GND平面,L4是主电源层,L7是副电源层。为了核心板能运行稳定并且EMI要尽量小要对关键走线进行阻抗控制,一般单端走线的阻抗为50Ω,差分走线为100Ω,控制三星S5pv210的PCB设计指导手册单端阻抗从45Ω-55Ω都可以,但是要保证每一层的阻抗变化不大。下面是Sate210的阻抗控制表: 顶层和底层的单端走线线宽是5.5mil,差分线宽是4.5mil间距9mil,内部走线层端走线线宽是4.5mil,差分线宽是4.5mil间距9mil。除了阻抗控制还要对走线长度控制,控制走线长度目的是为了满足信号时延的要求,通常说就是走蛇形线。暂停一下,更加详细的Sate210 硬件设计说明请参照《Sate210硬件用户手册V1.2》,这个文档有60 多页,我已经上传到CSDN,有兴趣的人请去看看。《Sate210硬件用户手册V1.2》下载地址是:http://download.csdn.net/detail/gooogleman/3706515 6.2 Sate210 DDR 走线设计按照三星210的PCB设计指导手册,DDR部分的走线有以下要求:l 所有信号的容性负载为15pF@200MHz, 1.8V。所以所有的电容包括电路板的寄生电容要小于15PFl 走线阻抗控制为45Ω-55Ωl 走线分支尽量短l 最长走线长度45mml 信号走线必需有参考层(GND或PWR平面)l 走线尽量在内层l 尽量加强电源走线,去耦电容紧靠电源脚l DRAM芯片每个电源网络至少两个去耦电容l 使用完整的地平面和电源平面为信号提供参考面 6.2.1 Xm1DQS and Xm1DATA, Xm1DQM信号Xm1DQS0 & Xm1DATA[7:0], Xm1DQM0一组,Xm1DQS1 & Xm1DATA[15:8], Xm1DQM1一组,Xm1DQS2 & Xm1DATA[23:16], Xm1DQM2一组,Xm1DQS3 & Xm1DATA[31:24], Xm1DQM3一组,每组之间布线长度偏差± 5.0mm。如果是DDR2内存偏差为± 1.0mm。 6.2.2 Xm1SCLK and Xm1SCLKn信号l 推荐使用星形拓扑l 推荐差分阻抗为100Ωl Xm1SCLK & Xm1SCLKn布线长度偏差±1.0mml Xm1SCLK(n) & Xm1DQS[3:0] 布线长度偏差± 10mm 6.2.3其它控制信号 l Xm1SCLK(n) & Xm1ADDR[15:0], Xm1CASn, Xm1RASn, Xm1CKE[1:0], Xm1WEn布线长度偏差± 10mm;l 地址信号(Xm1CKE[1:0], Xm1CSn[1:0], Xm1ADDR[15:0], Xm1RASn, Xm1CASn, Xm1WEn)推荐使用T形拓扑;l 不要靠近高速信号(Xm1SCLK, Xm1SCLKn, Xm1DQS(n)[3:0] and Xm1DATA),与其保持至少3W线距;l 直接连接Xm1GATEI (pin B10)到Xm1GATEO (pin C10)。l Xm0与Xm1的要求是一样的。 6.3 Sate210核心板PCB图(供参考)

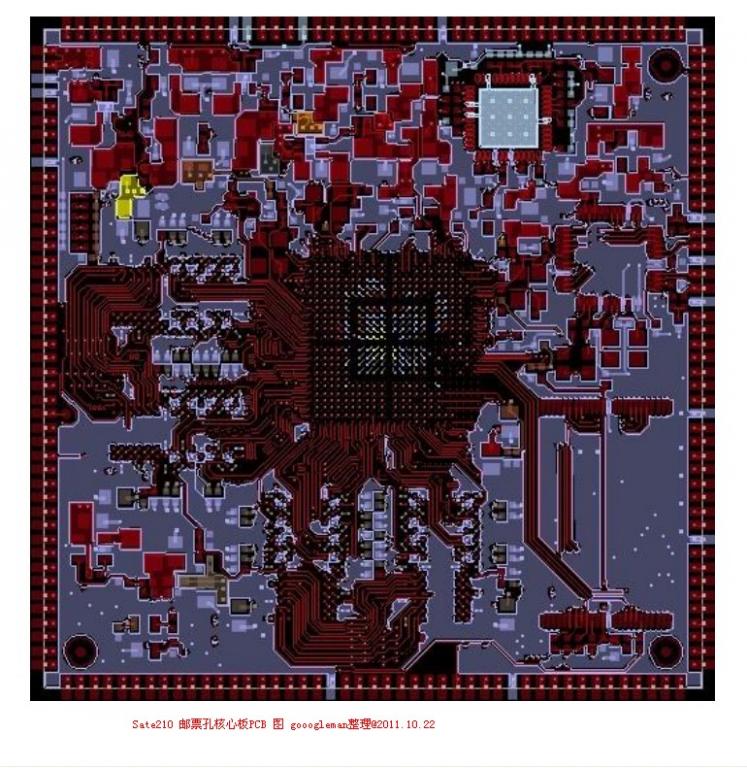

顶层和底层的单端走线线宽是5.5mil,差分线宽是4.5mil间距9mil,内部走线层端走线线宽是4.5mil,差分线宽是4.5mil间距9mil。除了阻抗控制还要对走线长度控制,控制走线长度目的是为了满足信号时延的要求,通常说就是走蛇形线。暂停一下,更加详细的Sate210 硬件设计说明请参照《Sate210硬件用户手册V1.2》,这个文档有60 多页,我已经上传到CSDN,有兴趣的人请去看看。《Sate210硬件用户手册V1.2》下载地址是:http://download.csdn.net/detail/gooogleman/3706515 6.2 Sate210 DDR 走线设计按照三星210的PCB设计指导手册,DDR部分的走线有以下要求:l 所有信号的容性负载为15pF@200MHz, 1.8V。所以所有的电容包括电路板的寄生电容要小于15PFl 走线阻抗控制为45Ω-55Ωl 走线分支尽量短l 最长走线长度45mml 信号走线必需有参考层(GND或PWR平面)l 走线尽量在内层l 尽量加强电源走线,去耦电容紧靠电源脚l DRAM芯片每个电源网络至少两个去耦电容l 使用完整的地平面和电源平面为信号提供参考面 6.2.1 Xm1DQS and Xm1DATA, Xm1DQM信号Xm1DQS0 & Xm1DATA[7:0], Xm1DQM0一组,Xm1DQS1 & Xm1DATA[15:8], Xm1DQM1一组,Xm1DQS2 & Xm1DATA[23:16], Xm1DQM2一组,Xm1DQS3 & Xm1DATA[31:24], Xm1DQM3一组,每组之间布线长度偏差± 5.0mm。如果是DDR2内存偏差为± 1.0mm。 6.2.2 Xm1SCLK and Xm1SCLKn信号l 推荐使用星形拓扑l 推荐差分阻抗为100Ωl Xm1SCLK & Xm1SCLKn布线长度偏差±1.0mml Xm1SCLK(n) & Xm1DQS[3:0] 布线长度偏差± 10mm 6.2.3其它控制信号 l Xm1SCLK(n) & Xm1ADDR[15:0], Xm1CASn, Xm1RASn, Xm1CKE[1:0], Xm1WEn布线长度偏差± 10mm;l 地址信号(Xm1CKE[1:0], Xm1CSn[1:0], Xm1ADDR[15:0], Xm1RASn, Xm1CASn, Xm1WEn)推荐使用T形拓扑;l 不要靠近高速信号(Xm1SCLK, Xm1SCLKn, Xm1DQS(n)[3:0] and Xm1DATA),与其保持至少3W线距;l 直接连接Xm1GATEI (pin B10)到Xm1GATEO (pin C10)。l Xm0与Xm1的要求是一样的。 6.3 Sate210核心板PCB图(供参考)

注意事项:由于Sate210核心板底面放置了一些滤波电容,所以设计底板PCB的时候要特别注意在适当的位置开槽,具体作法参照Sate210的底板设计与核心板尺寸图。 《6. Sate210 PCB设计说明》是由Sate210 团队硬件工程师C君完成,gooogleman负责整理的,如果有任何疑问,请发邮件到gooogleman@foxmail.com 探讨。

注意事项:由于Sate210核心板底面放置了一些滤波电容,所以设计底板PCB的时候要特别注意在适当的位置开槽,具体作法参照Sate210的底板设计与核心板尺寸图。 《6. Sate210 PCB设计说明》是由Sate210 团队硬件工程师C君完成,gooogleman负责整理的,如果有任何疑问,请发邮件到gooogleman@foxmail.com 探讨。

其中L3和L6是内部信号走线层,L2和L5是GND平面,L4是主电源层,L7是副电源层。为了核心板能运行稳定并且EMI要尽量小要对关键走线进行阻抗控制,一般单端走线的阻抗为50Ω,差分走线为100Ω,控制三星S5pv210的PCB设计指导手册单端阻抗从45Ω-55Ω都可以,但是要保证每一层的阻抗变化不大。下面是Sate210的阻抗控制表:

其中L3和L6是内部信号走线层,L2和L5是GND平面,L4是主电源层,L7是副电源层。为了核心板能运行稳定并且EMI要尽量小要对关键走线进行阻抗控制,一般单端走线的阻抗为50Ω,差分走线为100Ω,控制三星S5pv210的PCB设计指导手册单端阻抗从45Ω-55Ω都可以,但是要保证每一层的阻抗变化不大。下面是Sate210的阻抗控制表: 顶层和底层的单端走线线宽是5.5mil,差分线宽是4.5mil间距9mil,内部走线层端走线线宽是4.5mil,差分线宽是4.5mil间距9mil。除了阻抗控制还要对走线长度控制,控制走线长度目的是为了满足信号时延的要求,通常说就是走蛇形线。暂停一下,更加详细的Sate210 硬件设计说明请参照《Sate210硬件用户手册V1.2》,这个文档有60 多页,我已经上传到CSDN,有兴趣的人请去看看。《Sate210硬件用户手册V1.2》下载地址是:http://download.csdn.net/detail/gooogleman/3706515 6.2 Sate210 DDR 走线设计按照三星210的PCB设计指导手册,DDR部分的走线有以下要求:l 所有信号的容性负载为15pF@200MHz, 1.8V。所以所有的电容包括电路板的寄生电容要小于15PFl 走线阻抗控制为45Ω-55Ωl 走线分支尽量短l 最长走线长度45mml 信号走线必需有参考层(GND或PWR平面)l 走线尽量在内层l 尽量加强电源走线,去耦电容紧靠电源脚l DRAM芯片每个电源网络至少两个去耦电容l 使用完整的地平面和电源平面为信号提供参考面 6.2.1 Xm1DQS and Xm1DATA, Xm1DQM信号Xm1DQS0 & Xm1DATA[7:0], Xm1DQM0一组,Xm1DQS1 & Xm1DATA[15:8], Xm1DQM1一组,Xm1DQS2 & Xm1DATA[23:16], Xm1DQM2一组,Xm1DQS3 & Xm1DATA[31:24], Xm1DQM3一组,每组之间布线长度偏差± 5.0mm。如果是DDR2内存偏差为± 1.0mm。 6.2.2 Xm1SCLK and Xm1SCLKn信号l 推荐使用星形拓扑l 推荐差分阻抗为100Ωl Xm1SCLK & Xm1SCLKn布线长度偏差±1.0mml Xm1SCLK(n) & Xm1DQS[3:0] 布线长度偏差± 10mm 6.2.3其它控制信号 l Xm1SCLK(n) & Xm1ADDR[15:0], Xm1CASn, Xm1RASn, Xm1CKE[1:0], Xm1WEn布线长度偏差± 10mm;l 地址信号(Xm1CKE[1:0], Xm1CSn[1:0], Xm1ADDR[15:0], Xm1RASn, Xm1CASn, Xm1WEn)推荐使用T形拓扑;l 不要靠近高速信号(Xm1SCLK, Xm1SCLKn, Xm1DQS(n)[3:0] and Xm1DATA),与其保持至少3W线距;l 直接连接Xm1GATEI (pin B10)到Xm1GATEO (pin C10)。l Xm0与Xm1的要求是一样的。 6.3 Sate210核心板PCB图(供参考)

顶层和底层的单端走线线宽是5.5mil,差分线宽是4.5mil间距9mil,内部走线层端走线线宽是4.5mil,差分线宽是4.5mil间距9mil。除了阻抗控制还要对走线长度控制,控制走线长度目的是为了满足信号时延的要求,通常说就是走蛇形线。暂停一下,更加详细的Sate210 硬件设计说明请参照《Sate210硬件用户手册V1.2》,这个文档有60 多页,我已经上传到CSDN,有兴趣的人请去看看。《Sate210硬件用户手册V1.2》下载地址是:http://download.csdn.net/detail/gooogleman/3706515 6.2 Sate210 DDR 走线设计按照三星210的PCB设计指导手册,DDR部分的走线有以下要求:l 所有信号的容性负载为15pF@200MHz, 1.8V。所以所有的电容包括电路板的寄生电容要小于15PFl 走线阻抗控制为45Ω-55Ωl 走线分支尽量短l 最长走线长度45mml 信号走线必需有参考层(GND或PWR平面)l 走线尽量在内层l 尽量加强电源走线,去耦电容紧靠电源脚l DRAM芯片每个电源网络至少两个去耦电容l 使用完整的地平面和电源平面为信号提供参考面 6.2.1 Xm1DQS and Xm1DATA, Xm1DQM信号Xm1DQS0 & Xm1DATA[7:0], Xm1DQM0一组,Xm1DQS1 & Xm1DATA[15:8], Xm1DQM1一组,Xm1DQS2 & Xm1DATA[23:16], Xm1DQM2一组,Xm1DQS3 & Xm1DATA[31:24], Xm1DQM3一组,每组之间布线长度偏差± 5.0mm。如果是DDR2内存偏差为± 1.0mm。 6.2.2 Xm1SCLK and Xm1SCLKn信号l 推荐使用星形拓扑l 推荐差分阻抗为100Ωl Xm1SCLK & Xm1SCLKn布线长度偏差±1.0mml Xm1SCLK(n) & Xm1DQS[3:0] 布线长度偏差± 10mm 6.2.3其它控制信号 l Xm1SCLK(n) & Xm1ADDR[15:0], Xm1CASn, Xm1RASn, Xm1CKE[1:0], Xm1WEn布线长度偏差± 10mm;l 地址信号(Xm1CKE[1:0], Xm1CSn[1:0], Xm1ADDR[15:0], Xm1RASn, Xm1CASn, Xm1WEn)推荐使用T形拓扑;l 不要靠近高速信号(Xm1SCLK, Xm1SCLKn, Xm1DQS(n)[3:0] and Xm1DATA),与其保持至少3W线距;l 直接连接Xm1GATEI (pin B10)到Xm1GATEO (pin C10)。l Xm0与Xm1的要求是一样的。 6.3 Sate210核心板PCB图(供参考)

注意事项:由于Sate210核心板底面放置了一些滤波电容,所以设计底板PCB的时候要特别注意在适当的位置开槽,具体作法参照Sate210的底板设计与核心板尺寸图。 《6. Sate210 PCB设计说明》是由Sate210 团队硬件工程师C君完成,gooogleman负责整理的,如果有任何疑问,请发邮件到gooogleman@foxmail.com 探讨。

注意事项:由于Sate210核心板底面放置了一些滤波电容,所以设计底板PCB的时候要特别注意在适当的位置开槽,具体作法参照Sate210的底板设计与核心板尺寸图。 《6. Sate210 PCB设计说明》是由Sate210 团队硬件工程师C君完成,gooogleman负责整理的,如果有任何疑问,请发邮件到gooogleman@foxmail.com 探讨。 给我老师的人工智能教程打call!http://blog.csdn.net/jiangjunshow