来源https://blog.csdn.net/HururuKun/article/details/79606540

OrCAD 与 Cadence Allegro PCB 入门 - 以 16.6版本为例 (3)

2018年03月19日 01:32:41

阅读数:273

完成前两篇文章的内容后,现在才是真正开始画原理图和PCB的部分。上面一部分确实使得利用OrCAD/Cadence Allegro画PCB的最初的几个步骤变得繁琐,不过……毕竟是业界标杆的软件,说不定之后我会发现这个软件好用的部分呢。

一、绘制原理图(schematic)

这部分的用法和protel的使用相仿,这里就写几个绘制原理图是比较实用的窍门。

1. 给某个Net命名

使用Place Alias可以给部分一个相连接的Net命名。由于软件会自动给net命名为“Nxxxx”,这样部分网络名称就显得不直观,使用该功能就可以使得net的名称一目了然。

点击这个图标后,在小窗口中的Alias处键入想要给net起的名字。然后有个小框子,把小框子的下边沿和某个连线搭上,这样这个连线所连接的所有连线部分都改名为所起的名字了。

(a)未起名的网络 (b)起名了的网络

2. 更新元件图标

有时在画元件原理图符号的时候会出现一些偏差,当画都后面的时候发现有问题需要修改,这里就需要用到更新功能,这样可以免去手动一个一个删掉元件然后重新添加元件这样麻烦的事情了。

(1)修改原理图符号

(2)在工程文件管理目录中找到工程项目下面的Design Cache文件夹,右键点击修改过的元件,然后点选Update Cache。

(3)然后点选Replace Cache,勾选“Replace schematic part preperties”和“Preserve Refdes”两项,点击OK。之后所有的元件符号都会被替换成新的。

3. 元件自动编号

(1)在工程文件管理目录中右击工程原理图文件(xxx.dsn),选择Annotate。

(2)选择“Reset part references to ?”,然后点击OK。这将会把元件编号从"Ux"变为"U?"。

(3)选择“Incremental reference update”,然后点击OK。这将会把元件编号从"U?"变为"Ux"。这个过程就是自动编号的过程了。

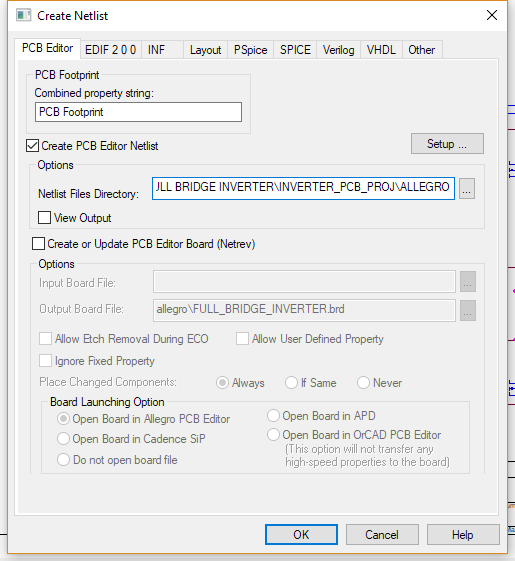

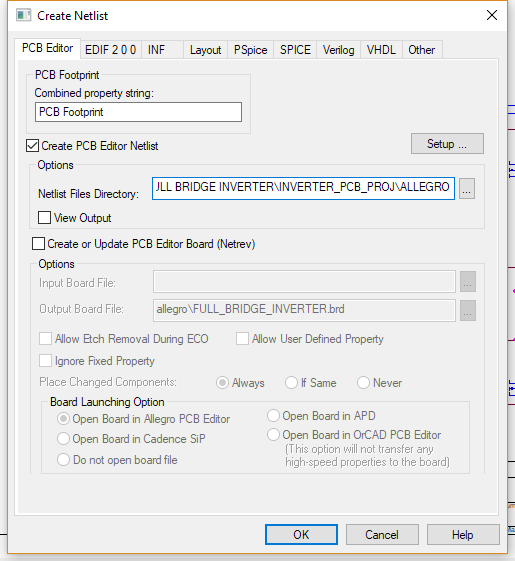

二、生成Netlist

这个步骤是将原理图的中的元件的连接映射到PCB当中的过程。

1. 首先保存当前的原理图文件(xxx.dsn)。

2. 在窗口顶部菜单栏中点击Tools -- Create Netlist。

3. 注意生成Netlist将会存储的路径,本例中设置为当前工程的菜单中新建名为“allegro”的文件夹。

三、开始画板子了

三、开始画板子了

1. 打开OrCAD PCB Editor,选择PCB Designer Professional。

2. 菜单栏中点击File -- New,选择新建类型为Board。注意保存路径为本工程的文件夹中。

3. 在黑 {MOD}的画布上右键点击 ,然后选择 Quick Utilities -- Design Parameters,然后到第二个标签页中修改画布大小为A3,这个尺寸比较合适。

4.导入Netlist。在菜单栏中选择Import -- Netlist。如图设置,注意选择的文件夹路径为在Capture CIS中生成的Netlist所存储的文件夹路径。

5. 放置元件。

在菜单栏中点选Place -- Component Manually,进行手动放置。勾选元件后,即可以在画布上布放元件了。

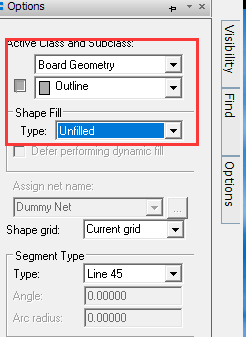

6. 画出PCB的边界

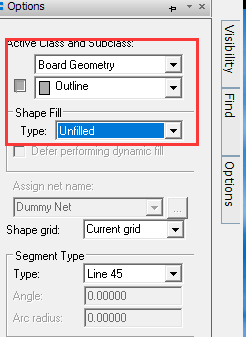

点击快捷工具栏中的Shape Add

,然后打开右侧option标签页,相关参数如图所示:

然后画出PCB板的边界。

7. 设置layout规则

在layout整个板子之前,需要设置layout的规则,这一点非常重要。点击Cmgr

,这里我们需要修改红框标出的三项的规则 。

根据需要,修改内容。

点击Physical -- All layer,修改DEFAULT部分有数值的项目。注意将VIA替换成需要的VIA类型。

点击Spacing -- All layer,修改DEFAULT部分有数值的项目。

点击Same Net Spacing -- All layer,修改DEFAULT部分有数值的项目。

8. 添加连线

选择Add Connect

开始连线。连线过程中可以改变连线粗细:右击鼠标,选择Option -- Line width -- New。

9. 添加VIA

右击鼠标,选择Add Via。

8.添加多边形底边

选择Add Polygon

,然后再Option中设定如下图

如此一来,可以在地面画出一个巨大的一面地。画好的PCB如图所示。

10. 检查

在菜单栏点击Check -- Design Status。

点击Update DRC,检查DRC(Design Rule Checking)的状态。如果没有违反规则的地方,结果即为下图所示。

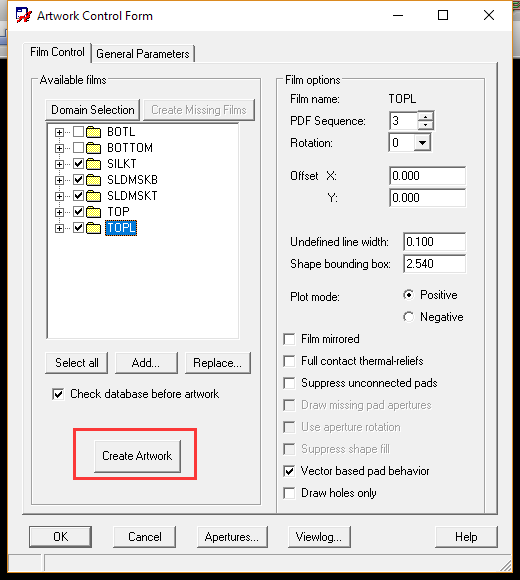

四、导出工程

四、导出工程

1. 建立各个层

由于一个板子有多层构成,除了顶层和底层,外侧还有绝缘的油墨层和丝印层等。所以需要建立多个层。

a. 查看不同层

菜单栏选择Setup -- Colors。打开后点选Global Visibility -- off,然后apply,世界一片黑暗了。

然后勾选Stack-Up中的TOP层,和Board Geometry的Outline部分。就会出现如下图层:

c. 存储该层

菜单栏中点选Display -- View -- Color View Save,存储该层为TOPL(top layer)。

同理,保存以下不同的层

底层BOTL:

(Stack-Up的Bottom,Board Geometry的Outline)

顶层丝印SILKT:

(Board Geometry的Outline,Package Geometry的Silkscreen_Top,Component的Silkscreen_Top)

顶层焊盘SLDMSKT:

(Stack-Up的Soldermask_Top,Board Geometry的Outline)

底层焊盘SLDMSKB:

(Stack-Up的Soldermask_Bottom,Board Geometry的Outline)

下图就是我们刚才新建的五个不同的view layer,方便查看,也方便下一步导出gerber文件给厂家生产电路板。

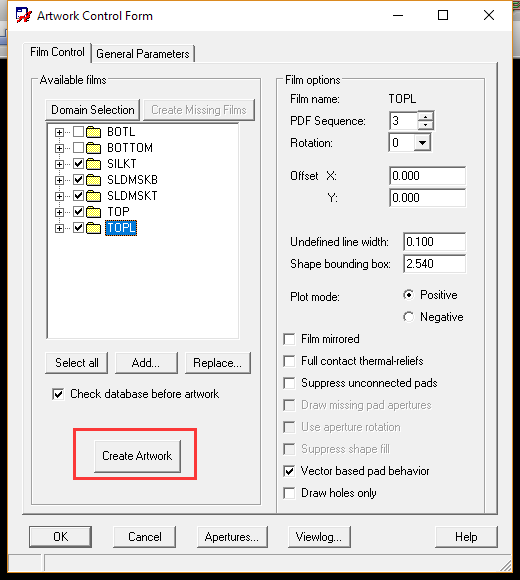

2. 生成Gerber文件

当你生成这些文件后,就可以把这些文件发给制作电路板的公司去生产你的电路板了。

a. 菜单栏点击Export -- Gerber,然后就打开了Artwork Control Form。在软件自动生成的层上,右键,然后选择Add,并命名对层。如下图,我命名了和上一小节一致的五个层,分别为TOPL, BOTL, SLDMSKT, SLDMSKB 和SILKT。

b. 把所有未定义的线宽设置为0.1。

c. 创建artwork文件

这样就生成成功了,使用gerber浏览器可以查看当前生成的.art文件。我这里使用的是gerbv。

3. 生成Drill文件

除了各层文件,电路板还有打孔的问题,所以需要生成Drill文件来生成有关孔位的文件。

菜单栏中点击Export -- NC Drill,然后选择这些内容。

生成的Drill文件就吼了。

个人分类:

OrCAD & Cadence Allegro

相关热词:

orcad分层 orcad批量 orcad稳压管 orcad仿真 orcad闪退

点击这个图标后,在小窗口中的Alias处键入想要给net起的名字。然后有个小框子,把小框子的下边沿和某个连线搭上,这样这个连线所连接的所有连线部分都改名为所起的名字了。

点击这个图标后,在小窗口中的Alias处键入想要给net起的名字。然后有个小框子,把小框子的下边沿和某个连线搭上,这样这个连线所连接的所有连线部分都改名为所起的名字了。

(a)未起名的网络 (b)起名了的网络

2. 更新元件图标

有时在画元件原理图符号的时候会出现一些偏差,当画都后面的时候发现有问题需要修改,这里就需要用到更新功能,这样可以免去手动一个一个删掉元件然后重新添加元件这样麻烦的事情了。

(1)修改原理图符号

(2)在工程文件管理目录中找到工程项目下面的Design Cache文件夹,右键点击修改过的元件,然后点选Update Cache。

(a)未起名的网络 (b)起名了的网络

2. 更新元件图标

有时在画元件原理图符号的时候会出现一些偏差,当画都后面的时候发现有问题需要修改,这里就需要用到更新功能,这样可以免去手动一个一个删掉元件然后重新添加元件这样麻烦的事情了。

(1)修改原理图符号

(2)在工程文件管理目录中找到工程项目下面的Design Cache文件夹,右键点击修改过的元件,然后点选Update Cache。

(3)然后点选Replace Cache,勾选“Replace schematic part preperties”和“Preserve Refdes”两项,点击OK。之后所有的元件符号都会被替换成新的。

(3)然后点选Replace Cache,勾选“Replace schematic part preperties”和“Preserve Refdes”两项,点击OK。之后所有的元件符号都会被替换成新的。

3. 元件自动编号

(1)在工程文件管理目录中右击工程原理图文件(xxx.dsn),选择Annotate。

3. 元件自动编号

(1)在工程文件管理目录中右击工程原理图文件(xxx.dsn),选择Annotate。

(2)选择“Reset part references to ?”,然后点击OK。这将会把元件编号从"Ux"变为"U?"。

(3)选择“Incremental reference update”,然后点击OK。这将会把元件编号从"U?"变为"Ux"。这个过程就是自动编号的过程了。

二、生成Netlist

这个步骤是将原理图的中的元件的连接映射到PCB当中的过程。

1. 首先保存当前的原理图文件(xxx.dsn)。

2. 在窗口顶部菜单栏中点击Tools -- Create Netlist。

3. 注意生成Netlist将会存储的路径,本例中设置为当前工程的菜单中新建名为“allegro”的文件夹。

(2)选择“Reset part references to ?”,然后点击OK。这将会把元件编号从"Ux"变为"U?"。

(3)选择“Incremental reference update”,然后点击OK。这将会把元件编号从"U?"变为"Ux"。这个过程就是自动编号的过程了。

二、生成Netlist

这个步骤是将原理图的中的元件的连接映射到PCB当中的过程。

1. 首先保存当前的原理图文件(xxx.dsn)。

2. 在窗口顶部菜单栏中点击Tools -- Create Netlist。

3. 注意生成Netlist将会存储的路径,本例中设置为当前工程的菜单中新建名为“allegro”的文件夹。

三、开始画板子了

1. 打开OrCAD PCB Editor,选择PCB Designer Professional。

2. 菜单栏中点击File -- New,选择新建类型为Board。注意保存路径为本工程的文件夹中。

三、开始画板子了

1. 打开OrCAD PCB Editor,选择PCB Designer Professional。

2. 菜单栏中点击File -- New,选择新建类型为Board。注意保存路径为本工程的文件夹中。

3. 在黑 {MOD}的画布上右键点击 ,然后选择 Quick Utilities -- Design Parameters,然后到第二个标签页中修改画布大小为A3,这个尺寸比较合适。

4.导入Netlist。在菜单栏中选择Import -- Netlist。如图设置,注意选择的文件夹路径为在Capture CIS中生成的Netlist所存储的文件夹路径。

3. 在黑 {MOD}的画布上右键点击 ,然后选择 Quick Utilities -- Design Parameters,然后到第二个标签页中修改画布大小为A3,这个尺寸比较合适。

4.导入Netlist。在菜单栏中选择Import -- Netlist。如图设置,注意选择的文件夹路径为在Capture CIS中生成的Netlist所存储的文件夹路径。

5. 放置元件。

在菜单栏中点选Place -- Component Manually,进行手动放置。勾选元件后,即可以在画布上布放元件了。

5. 放置元件。

在菜单栏中点选Place -- Component Manually,进行手动放置。勾选元件后,即可以在画布上布放元件了。

6. 画出PCB的边界

点击快捷工具栏中的Shape Add

6. 画出PCB的边界

点击快捷工具栏中的Shape Add  ,然后打开右侧option标签页,相关参数如图所示:

,然后打开右侧option标签页,相关参数如图所示:

然后画出PCB板的边界。

然后画出PCB板的边界。

7. 设置layout规则

在layout整个板子之前,需要设置layout的规则,这一点非常重要。点击Cmgr

7. 设置layout规则

在layout整个板子之前,需要设置layout的规则,这一点非常重要。点击Cmgr ,这里我们需要修改红框标出的三项的规则 。

,这里我们需要修改红框标出的三项的规则 。

根据需要,修改内容。

点击Physical -- All layer,修改DEFAULT部分有数值的项目。注意将VIA替换成需要的VIA类型。

点击Spacing -- All layer,修改DEFAULT部分有数值的项目。

点击Same Net Spacing -- All layer,修改DEFAULT部分有数值的项目。

8. 添加连线

选择Add Connect

根据需要,修改内容。

点击Physical -- All layer,修改DEFAULT部分有数值的项目。注意将VIA替换成需要的VIA类型。

点击Spacing -- All layer,修改DEFAULT部分有数值的项目。

点击Same Net Spacing -- All layer,修改DEFAULT部分有数值的项目。

8. 添加连线

选择Add Connect  开始连线。连线过程中可以改变连线粗细:右击鼠标,选择Option -- Line width -- New。

9. 添加VIA

右击鼠标,选择Add Via。

8.添加多边形底边

选择Add Polygon

开始连线。连线过程中可以改变连线粗细:右击鼠标,选择Option -- Line width -- New。

9. 添加VIA

右击鼠标,选择Add Via。

8.添加多边形底边

选择Add Polygon  ,然后再Option中设定如下图

,然后再Option中设定如下图

如此一来,可以在地面画出一个巨大的一面地。画好的PCB如图所示。

如此一来,可以在地面画出一个巨大的一面地。画好的PCB如图所示。

10. 检查

在菜单栏点击Check -- Design Status。

10. 检查

在菜单栏点击Check -- Design Status。

点击Update DRC,检查DRC(Design Rule Checking)的状态。如果没有违反规则的地方,结果即为下图所示。

点击Update DRC,检查DRC(Design Rule Checking)的状态。如果没有违反规则的地方,结果即为下图所示。

四、导出工程

1. 建立各个层

由于一个板子有多层构成,除了顶层和底层,外侧还有绝缘的油墨层和丝印层等。所以需要建立多个层。

a. 查看不同层

菜单栏选择Setup -- Colors。打开后点选Global Visibility -- off,然后apply,世界一片黑暗了。

四、导出工程

1. 建立各个层

由于一个板子有多层构成,除了顶层和底层,外侧还有绝缘的油墨层和丝印层等。所以需要建立多个层。

a. 查看不同层

菜单栏选择Setup -- Colors。打开后点选Global Visibility -- off,然后apply,世界一片黑暗了。

然后勾选Stack-Up中的TOP层,和Board Geometry的Outline部分。就会出现如下图层:

然后勾选Stack-Up中的TOP层,和Board Geometry的Outline部分。就会出现如下图层:

c. 存储该层

菜单栏中点选Display -- View -- Color View Save,存储该层为TOPL(top layer)。

c. 存储该层

菜单栏中点选Display -- View -- Color View Save,存储该层为TOPL(top layer)。

同理,保存以下不同的层

底层BOTL:

(Stack-Up的Bottom,Board Geometry的Outline)

顶层丝印SILKT:

(Board Geometry的Outline,Package Geometry的Silkscreen_Top,Component的Silkscreen_Top)

顶层焊盘SLDMSKT:

(Stack-Up的Soldermask_Top,Board Geometry的Outline)

底层焊盘SLDMSKB:

(Stack-Up的Soldermask_Bottom,Board Geometry的Outline)

下图就是我们刚才新建的五个不同的view layer,方便查看,也方便下一步导出gerber文件给厂家生产电路板。

同理,保存以下不同的层

底层BOTL:

(Stack-Up的Bottom,Board Geometry的Outline)

顶层丝印SILKT:

(Board Geometry的Outline,Package Geometry的Silkscreen_Top,Component的Silkscreen_Top)

顶层焊盘SLDMSKT:

(Stack-Up的Soldermask_Top,Board Geometry的Outline)

底层焊盘SLDMSKB:

(Stack-Up的Soldermask_Bottom,Board Geometry的Outline)

下图就是我们刚才新建的五个不同的view layer,方便查看,也方便下一步导出gerber文件给厂家生产电路板。

2. 生成Gerber文件

当你生成这些文件后,就可以把这些文件发给制作电路板的公司去生产你的电路板了。

a. 菜单栏点击Export -- Gerber,然后就打开了Artwork Control Form。在软件自动生成的层上,右键,然后选择Add,并命名对层。如下图,我命名了和上一小节一致的五个层,分别为TOPL, BOTL, SLDMSKT, SLDMSKB 和SILKT。

2. 生成Gerber文件

当你生成这些文件后,就可以把这些文件发给制作电路板的公司去生产你的电路板了。

a. 菜单栏点击Export -- Gerber,然后就打开了Artwork Control Form。在软件自动生成的层上,右键,然后选择Add,并命名对层。如下图,我命名了和上一小节一致的五个层,分别为TOPL, BOTL, SLDMSKT, SLDMSKB 和SILKT。

b. 把所有未定义的线宽设置为0.1。

b. 把所有未定义的线宽设置为0.1。

c. 创建artwork文件

c. 创建artwork文件

这样就生成成功了,使用gerber浏览器可以查看当前生成的.art文件。我这里使用的是gerbv。

这样就生成成功了,使用gerber浏览器可以查看当前生成的.art文件。我这里使用的是gerbv。

3. 生成Drill文件

除了各层文件,电路板还有打孔的问题,所以需要生成Drill文件来生成有关孔位的文件。

菜单栏中点击Export -- NC Drill,然后选择这些内容。

3. 生成Drill文件

除了各层文件,电路板还有打孔的问题,所以需要生成Drill文件来生成有关孔位的文件。

菜单栏中点击Export -- NC Drill,然后选择这些内容。

生成的Drill文件就吼了。

个人分类: OrCAD & Cadence Allegro

相关热词: orcad分层 orcad批量 orcad稳压管 orcad仿真 orcad闪退

生成的Drill文件就吼了。

个人分类: OrCAD & Cadence Allegro

相关热词: orcad分层 orcad批量 orcad稳压管 orcad仿真 orcad闪退