简单地说,从PCB板厂拿到各层的Thickness参数(或许介电常数也可以提供)后,利用Si9000设定好差分阻抗100Ω,计算出合适的差分线宽和线间距。

项目上使用的层叠设置如下图所示,下图中各层的Thickness由PCB板厂提供。

上图勾选了右下角的Show Diff Impedance。

首先以Top层为例:

Top层厚度Thickness=2.1mil,介电常数Dielectric Constant=4.2,线宽Width=5.10mil,差分线内间距Spacing=8.5mil,Top层相邻的介质层的厚度为3.85mil,介质层的介电常数=4.5,Cross Section计算出的差分阻抗为88.622ohm,下面使用Si9000并使用相同的参数计算差分阻抗,用于与Allegro的计算结果对比。下图是相同参数条件下,Si9000的差分阻抗计算结果:

上图勾选了右下角的Show Diff Impedance。

首先以Top层为例:

Top层厚度Thickness=2.1mil,介电常数Dielectric Constant=4.2,线宽Width=5.10mil,差分线内间距Spacing=8.5mil,Top层相邻的介质层的厚度为3.85mil,介质层的介电常数=4.5,Cross Section计算出的差分阻抗为88.622ohm,下面使用Si9000并使用相同的参数计算差分阻抗,用于与Allegro的计算结果对比。下图是相同参数条件下,Si9000的差分阻抗计算结果:

上图中,介质层厚度H1设置为3.85mil,介质层介电常数Er1设置为4.5mil,线宽W1(就是一般说的线宽)设置为5.1mil,线宽W2设置为(W1-0.5mil)=4.6mil,差分线内间距S1设置为8.5mil,Top层厚度T1设置为2.1mil,Si9000计算出的差分阻抗为99.07ohm,因此相对于Allegro的计算结果88.622ohm,Si9000的计算结果要偏大一些。

再以ART03层为例:

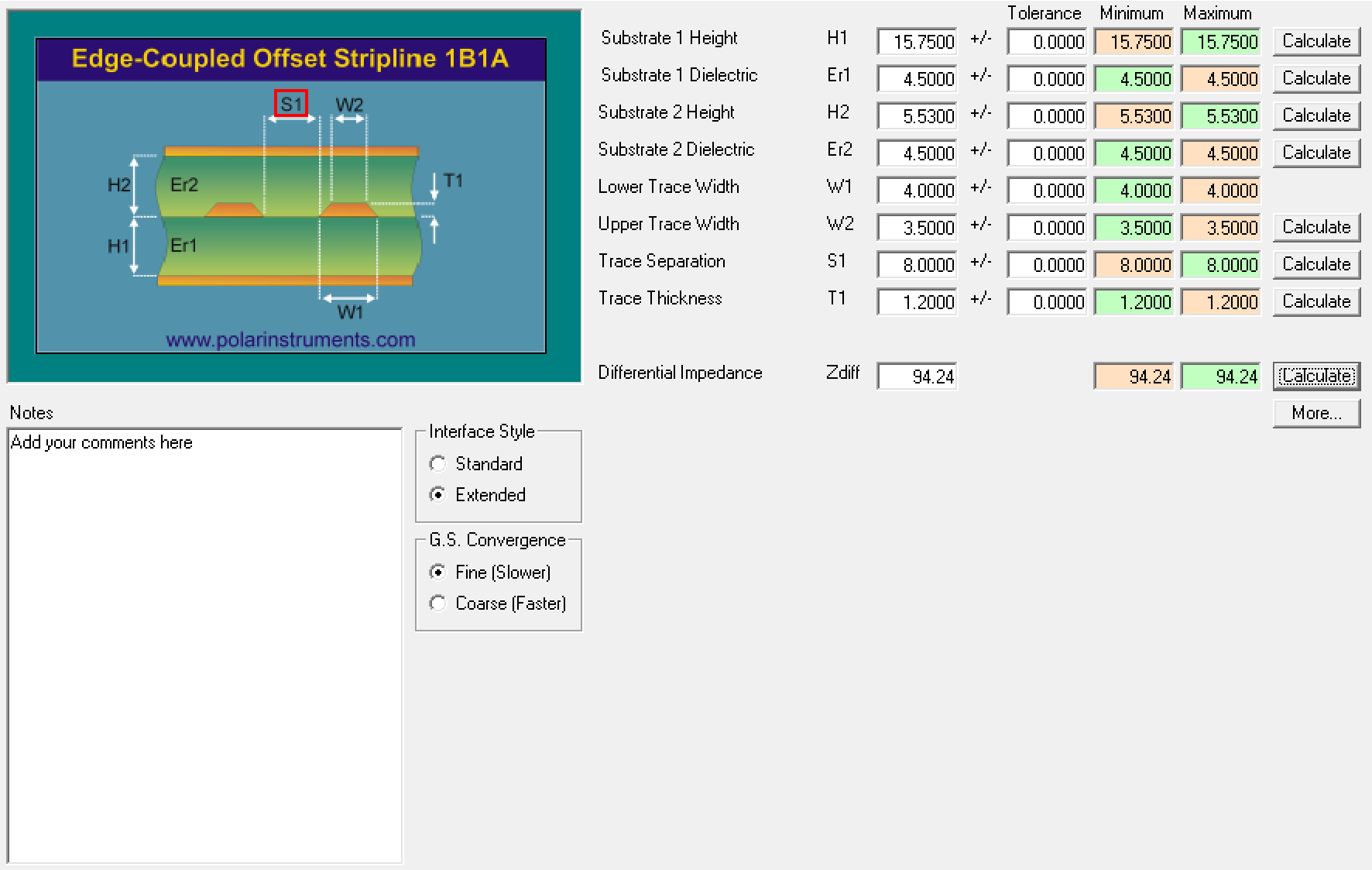

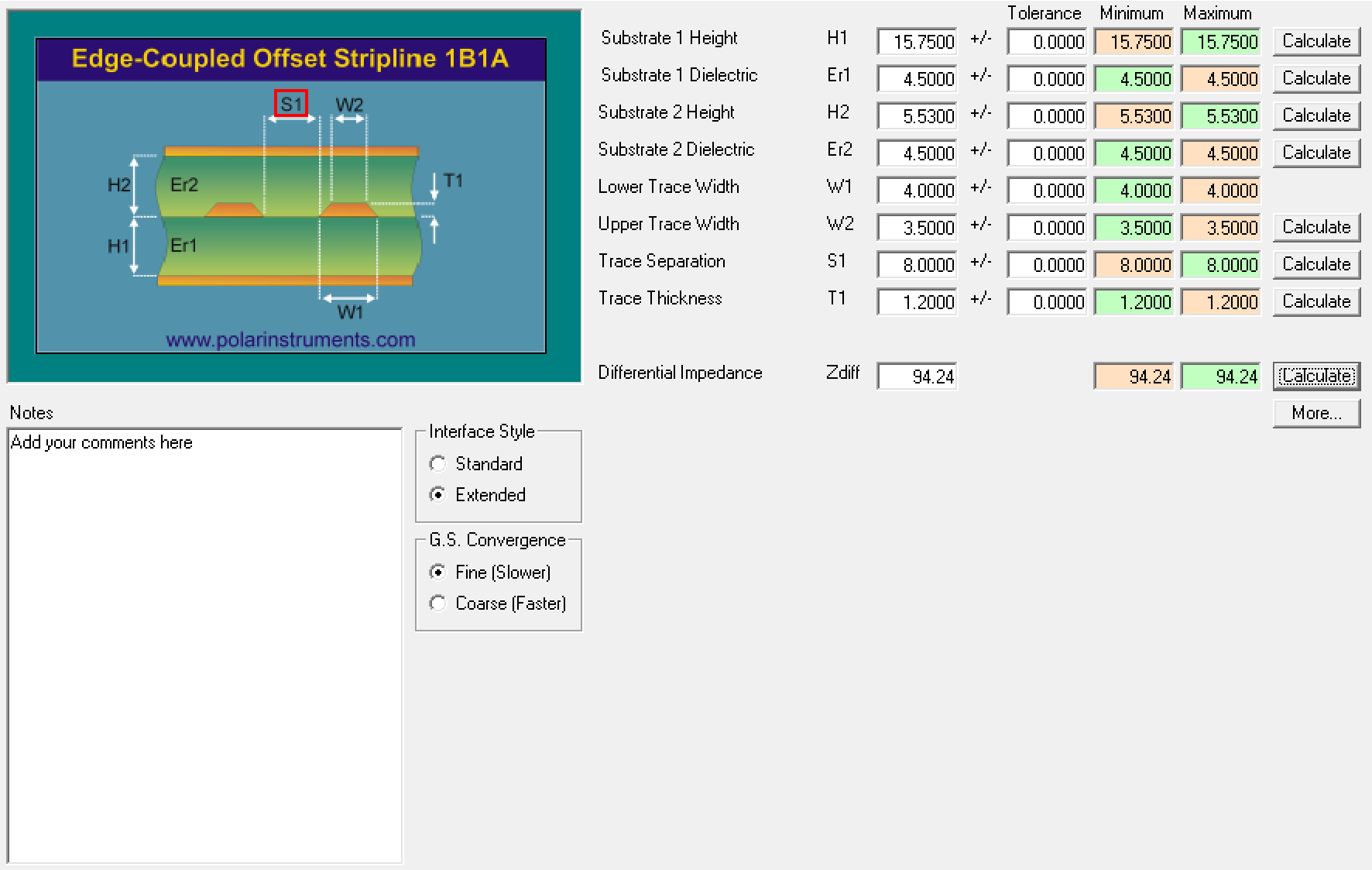

ART03层厚度Thickness=1.2mil,介电常数Dielectric Constant=4.2,线宽Width=4.00mil,差分线内间距Spacing=8.00mil,ART03层上方的介质层的厚度为4.33mil,介质层的介电常数=4.5,ART03层下方的介质层的厚度为15.75mil,介质层的介电常数=4.5,Cross Section计算出的差分阻抗为93.677ohm,下面使用Si9000并使用相同的参数计算差分阻抗,用于与Allegro的计算结果对比。下图是相同参数条件下,Si9000的差分阻抗计算结果:

上图中,介质层厚度H1设置为3.85mil,介质层介电常数Er1设置为4.5mil,线宽W1(就是一般说的线宽)设置为5.1mil,线宽W2设置为(W1-0.5mil)=4.6mil,差分线内间距S1设置为8.5mil,Top层厚度T1设置为2.1mil,Si9000计算出的差分阻抗为99.07ohm,因此相对于Allegro的计算结果88.622ohm,Si9000的计算结果要偏大一些。

再以ART03层为例:

ART03层厚度Thickness=1.2mil,介电常数Dielectric Constant=4.2,线宽Width=4.00mil,差分线内间距Spacing=8.00mil,ART03层上方的介质层的厚度为4.33mil,介质层的介电常数=4.5,ART03层下方的介质层的厚度为15.75mil,介质层的介电常数=4.5,Cross Section计算出的差分阻抗为93.677ohm,下面使用Si9000并使用相同的参数计算差分阻抗,用于与Allegro的计算结果对比。下图是相同参数条件下,Si9000的差分阻抗计算结果:

上图中,ART03层下方的介质层厚度H1设置为15.75mil,介质层介电常数Er1设置为4.5mil,ART03层上方的介质层厚度H2设置为5.53mil(4.33mil+1.2mil),介质层介电常数Er2设置为4.5mil,线宽W1(就是一般说的线宽)设置为4.00mil,线宽W2设置为(W1-0.5mil)=3.5mil,差分线内间距S1设置为8.0mil,ART03层厚度T1设置为1.2mil,Si9000计算出的差分阻抗为94.24ohm,因此相对于Allegro的计算结果93.677ohm,Si9000的计算结果要偏大一些。

似乎Si9000的结果更被接受。

可以看出,Top层差分线线宽设置为5.1mil,差分线内间距设置为8.5mil,内部走线层差分线线宽设置为是4.00mil,差分线内间距设置为8.0mil是合适的,因此可以在约束管理器中将100ohm差分线的线宽Min Line Width设置为5.1mil(Top层)和4.00mil(内部走线层),将100ohm差分线的Primary Gap设置为8.5mil(Top层)和8.00mil(内部走线层)。

上图中,ART03层下方的介质层厚度H1设置为15.75mil,介质层介电常数Er1设置为4.5mil,ART03层上方的介质层厚度H2设置为5.53mil(4.33mil+1.2mil),介质层介电常数Er2设置为4.5mil,线宽W1(就是一般说的线宽)设置为4.00mil,线宽W2设置为(W1-0.5mil)=3.5mil,差分线内间距S1设置为8.0mil,ART03层厚度T1设置为1.2mil,Si9000计算出的差分阻抗为94.24ohm,因此相对于Allegro的计算结果93.677ohm,Si9000的计算结果要偏大一些。

似乎Si9000的结果更被接受。

可以看出,Top层差分线线宽设置为5.1mil,差分线内间距设置为8.5mil,内部走线层差分线线宽设置为是4.00mil,差分线内间距设置为8.0mil是合适的,因此可以在约束管理器中将100ohm差分线的线宽Min Line Width设置为5.1mil(Top层)和4.00mil(内部走线层),将100ohm差分线的Primary Gap设置为8.5mil(Top层)和8.00mil(内部走线层)。

上图勾选了右下角的Show Diff Impedance。

首先以Top层为例:

Top层厚度Thickness=2.1mil,介电常数Dielectric Constant=4.2,线宽Width=5.10mil,差分线内间距Spacing=8.5mil,Top层相邻的介质层的厚度为3.85mil,介质层的介电常数=4.5,Cross Section计算出的差分阻抗为88.622ohm,下面使用Si9000并使用相同的参数计算差分阻抗,用于与Allegro的计算结果对比。下图是相同参数条件下,Si9000的差分阻抗计算结果:

上图勾选了右下角的Show Diff Impedance。

首先以Top层为例:

Top层厚度Thickness=2.1mil,介电常数Dielectric Constant=4.2,线宽Width=5.10mil,差分线内间距Spacing=8.5mil,Top层相邻的介质层的厚度为3.85mil,介质层的介电常数=4.5,Cross Section计算出的差分阻抗为88.622ohm,下面使用Si9000并使用相同的参数计算差分阻抗,用于与Allegro的计算结果对比。下图是相同参数条件下,Si9000的差分阻抗计算结果:

上图中,介质层厚度H1设置为3.85mil,介质层介电常数Er1设置为4.5mil,线宽W1(就是一般说的线宽)设置为5.1mil,线宽W2设置为(W1-0.5mil)=4.6mil,差分线内间距S1设置为8.5mil,Top层厚度T1设置为2.1mil,Si9000计算出的差分阻抗为99.07ohm,因此相对于Allegro的计算结果88.622ohm,Si9000的计算结果要偏大一些。

再以ART03层为例:

ART03层厚度Thickness=1.2mil,介电常数Dielectric Constant=4.2,线宽Width=4.00mil,差分线内间距Spacing=8.00mil,ART03层上方的介质层的厚度为4.33mil,介质层的介电常数=4.5,ART03层下方的介质层的厚度为15.75mil,介质层的介电常数=4.5,Cross Section计算出的差分阻抗为93.677ohm,下面使用Si9000并使用相同的参数计算差分阻抗,用于与Allegro的计算结果对比。下图是相同参数条件下,Si9000的差分阻抗计算结果:

上图中,介质层厚度H1设置为3.85mil,介质层介电常数Er1设置为4.5mil,线宽W1(就是一般说的线宽)设置为5.1mil,线宽W2设置为(W1-0.5mil)=4.6mil,差分线内间距S1设置为8.5mil,Top层厚度T1设置为2.1mil,Si9000计算出的差分阻抗为99.07ohm,因此相对于Allegro的计算结果88.622ohm,Si9000的计算结果要偏大一些。

再以ART03层为例:

ART03层厚度Thickness=1.2mil,介电常数Dielectric Constant=4.2,线宽Width=4.00mil,差分线内间距Spacing=8.00mil,ART03层上方的介质层的厚度为4.33mil,介质层的介电常数=4.5,ART03层下方的介质层的厚度为15.75mil,介质层的介电常数=4.5,Cross Section计算出的差分阻抗为93.677ohm,下面使用Si9000并使用相同的参数计算差分阻抗,用于与Allegro的计算结果对比。下图是相同参数条件下,Si9000的差分阻抗计算结果:

上图中,ART03层下方的介质层厚度H1设置为15.75mil,介质层介电常数Er1设置为4.5mil,ART03层上方的介质层厚度H2设置为5.53mil(4.33mil+1.2mil),介质层介电常数Er2设置为4.5mil,线宽W1(就是一般说的线宽)设置为4.00mil,线宽W2设置为(W1-0.5mil)=3.5mil,差分线内间距S1设置为8.0mil,ART03层厚度T1设置为1.2mil,Si9000计算出的差分阻抗为94.24ohm,因此相对于Allegro的计算结果93.677ohm,Si9000的计算结果要偏大一些。

似乎Si9000的结果更被接受。

可以看出,Top层差分线线宽设置为5.1mil,差分线内间距设置为8.5mil,内部走线层差分线线宽设置为是4.00mil,差分线内间距设置为8.0mil是合适的,因此可以在约束管理器中将100ohm差分线的线宽Min Line Width设置为5.1mil(Top层)和4.00mil(内部走线层),将100ohm差分线的Primary Gap设置为8.5mil(Top层)和8.00mil(内部走线层)。

上图中,ART03层下方的介质层厚度H1设置为15.75mil,介质层介电常数Er1设置为4.5mil,ART03层上方的介质层厚度H2设置为5.53mil(4.33mil+1.2mil),介质层介电常数Er2设置为4.5mil,线宽W1(就是一般说的线宽)设置为4.00mil,线宽W2设置为(W1-0.5mil)=3.5mil,差分线内间距S1设置为8.0mil,ART03层厚度T1设置为1.2mil,Si9000计算出的差分阻抗为94.24ohm,因此相对于Allegro的计算结果93.677ohm,Si9000的计算结果要偏大一些。

似乎Si9000的结果更被接受。

可以看出,Top层差分线线宽设置为5.1mil,差分线内间距设置为8.5mil,内部走线层差分线线宽设置为是4.00mil,差分线内间距设置为8.0mil是合适的,因此可以在约束管理器中将100ohm差分线的线宽Min Line Width设置为5.1mil(Top层)和4.00mil(内部走线层),将100ohm差分线的Primary Gap设置为8.5mil(Top层)和8.00mil(内部走线层)。