通用的高速信号PCB设计处理原则有:

(1)层面的选择:处理高速信号优先选择两边是GND的层面处理

(2)处理时要优先考虑高速信号的总长

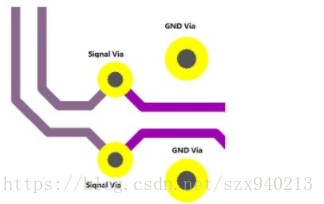

(3)高速信号Via数量的限制:高速信号允许换一次层,换层时加GND VIA如图:

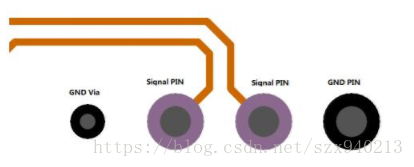

(4)如果高速信号在连接器有一端信号没有与GND 相邻PIN时,设计时应加GND VIA 如下图:

(5)高速信号在连接器内的走线要求:在连接器内走线要中心出线。

(6)高速信号应设置不耦合长度及本对信号的长度误差,在做长度误差时须考虑是否要加PIN DELAY

(7)高速信号处理时尽量收发走在不同层,如果空间有限,需收发同层时,应加大收发信号的距离

(8)高速信号离12V 要有180 MIL的间距要求,距离时钟信号65mil间距