基于FPGA的详细设计流程

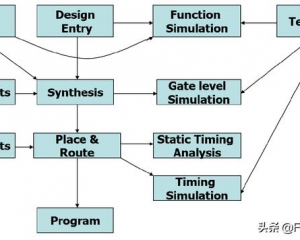

本文主要讲述FPGA开发过程。标准设计流程一、Design在系统设计之前,首先要进行的是方案论证、系统设计和 FPGA 芯片选择等准备工作。 系统工程师根据任务要求,如系统的指标和复杂度,对工作速度和芯片本 身的各种资源、 成本等方面进行权衡,选择合理的设计...

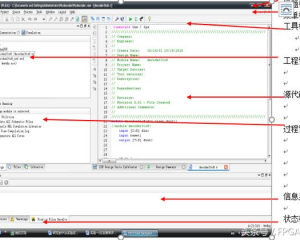

Xilinx的FPGA开发工具——ISE开发流程

在计算机桌面上双击ISE图标,便可以启动ISE软件的运行。整个界面采用标准Windows格式,共分8个部分:标题栏、菜单栏、工具栏、工程管理栏、源代码文件编辑区、过程管理区、信息显示区和状态栏。图1 ISE 工具界面具体菜单栏中的各项的具体功能可以阅读相关资料...

嵌入式领域,FPGA的串口通信接口设计,VHDL编程,altera平台

一、FPGA的UART设计前准备1、准备硬件开发板一个,altera芯片就行,成本低;2、熟悉VHDL硬件描述语言编程及其调试方法;3、熟练使用软件开发工具使用,QuartusII9.0,仿真工具modelsim。4、做UART串口设计之前先上网学习UART原理,实现FPGA接口电路设计。二、...

干货分享,FPGA硬件系统的设计技巧

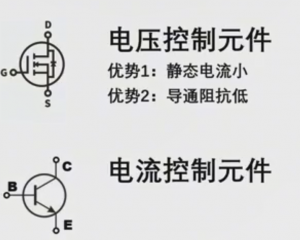

PGA的硬件设计不同于DSP和ARM系统,比较灵活和自由。只要设计好专用管脚的电路,通用I/O的连接可以自己定义。因此,FPGA的电路设计中会有一些特殊的技巧可以参考。1. FPGA管脚兼容性设计FPGA在芯片选项时要尽量选择兼容性好的封装。那么,在硬件电路设计时,...

你知道Verilog HDL程序是如何构成的吗

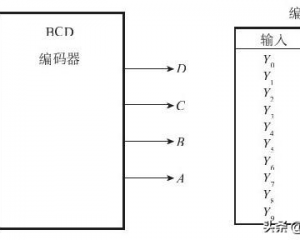

本节通过硬件描述语言Verilog HDL对二十进制编码器的描述,介绍Verilog HDL程序的基本结构及特点。二十进制编码器及Verilog HDL描述二十进制编码器是数字电路中常用的电路单元,它的输入是代表0~9这10个输入端的状态信息。输入信...

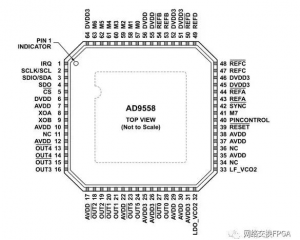

一种通过FPGA对AD9558时钟管理芯片进行配置的方法

原本一个很普通的时钟管理芯片,通过自带软件用串口很容易就能够进行配置,但尝试着写FPGA代码进行配置却遇到了各种困难,等最终问题解决后才发现,是忽略了一个很小的细节。硬件调试就是这样,只要是没有调试经验,一个很小的细...