通过list实现allegro第三方网表交互布局并添加room属性

由Altium Designer等软件生成的网表导入allegro后,无法实现PCB和原理图交互布局,对器件选取和模块划分很不方便。只能通过list文件选取,然后添加room属性,实现模块划分。

1、全选本页/模块元件,这里照样按allegro原理图来得到...

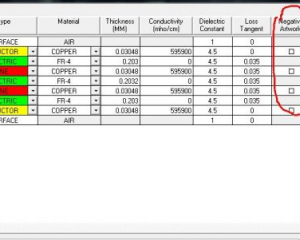

Cadence16.5 叠层设置怎样设置正片负片

allegro16.5多层PCB板的叠层设计时,内电层设计为正片或负片的选项不知道怎样处理,我原来用的是allegro15.7,allegro15.7设置内电层时,它有个选项,可选为正片或负片,但allegro16.5没看到这个选项,怎么办?Show diff impedance 不要打勾,就会显示出来

...

Cadence Allegro学习之copy+Change+delete+走线居中技巧

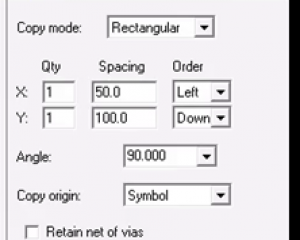

1copy

选择复制个数

是否带属性复制

2change命令

相同class不同sub下切换

3删除命令删除命令记着选择删除对象的类型,不然容易误删

删除与其有电器特性的东西

删除net时是否删除其他

4走线居中技巧

双击两...

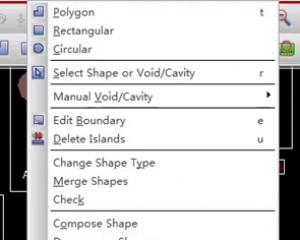

Cadence Allegro学习之铜皮(走粗线)的使用方法+罐铜+铜皮切割

1(1)附铜全局操作

设置附铜效果

附铜菜单

任何角度铜皮

指定铜皮网络

方形铜皮角度参数

删除鼓捣

挖铜皮

修整铜皮边界

删除鼓捣铜皮

铜皮合并...

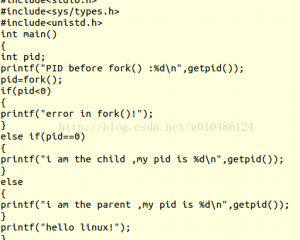

Linux 系统调用之 fork()——进程的创建

对于主进程 fork()返回新建的子进程ID, 子进程fork()返回0

进程配置有唯一的进程控制块PCB,由proc结构和usr结构组成。

下面依次介绍进程相关的系统调用:

fork()函数 创建一个子进程

#include /* 提供类型pid_t的定义 */

#include /* 提供函数的定义...

altium designer怎么在原理图中批量修改元件封装

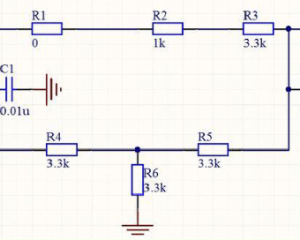

如图中,所有3.3k电阻封装为0603,想改为0805.

在altium designer中,直接选择3.3k右键找相同项,则没有封装信息可以修改

因此这里必须直接选择这些元件体,用鼠标+shift键一个个选中;

然后右键找相同目标

...

[Ground]模拟地与数字地

问题描述:PCB布线中模拟地和数字地的划分对硬件性能影响很大,特别使用了AD等一些敏感元件时。做整理如下:一、形成干扰的基本要素: 1.

干扰源

指产生干扰的元件、设备或信号,用数学语言描述如下:du/dt,di/dt大的地方就是干扰源。如:雷电、继电器、可...

OrCAD导出逻辑网表时无法生成netrev.lst文件

最近通过OrCAD导出网表画PCB时,发现Allegro 在导入网表时提示找不到netrev.lst,然后在生成网表的路径下面去找netrev.lst文件时,文件要嘛不存在,要嘛容量为 0KB。这个时候我怀疑ALlegro下面的netrev.exe应用程序出了问题,生成不了netrev.lst。然后到...

如何为Altium Designer 建立SvnDbLib

SVNDbLib 采用MySQL ODBC连接元器件库主库,通过SVN Http协议连接符号库文件以及封装文件。1. 服务器端:建立MySQL元器件库主库2. 服务器端:为符号库文件和封装文件建库在不同的子目录SchLibraries, PcbLibraries Footprint Path, Schematic Path 两列没什么...

PCB设计中元器件图与封装设计的一些事项

问题描述:设计出的PCB功能可以实现是一个层次,而美观,易于焊接人员焊接,排列整齐,易于连接,接口没有歧义等细节问题都考虑周到的话,电路板就是另一个层次了。下面的内容将记录设计过程中的元器件图与封装的一些注意事项,并慢慢积累,不断进行更新。

...

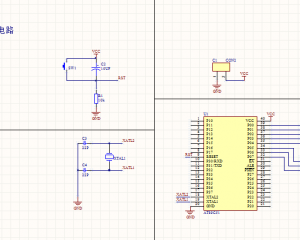

PCB-从零开始

只是一个初学者的一些总结感想。 今天算是第一天让我真正感受到我是嵌入式专业的学生,从一块电路板开始,从零开始。看似忙忙碌碌的一天天,还不如学到一点东西来的实惠。 我在慢慢靠近我喜欢的东西,我感到很兴奋。 其中最基础的是四个模块,主电路,复位电...

PCB设计中的电源信号完整性的考虑

在电路设计中,一般我们很关心信号的质量问题,但有时我们往往局限在信号线上进行研究,而把电源和地当成理想的情况来处理,虽然这样做能使问题简化,但在高速设计中,这种简化已经是行不通的了。尽管电路设计比较直接的结果是从信号完整性上表现出来的,但我...

PCB设计中专业英译术语之综合词汇(基础介绍)

1. 板:board 2. 印制板:printed board 3. 印制电路:printed circuit 4. 印制线路:printed wiring 5. 印制线路板:printed wiring board(PWB) 6. 印制板电路:printed circuit board (PCB) 7. 印制接点:printed contact 8. 印制组件...

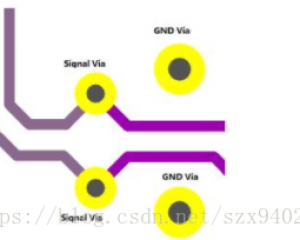

PCB设计处理原则

通用的高速信号PCB设计处理原则有:(1)层面的选择:处理高速信号优先选择两边是GND的层面处理(2)处理时要优先考虑高速信号的总长(3)高速信号Via数量的限制:高速信号允许换一次层,换层时加GND VIA如图:(4)如果高速信号在连接器有一端信号没有与GND ...