本帖最后由 flwjn 于 2019-3-22 13:29 编辑

最近在用F407,事事不顺。

刚搞定时钟,又遇到原来的GPIO位操作头文件不能用了的问题。

发现GPIO寄存器里,比F103少了个BRR。

偷懒,找了个现成的头文件用。说实话,并没看懂。

所以,实测了一下,感觉有点诡异。

突然有了兴致。

先用F407的BSRR重新定义了头文件。

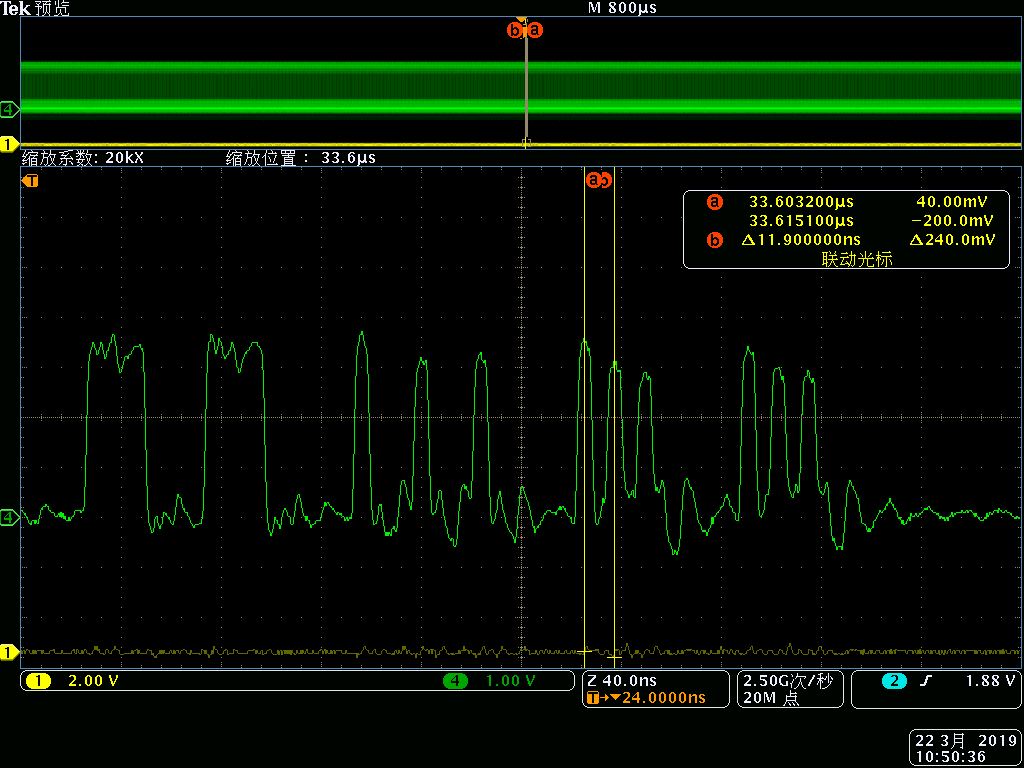

测试却发现,高低电平的保持时间不一致。

强迫症表示不能接受。。

测了下,电平的保持时间刚好是2倍关系。

感觉是和数据的位数有关系。

看了下资料,GPIO 寄存器8位、16位、32位都可以操作。

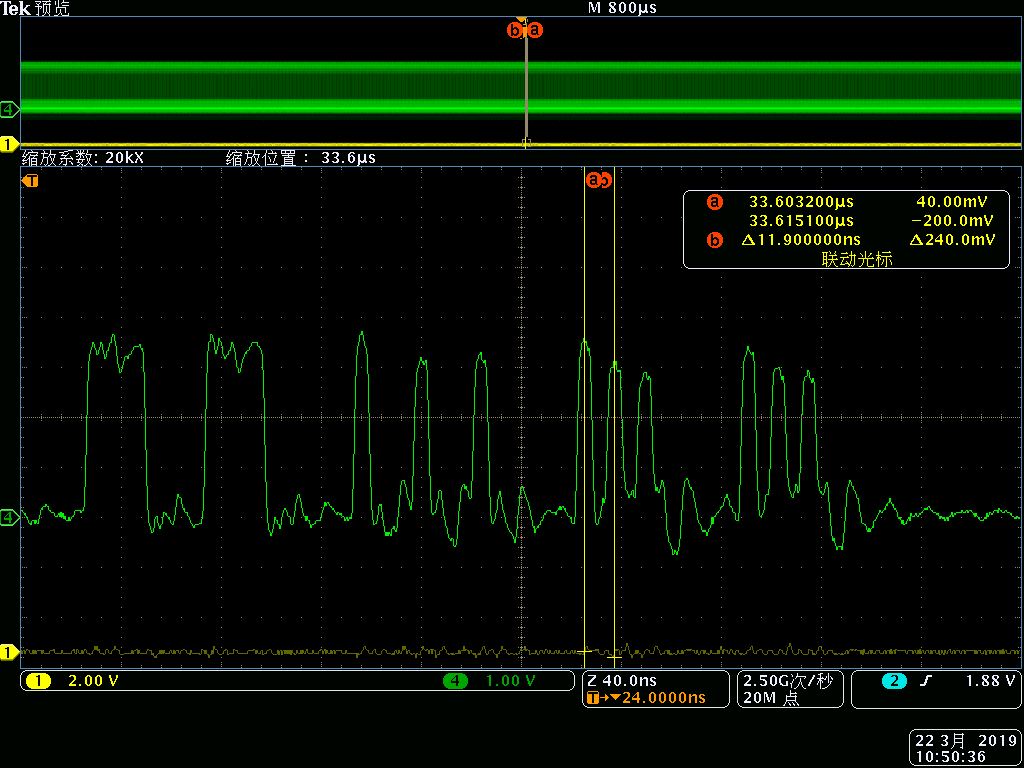

重定义了一下寄存器的地址。将BSRR(32位)一分为二:BSR(16位)和BRR(16位)。

这次得到了,想要的结果。

不过,我就想啊,如果进行8位的操作,IO的翻转是不是能更快。

然后就又定义了一下,分成:

BSRH、BSRL、BRRH、BRRL

测试结果,和16位的操作一样。

个人比较偏实践,理论不足。

就感觉上,这像是个16位单片机,兼容8位操作,但实际是16位操作。所以8位和16位的操作速度是一样的。

在进行32位操作时,其实是进行了2次16位操作,所以会比16位操作多用1倍的时间。

当然,也许内核是32位的,但由于某个瓶颈造成的表现。

*测试程序和波形。PA8引脚,GP PP SP100.

3组

1组

展开

最近在用F407,事事不顺。

刚搞定时钟,又遇到原来的GPIO位操作头文件不能用了的问题。

发现GPIO寄存器里,比F103少了个BRR。

偷懒,找了个现成的头文件用。说实话,并没看懂。

所以,实测了一下,感觉有点诡异。

突然有了兴致。

先用F407的BSRR重新定义了头文件。

测试却发现,高低电平的保持时间不一致。

强迫症表示不能接受。。

测了下,电平的保持时间刚好是2倍关系。

感觉是和数据的位数有关系。

看了下资料,GPIO 寄存器8位、16位、32位都可以操作。

重定义了一下寄存器的地址。将BSRR(32位)一分为二:BSR(16位)和BRR(16位)。

这次得到了,想要的结果。

不过,我就想啊,如果进行8位的操作,IO的翻转是不是能更快。

然后就又定义了一下,分成:

BSRH、BSRL、BRRH、BRRL

测试结果,和16位的操作一样。

个人比较偏实践,理论不足。

就感觉上,这像是个16位单片机,兼容8位操作,但实际是16位操作。所以8位和16位的操作速度是一样的。

在进行32位操作时,其实是进行了2次16位操作,所以会比16位操作多用1倍的时间。

当然,也许内核是32位的,但由于某个瓶颈造成的表现。

*测试程序和波形。PA8引脚,GP PP SP100.

3组

1组

展开

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

我猜你是的编译器的优化级别是设为0了, 其实这跟你说到的无关, 主要是ARM的立即数只是8位, 超过8位的就要用LDR(可以打开反汇编查看), 多了一指令周期, 所以你发现高低电平时间不一

你可以定义两个局部变量, 加register关键字, 分别把(1<<0)和(1<<8)赋值给这两变量, 然后用此两变量赋值给BSRR, 就不会有高低电平时间不一的问题了, 试试

好主意哦,我先去找指令集看看。仿真好像能看到汇编,再对照一下指令周期。

一周热门 更多>