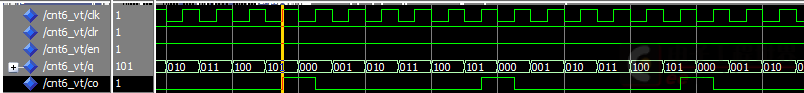

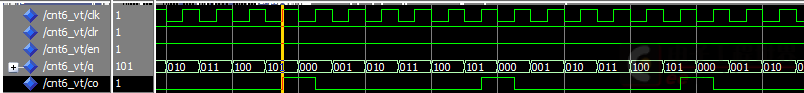

1、Cnt_6的VHDL源代码如下:library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; entity cnt6 is port (clr,en,clk :in std_logic; q :out std_logic_vector(2 downto 0); co :out std_logic ); end entity cnt6; architecture rtl of cnt6 is signal tmp :std_logic_vector(2 downto 0); begin process(clk) begin if (clr='0') then tmp<="000"; co<='0'; elsif (rising_edge(clk))then if(en='1') then if(tmp="101")then tmp<="000"; co<='1'; else tmp<=tmp+1;co<='0'; end if; end if; end if; q<=tmp; end process; end rtl; 2、Cnt_6的testbench代码如下: LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY cnt6_vt ISEND cnt6_vt;ARCHITECTURE cnt6_arch OF cnt6_vt IS-- constants -- signals SIGNAL clk : STD_LOGIC:='0';SIGNAL clr : STD_LOGIC:='0';SIGNAL en : STD_LOGIC:='0';SIGNAL q : STD_LOGIC_VECTOR(2 DOWNTO 0);SIGNAL co: STD_LOGIC:='0';CONSTANT clk_period :time :=100 ns; COMPONENT cnt6 port (clr,en,clk :in std_logic; q :out std_logic_vector(2 downto 0); co :out std_logic ); END COMPONENT;BEGIN i1 : cnt6 PORT MAP (-- list connections between master ports and signals clk => clk, clr => clr, en => en, q => q, co=>co ); clk_gen:process begin wait for clk_period/2; clk<='1'; wait for clk_period/2; clk<='0'; end process; clr_gen:process begin clr<='0'; wait for 30 ns; clr<='1'; wait; end process; en_gen:process begin en<='0'; wait for 50 ns; en<='1'; wait; end process; END cnt6_arch; 3、Modelism中的仿真波形如下图所示:

modelsim仿真波形

由波形可见,进位信号是上升沿触发的,计数结果确实下降沿触发的,不知道是什么原因?请各位大侠指点,多谢!!!

modelsim版本是6.4a

此帖出自小平头技术问答

modelsim版本是6.4a

此帖出自小平头技术问答

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

1、你仿真结果里没发现temp,可以试着仿真的时候把temp显示出来看看

2、q <=temp;这个赋值要么放进程外,要么时钟打一拍赋值,再看看结果

一周热门 更多>