本帖最后由 wsmysyn 于 2018-7-29 10:09 编辑

如题:

最近在调试FPGA,需要把代码烧到Flash中;但是遇到jic文件下载成功但是FPGA加载过程一直停不下来,程序也不运行

目标芯片:EP4CE10F17C8;BGA封装

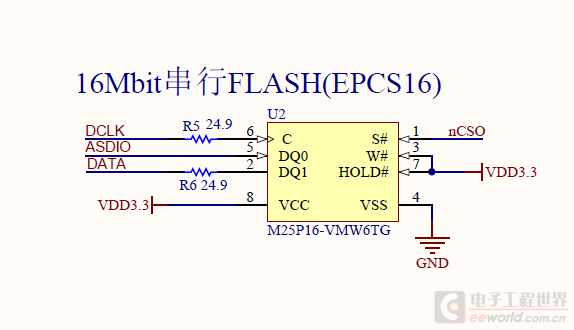

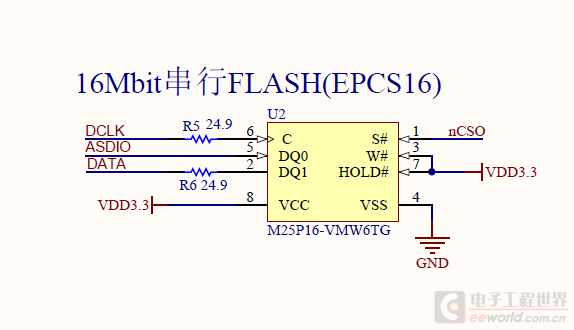

Flash:EPCS16,或兼容型号

quartus版本:18.0/17.0

背景:

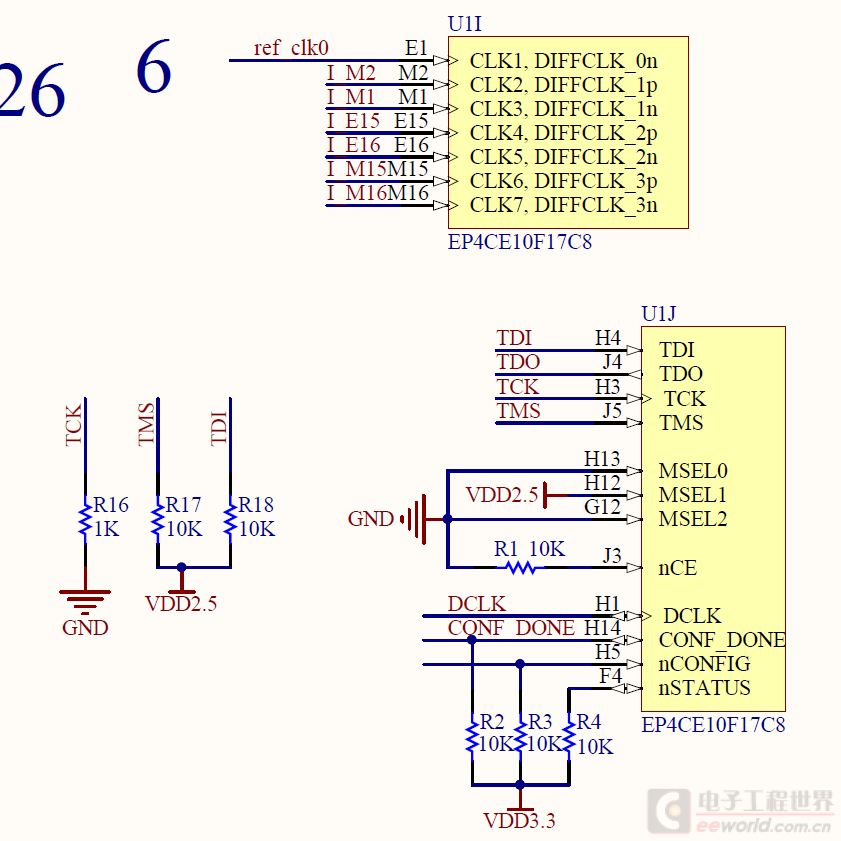

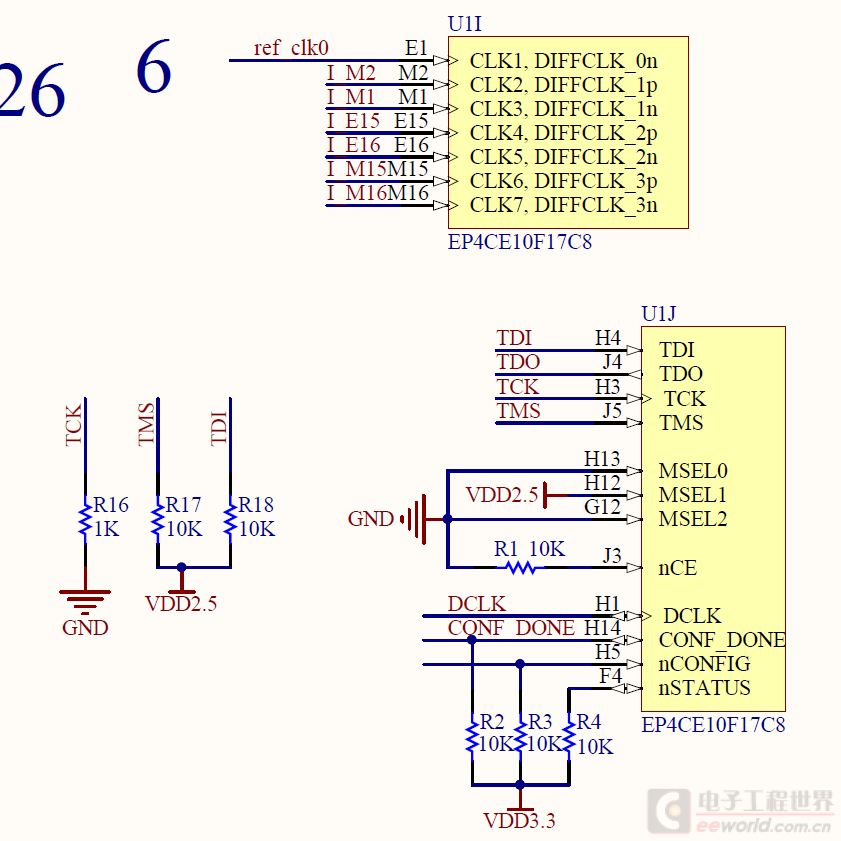

1、FPGA的核心板是买的现成的模块,接口只留了jtag接口,AS接口并没有预留;核心板上配置EPCS16的flash

2、现成的FPGA模块通过排针插在自己画的地板上使用;

3、平时调试的时候都是下载sof文件,逻辑功能正常

4、将sof转换成jic文件烧写flash之后,选择verify,和 config,提示成功;拔掉jtag,重新上电;发现config_done管脚一直为低;FPGA没有运行起来;

5、同样在quartus 18.0版本下,基于以前的EP4CE6E22C8开发板,flash型号同样是EPCS16, 下载sof和jic的文件都是正常的;

尝试:

1、各个电源都有确认,是正常的

2、重新上电后,测量SPI flash的管脚,发现DCLK、ASDIO、DATA管脚一直有信号,在动作;DCLK是33MHz的方波;

所以FPGA一直没有加载完??持续几分钟一直都这样子;所谓的被卡住了?

3、更换EP4CE6E22C8的开发板上验证OK的flash;同样也是上述问题;

4、写了一个很小的点灯程序,只用到两个管脚;下载sof文件正常,下载jic文件同样的问题;

5、quartus版本之前一直在18.0版本,后来使用17.0版本重新编译工程,转换jic文件;下载问题依旧

6、更换FPGA核心板,问题依旧;

7、查看过MSEL[2:0]的配置方式;CE10F17的板子是010方式,“1”是2.5V;

我自己画过的一个板子CE6E22的上边用的是101方式,“1”是3.3V

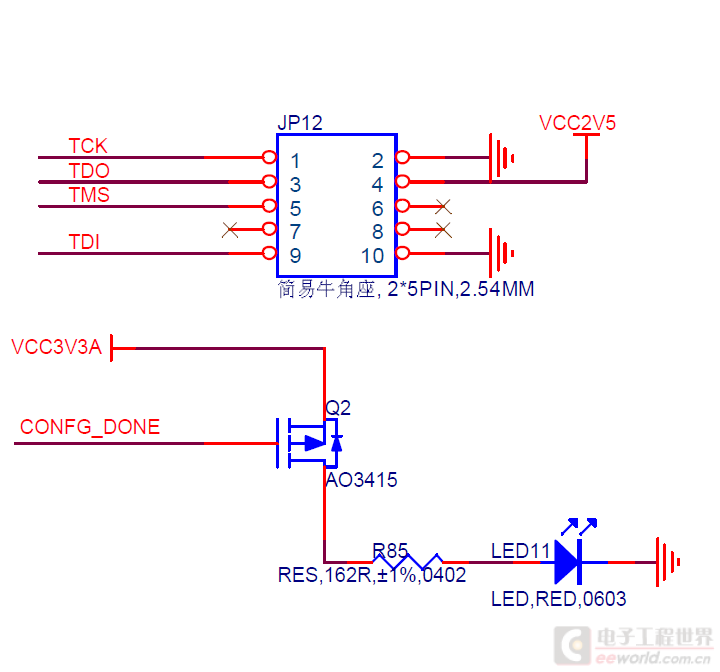

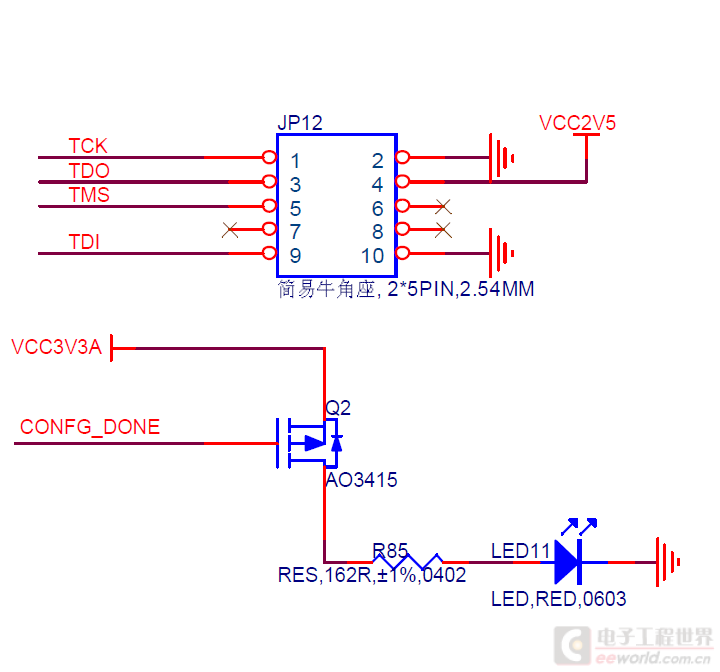

其他专用管脚比如TMS,TDI,TDO,TCK,config_done,nStatus,等都是和以前ok的板子同样处理方式;

问题:

1、大家还有什么意见么?有遇到过相同问题的童鞋么?

是怎么解决的?

已经头疼了

2、现在的怀疑有几点,但是还没验证,或者暂时没办法验证

A:MSEL的配置方式是否有影响,起码和我之前做的EP4CE6的那个开发板设置方式不一样;不过不确认是否有影响

B:走线过长(大概最长10cm),有信号完整性问题?还没有验证;

C:FPGA本身有问题

D:底板设计有问题

E:另外下载器是兼容系列不是原装的;手里有几个其他版本可以试一下

F:其他没有注意到的地方

附件:

成品FPGA核心板模块flash和jtag部分的设置;感觉应该没问题

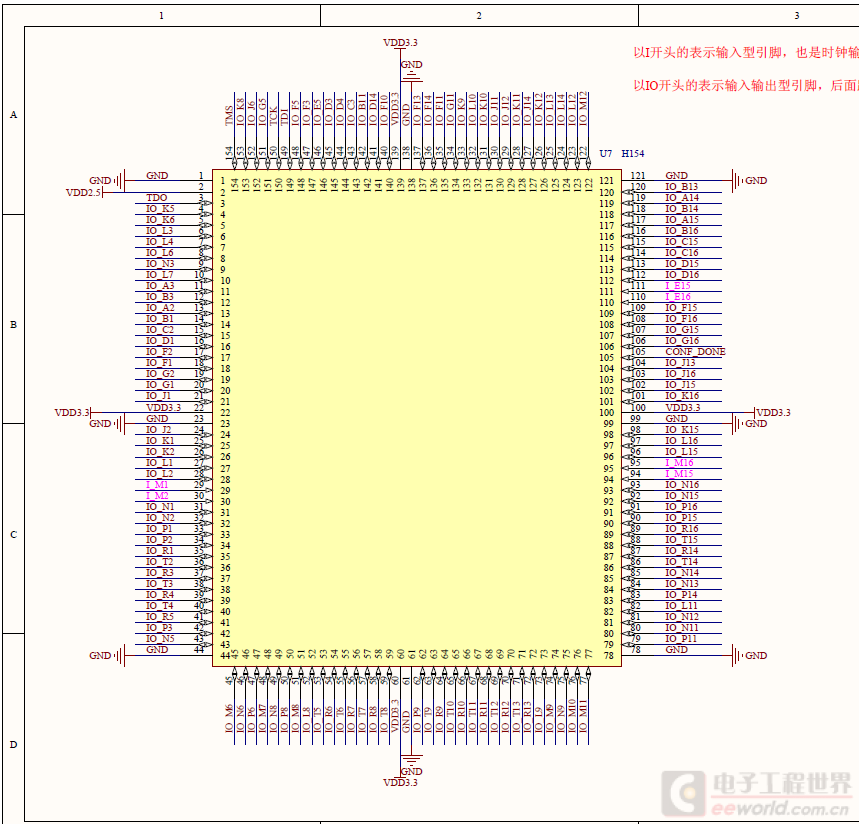

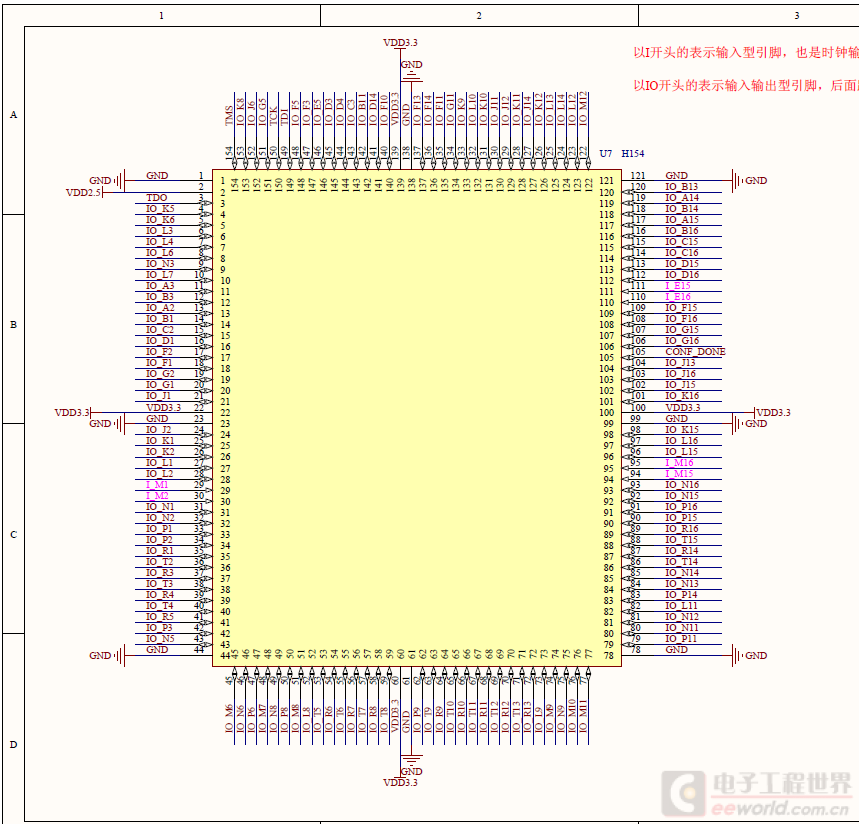

核心板IO位置图

底板jtag部分的原理图

此帖出自小平头技术问答

如题:

最近在调试FPGA,需要把代码烧到Flash中;但是遇到jic文件下载成功但是FPGA加载过程一直停不下来,程序也不运行

目标芯片:EP4CE10F17C8;BGA封装

Flash:EPCS16,或兼容型号

quartus版本:18.0/17.0

背景:

1、FPGA的核心板是买的现成的模块,接口只留了jtag接口,AS接口并没有预留;核心板上配置EPCS16的flash

2、现成的FPGA模块通过排针插在自己画的地板上使用;

3、平时调试的时候都是下载sof文件,逻辑功能正常

4、将sof转换成jic文件烧写flash之后,选择verify,和 config,提示成功;拔掉jtag,重新上电;发现config_done管脚一直为低;FPGA没有运行起来;

5、同样在quartus 18.0版本下,基于以前的EP4CE6E22C8开发板,flash型号同样是EPCS16, 下载sof和jic的文件都是正常的;

尝试:

1、各个电源都有确认,是正常的

2、重新上电后,测量SPI flash的管脚,发现DCLK、ASDIO、DATA管脚一直有信号,在动作;DCLK是33MHz的方波;

所以FPGA一直没有加载完??持续几分钟一直都这样子;所谓的被卡住了?

3、更换EP4CE6E22C8的开发板上验证OK的flash;同样也是上述问题;

4、写了一个很小的点灯程序,只用到两个管脚;下载sof文件正常,下载jic文件同样的问题;

5、quartus版本之前一直在18.0版本,后来使用17.0版本重新编译工程,转换jic文件;下载问题依旧

6、更换FPGA核心板,问题依旧;

7、查看过MSEL[2:0]的配置方式;CE10F17的板子是010方式,“1”是2.5V;

我自己画过的一个板子CE6E22的上边用的是101方式,“1”是3.3V

其他专用管脚比如TMS,TDI,TDO,TCK,config_done,nStatus,等都是和以前ok的板子同样处理方式;

问题:

1、大家还有什么意见么?有遇到过相同问题的童鞋么?

是怎么解决的?

已经头疼了

2、现在的怀疑有几点,但是还没验证,或者暂时没办法验证

A:MSEL的配置方式是否有影响,起码和我之前做的EP4CE6的那个开发板设置方式不一样;不过不确认是否有影响

B:走线过长(大概最长10cm),有信号完整性问题?还没有验证;

C:FPGA本身有问题

D:底板设计有问题

E:另外下载器是兼容系列不是原装的;手里有几个其他版本可以试一下

F:其他没有注意到的地方

附件:

成品FPGA核心板模块flash和jtag部分的设置;感觉应该没问题

核心板IO位置图

底板jtag部分的原理图

此帖出自小平头技术问答

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

MSEL2..0 = 010 没有问题,"1" 是接2.5V的VCCA

"3、更换EP4CE6E22C8的开发板上验证OK的flash;同样也是上述问题;"

在OK的板子上把 jic 下进去,再焊到新板子上来看看? 以及在新板子上下一个 jic, 再焊到旧板子上去看能否配置。

ok的板子上烧写jic之后换到新板子这个有试过,问题是一样的;

换回去没试过,可以试一下

现在看来还可以有两个操作可以试一下

1、下载器更换其他型号的试一下;手里现在有3种下载器,可以每个都试一下

2、新板子烧写,换到旧板子上

另外也找了卖家,他们给寄了一套新的,说让试一试。看周一什么结果了

核心板是1.27的排针引出的,暂时不方便单独调试

不过已经解决问题了,见楼下。

一周热门 更多>