我想仿真一个分频系数是12的分频器。

代码如下:

module div12(fm,clk);

output fm;

input clk;

reg fm;

reg[2:0] cnt=3'b000;

always @(posedge clk)

begin

if(cnt==3'b101)

begin fm <= ~fm;cnt<=0;end

else

begin cnt<=cnt+1;end

end

endmodule

testbench文件为:

`timescale 1ns/1ns

module div12_testbench;

wire fm=0;

reg clk=0;

div12 div12(fm,clk);

always

#10 clk=~clk;

endmodule

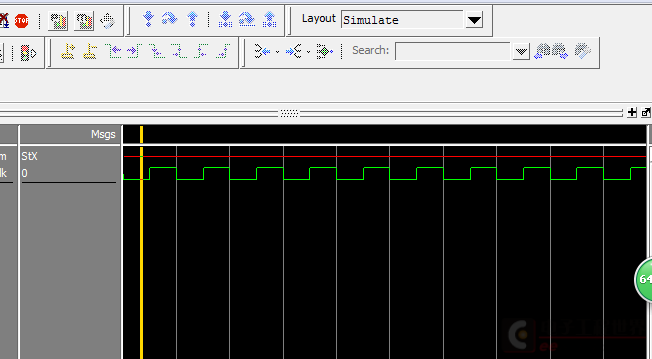

仿真结果:

fm一直是一条红线。请问高手,怎么回事?如何解决?谢谢!

代码如下:

module div12(fm,clk);

output fm;

input clk;

reg fm;

reg[2:0] cnt=3'b000;

always @(posedge clk)

begin

if(cnt==3'b101)

begin fm <= ~fm;cnt<=0;end

else

begin cnt<=cnt+1;end

end

endmodule

testbench文件为:

`timescale 1ns/1ns

module div12_testbench;

wire fm=0;

reg clk=0;

div12 div12(fm,clk);

always

#10 clk=~clk;

endmodule

仿真结果:

fm一直是一条红线。请问高手,怎么回事?如何解决?谢谢!

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

module div12(fm,clk);

output fm;

input clk;

reg fm;

reg[2:0] cnt=3'b000;

always @(posedge clk)

begin

if(cnt==3'b101)

begin fm <= ~fm;cnt<=0;end

else

begin cnt<=cnt+1;end

end

endmodule

testbench文件为

`timescale 1ns/1ns

module div12_testbench;

wire fm=0;

reg clk=0;

div12 div12(fm,clk);

always

#10 clk=~clk;

endmodule

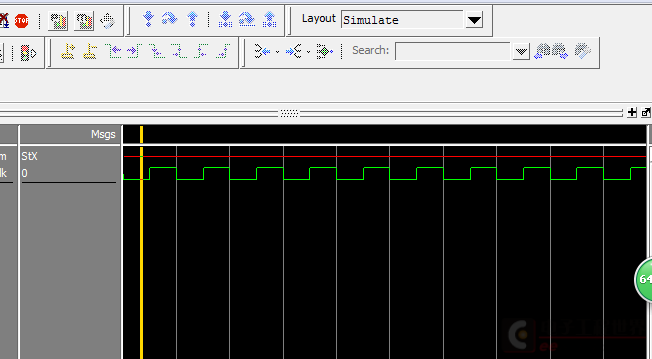

仿真结果为:

可是fm一直是一条红线。请问高手,为什么没有波形呢?谢谢!

①fm是输出,测试文件中不能给输出赋值

②源代码中fm没有初始值,fm不能进行翻转,仿真时显示为不定态更改:源代码fm=0 或者fm=1

一周热门 更多>