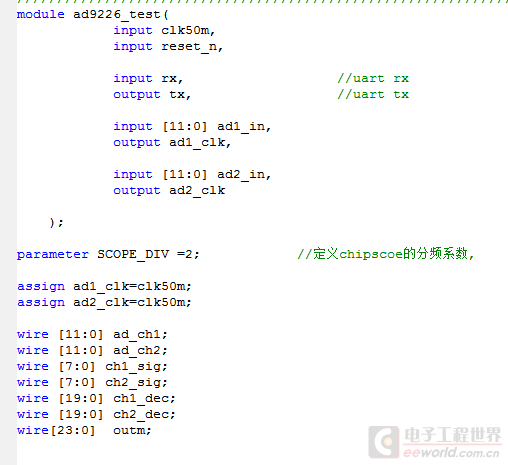

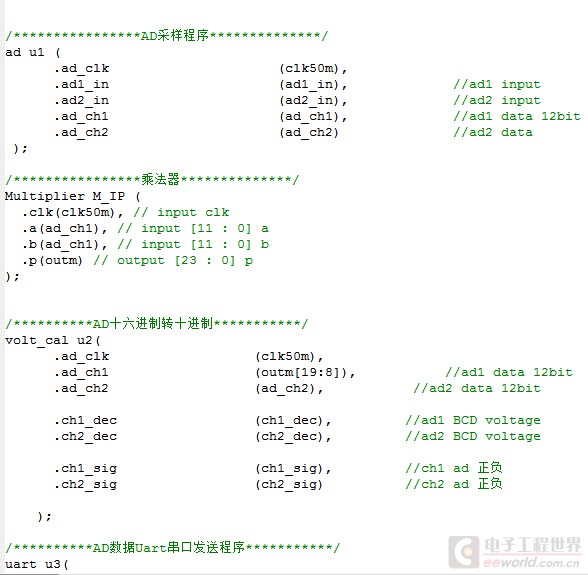

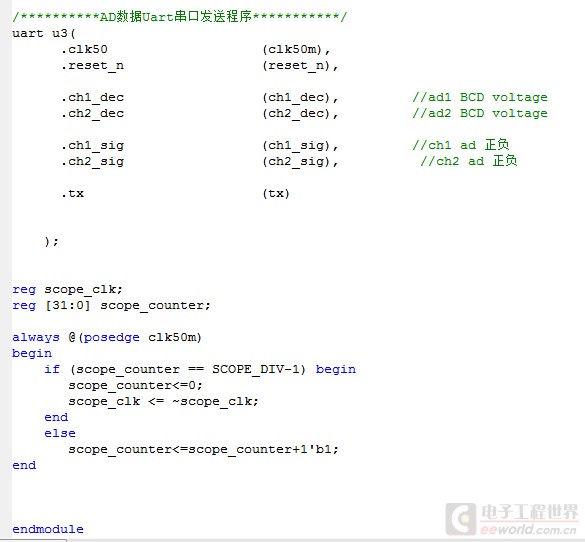

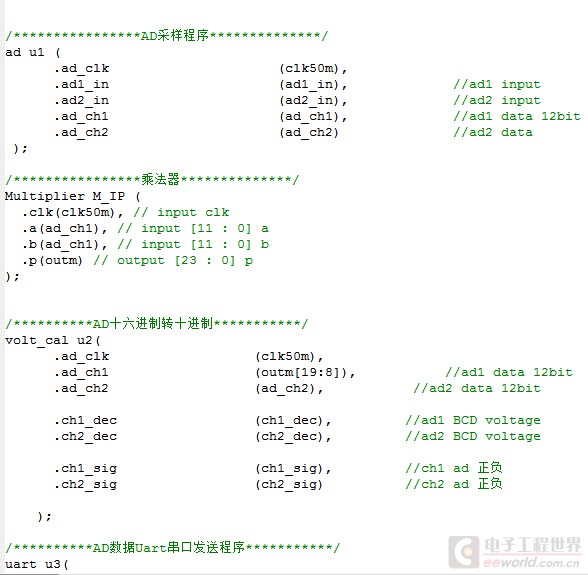

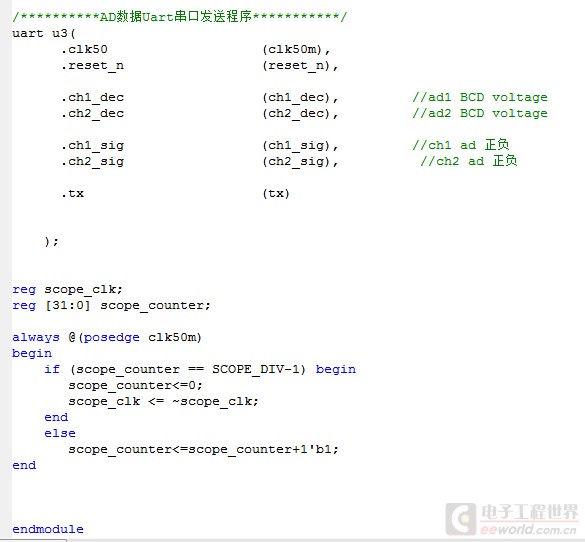

如题,AD程序是现成的,可以正常工作,乘法器我是用IP核做的,顶层文件如下面截图。输入信号我接的是信号发生器的1kHz,4Vpp(峰峰值,幅值为2V),我用乘法器做平方(所以输入都为ad_ch1),经过乘法器之后应该输出为4V,但是我通过串口小工具查看,输出峰值接近5V,不知为何,特来求助。

此帖出自小平头技术问答

此帖出自小平头技术问答

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

一周热门 更多>