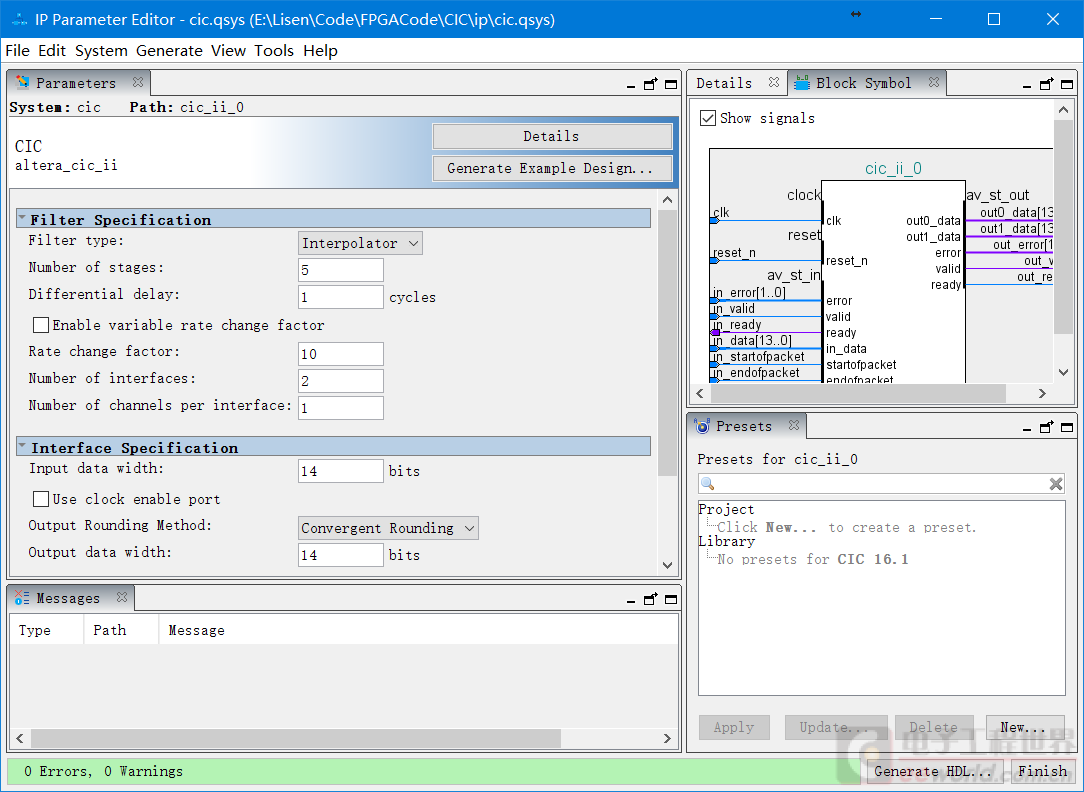

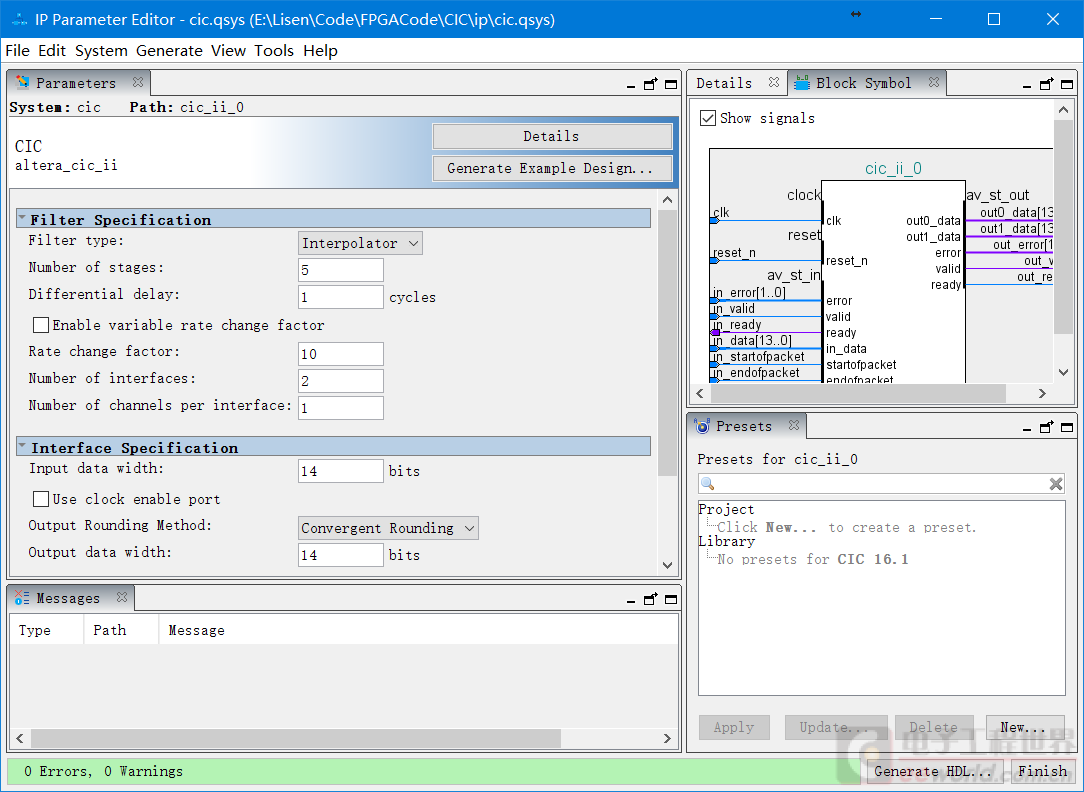

大家好!最近用Quartus的CIC IP核遇到一个问题,描述一下问题,如下图,CIC IP核的设置,主要是内插倍数是10,两接口输出。

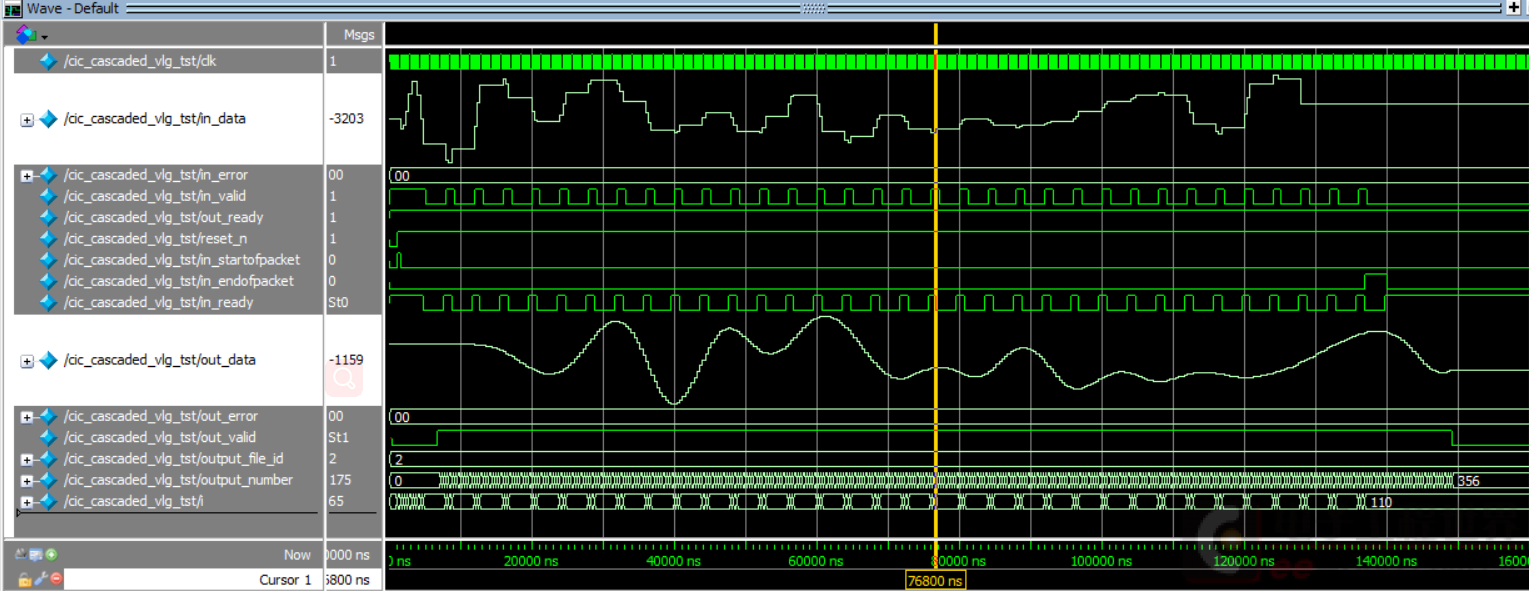

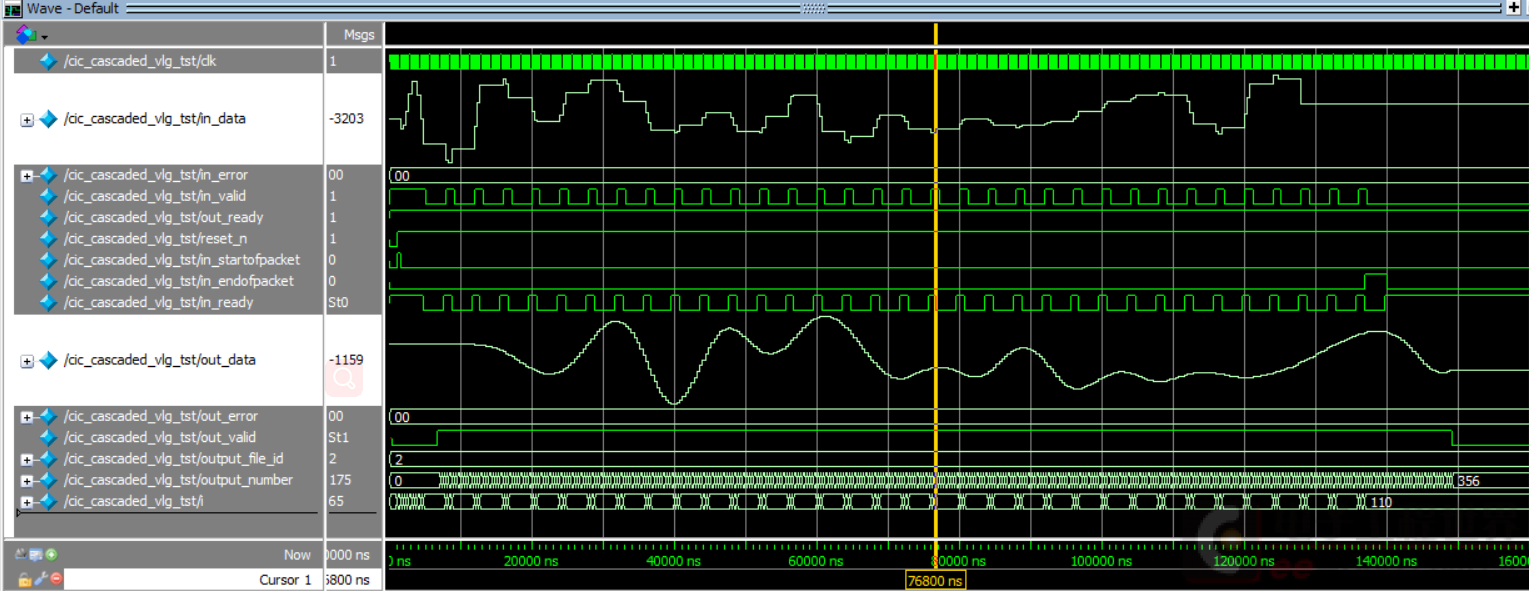

然后下图是仿真输出,可以看到输入输出波形,这里只显示了一路波形,那么这一路相对于输入采样率是5倍内插,i表示的是输入点数,output_number是输出点数。

那么问题就是,应该是5倍内插,为什么输出只有356个点?

仔细对比一下输入输出波形也可以看出,输出波形没有输入波形的最后一小段?

时序我也仔细检查过了,感觉没什么问题。

求大神指点迷津!感谢!

此帖出自小平头技术问答

然后下图是仿真输出,可以看到输入输出波形,这里只显示了一路波形,那么这一路相对于输入采样率是5倍内插,i表示的是输入点数,output_number是输出点数。

那么问题就是,应该是5倍内插,为什么输出只有356个点?

仔细对比一下输入输出波形也可以看出,输出波形没有输入波形的最后一小段?

时序我也仔细检查过了,感觉没什么问题。

求大神指点迷津!感谢!

此帖出自小平头技术问答

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

自己补充,在输入末端补零,可以得到最后一小段的内插结果,然后输出也是0。

但是,输出数据量依然达不到500,只有426!

然后在连续运行的情况下可以得到5倍的内插倍数的输出。

输出波形经matlab画图观察,还是很好的。

一周热门 更多>