比如我的testbench由 tb_bin_gen.v,

tb_bin_monitor.v

tb_bin_counter_top.v

三个verilog文件构成,其中tb_bin_counter_top.v是testbench的顶层文件。

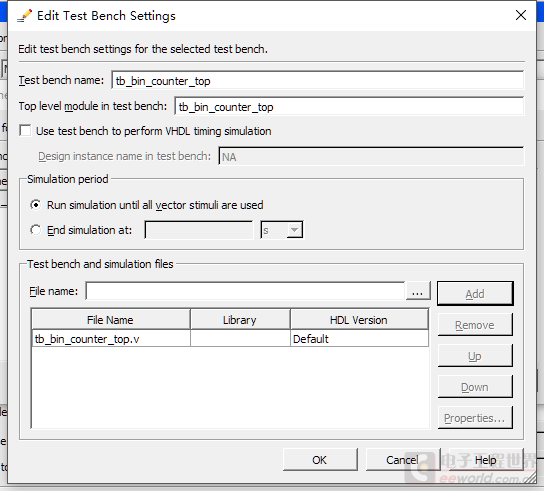

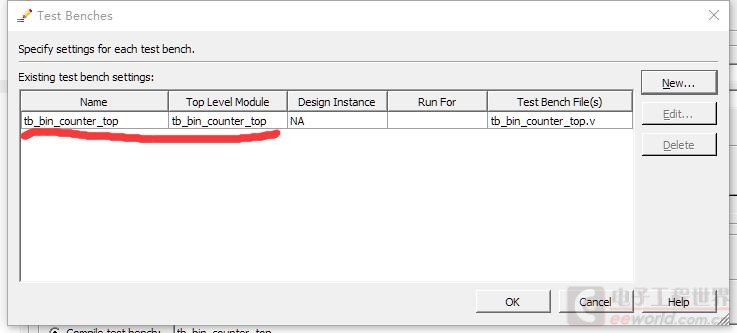

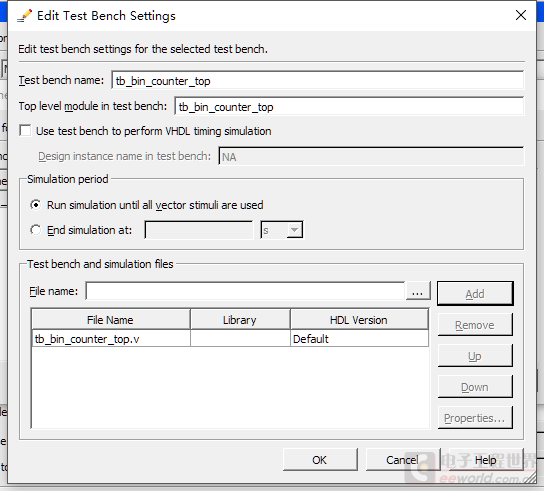

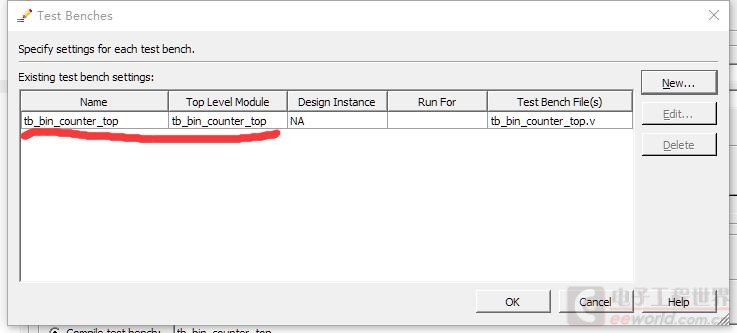

在Quartus II 的Setting页面中,找到Simuation 设置为ModelSim仿真,

然后在Compile test bench 添加 测试模块的顶层文件 tb_bin_counter_top.v

编译没有出错,然后从QuartusII 运行RTL 仿真,自动打开ModelSim之后,出现报错

** Error: C:/Users/Z/Desktop/FPGA_Test_Only/bin_counter/tb_bin_counter_top.v(41): Module 'tb_bin_gen' is not defined.

# ** Error: (vopt-7) Failed to open info file "work/_info" in read mode.

#

# No such file or directory. (errno = ENOENT)

# ** Error: C:/Users/Z/Desktop/FPGA_Test_Only/bin_counter/tb_bin_counter_top.v(59): Module 'tb_bin_monitor' is not defined.

# Optimization failed

# Error loading design

# Error: Error loading design

# Pausing macro execution

# MACRO ./univ_bin_counter_run_msim_rtl_verilog.do PAUSED at line 40

怎么解决呀?

此帖出自小平头技术问答

tb_bin_monitor.v

tb_bin_counter_top.v

三个verilog文件构成,其中tb_bin_counter_top.v是testbench的顶层文件。

在Quartus II 的Setting页面中,找到Simuation 设置为ModelSim仿真,

然后在Compile test bench 添加 测试模块的顶层文件 tb_bin_counter_top.v

编译没有出错,然后从QuartusII 运行RTL 仿真,自动打开ModelSim之后,出现报错

** Error: C:/Users/Z/Desktop/FPGA_Test_Only/bin_counter/tb_bin_counter_top.v(41): Module 'tb_bin_gen' is not defined.

# ** Error: (vopt-7) Failed to open info file "work/_info" in read mode.

#

# No such file or directory. (errno = ENOENT)

# ** Error: C:/Users/Z/Desktop/FPGA_Test_Only/bin_counter/tb_bin_counter_top.v(59): Module 'tb_bin_monitor' is not defined.

# Optimization failed

# Error loading design

# Error: Error loading design

# Pausing macro execution

# MACRO ./univ_bin_counter_run_msim_rtl_verilog.do PAUSED at line 40

怎么解决呀?

此帖出自小平头技术问答

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

解决了,非常感谢,还是第一次使用`include

不过使用include得把原来的子文件从工程中移除,否则会报错,

我还是想知道如果不用include 就将子文件添加到工程目录中,然后直接实例化,应该怎么操作呢

一周热门 更多>