各位大神,为什么我编的并串转换后会在每一个并行数据之间有一个低电平的无效数据。always@(posedge clk or negedge rst)begin if(!rst) begin count<=0; clkdiv<=0; end else begin count<=count+1; if(count==9) clkdiv<=~clkdiv; else if(count==19) begin clkdiv<=~clkdiv; count<=0; end endend

always@(posedge clk or negedge rst)begin if(!rst) begin pscen<=0; sdata<=0; state<=16; data_buf<=0; end else begin case(state) 16: begin pscen<=0; sdata<=0; data_buf<=data_in; state<=15; end 15: begin pscen<=1; sdata<=data_buf[15]; state<=14; end 14: begin pscen<=1; sdata<=data_buf[14]; state<=13; end 13: begin pscen<=1; sdata<=data_buf[13]; state<=12; end 12: begin pscen<=1; sdata<=data_buf[12]; state<=11; end 11: begin pscen<=1; sdata<=data_buf[11]; state<=10; end 10: begin pscen<=1; sdata<=data_buf[10]; state<=9; end 9: begin pscen<=1; sdata<=data_buf[9]; state<=8; end 8: begin pscen<=1; sdata<=data_buf[8]; state<=7; end 7: begin pscen<=1; sdata<=data_buf[7]; state<=6; end 6: begin pscen<=1; sdata<=data_buf[6]; state<=5; end 5: begin pscen<=1; sdata<=data_buf[5]; state<=4; end 4: begin pscen<=1; sdata<=data_buf[4]; state<=3; end 3: begin pscen<=1; sdata<=data_buf[3]; state<=2; end 2: begin pscen<=1; sdata<=data_buf[2]; state<=1; end 1: begin pscen<=1; sdata<=data_buf[1]; state<=0; end 0: begin pscen<=1; sdata<=data_buf[0]; state<=16; end default: begin pscen<=0; sdata<=0; state<=16; end endcase endend

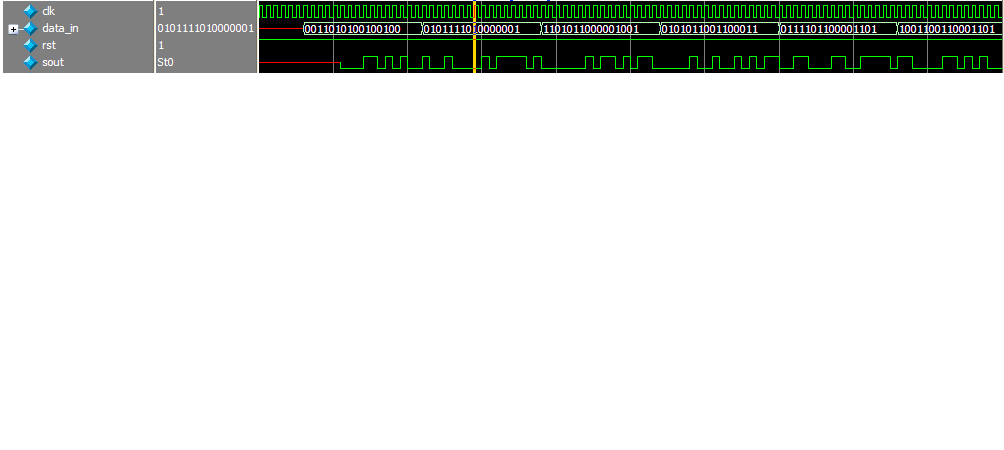

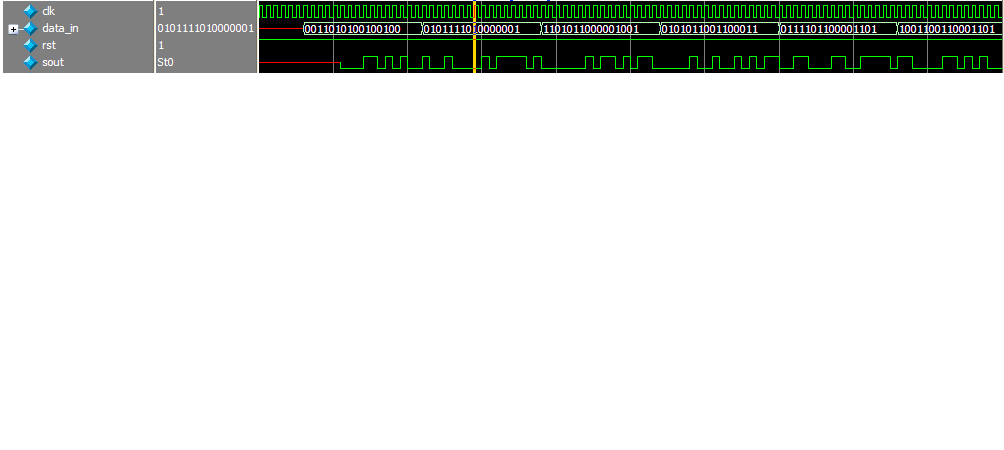

仿真图

此帖出自小平头技术问答

always@(posedge clk or negedge rst)begin if(!rst) begin pscen<=0; sdata<=0; state<=16; data_buf<=0; end else begin case(state) 16: begin pscen<=0; sdata<=0; data_buf<=data_in; state<=15; end 15: begin pscen<=1; sdata<=data_buf[15]; state<=14; end 14: begin pscen<=1; sdata<=data_buf[14]; state<=13; end 13: begin pscen<=1; sdata<=data_buf[13]; state<=12; end 12: begin pscen<=1; sdata<=data_buf[12]; state<=11; end 11: begin pscen<=1; sdata<=data_buf[11]; state<=10; end 10: begin pscen<=1; sdata<=data_buf[10]; state<=9; end 9: begin pscen<=1; sdata<=data_buf[9]; state<=8; end 8: begin pscen<=1; sdata<=data_buf[8]; state<=7; end 7: begin pscen<=1; sdata<=data_buf[7]; state<=6; end 6: begin pscen<=1; sdata<=data_buf[6]; state<=5; end 5: begin pscen<=1; sdata<=data_buf[5]; state<=4; end 4: begin pscen<=1; sdata<=data_buf[4]; state<=3; end 3: begin pscen<=1; sdata<=data_buf[3]; state<=2; end 2: begin pscen<=1; sdata<=data_buf[2]; state<=1; end 1: begin pscen<=1; sdata<=data_buf[1]; state<=0; end 0: begin pscen<=1; sdata<=data_buf[0]; state<=16; end default: begin pscen<=0; sdata<=0; state<=16; end endcase endend

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

一个数据时钟也是 16 个clk, 输了我 4遍

可 你的state 状态 是 0 到 16, 多了一个

state16是表示让data_in数据输入到数据缓存data_buf中,我尝试过把这个过程拿到case语句外面,可是那样会造成转换的错码和丢码的现象。。所以我就在case里面多加了已个状态。。。

if (load )

shift_req <= 16 bit 初期值

else (shift enable)

shift_req <= {0, shift_req[15:1]};

不过哥,我还是有点强迫症晚期的提醒一下,else后面不能接条件语句,应该用else if

一周热门 更多>