我要在FPGA中做数字正交,故此要用到DDS IP核,5.0版本的,但是研究了两天始终无法产生比较满意的正玄波,用ChipScope采到的波形要不是就是像下图这种,要不就是一些比较混乱的,反正不是比较正常的正玄波。

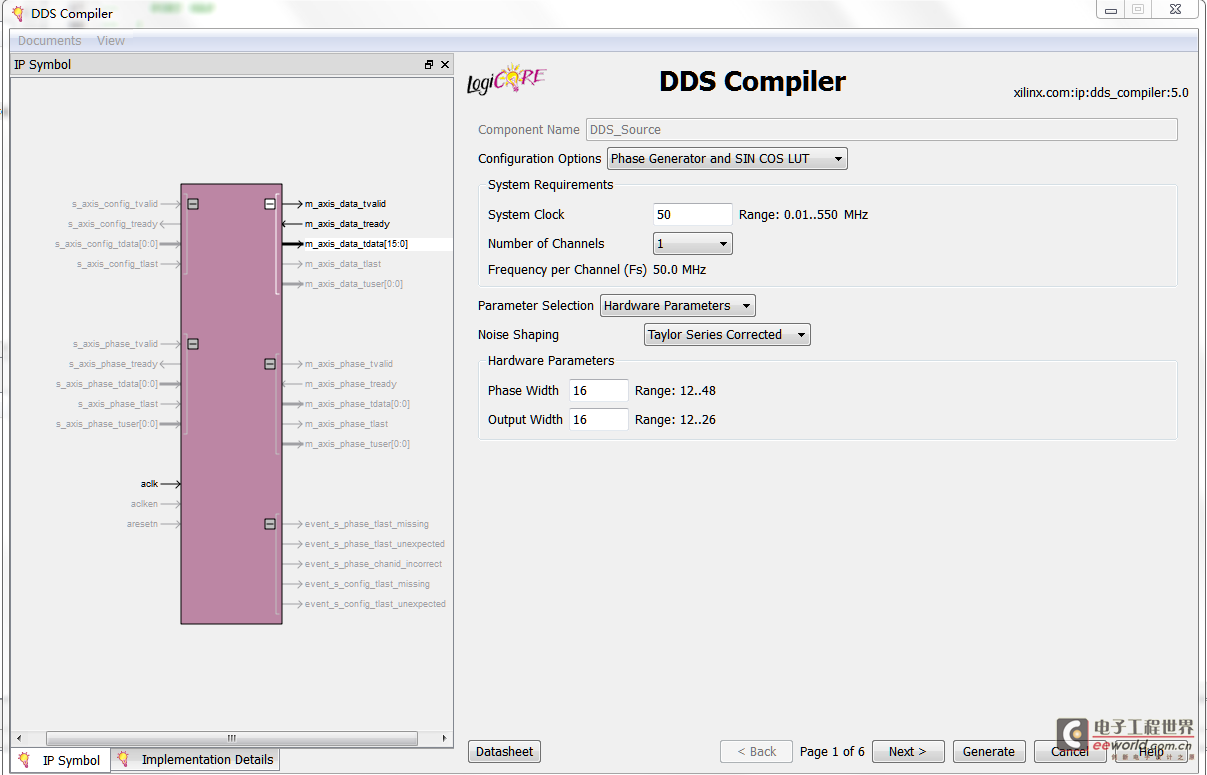

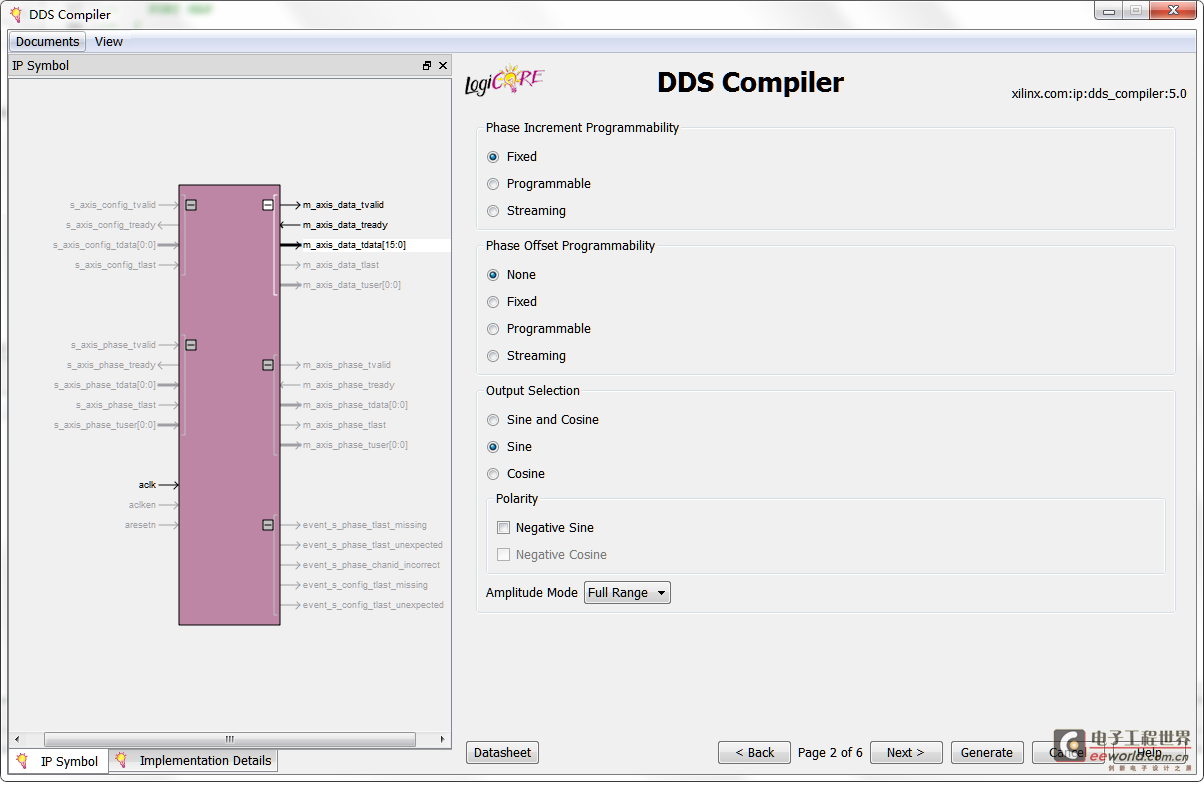

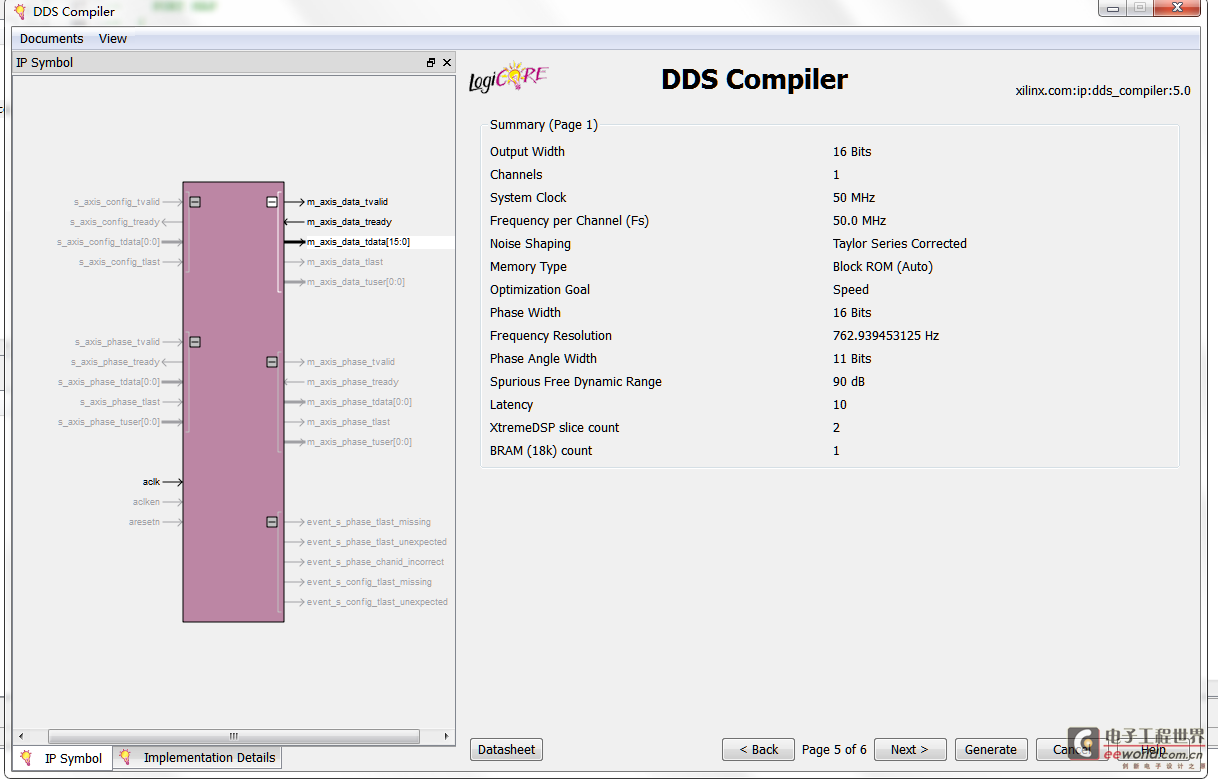

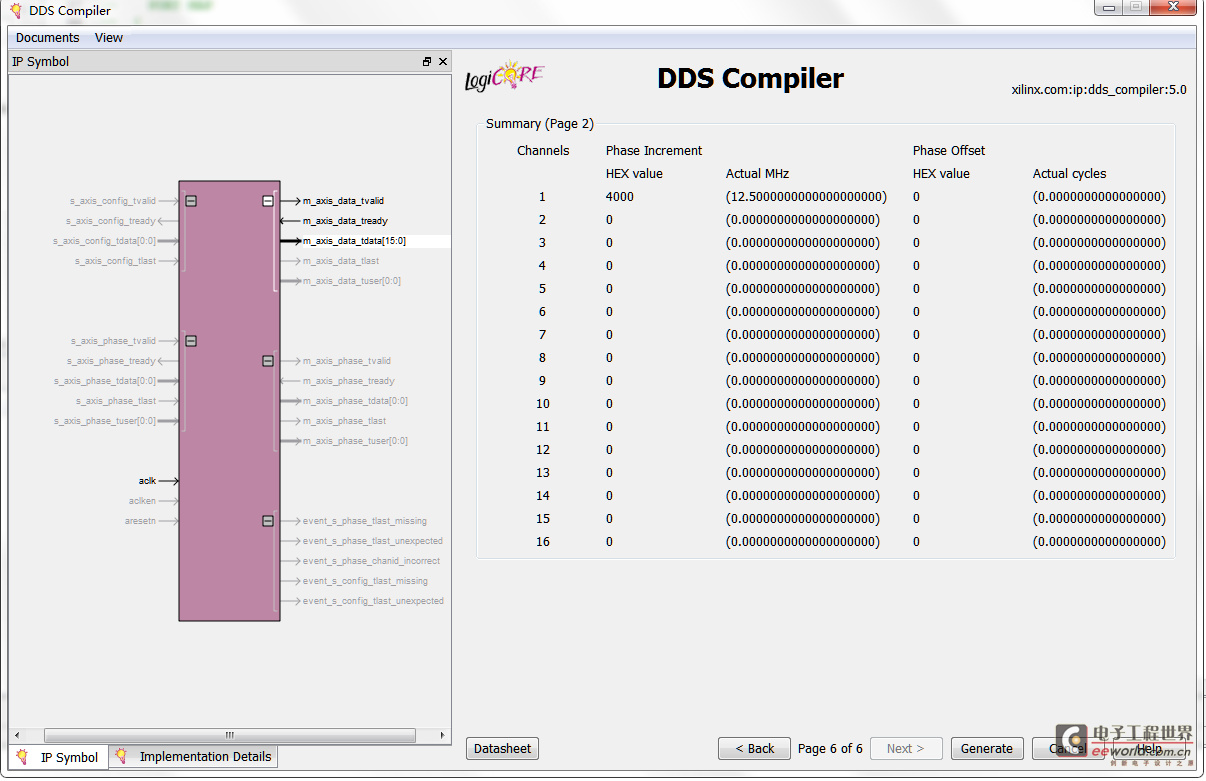

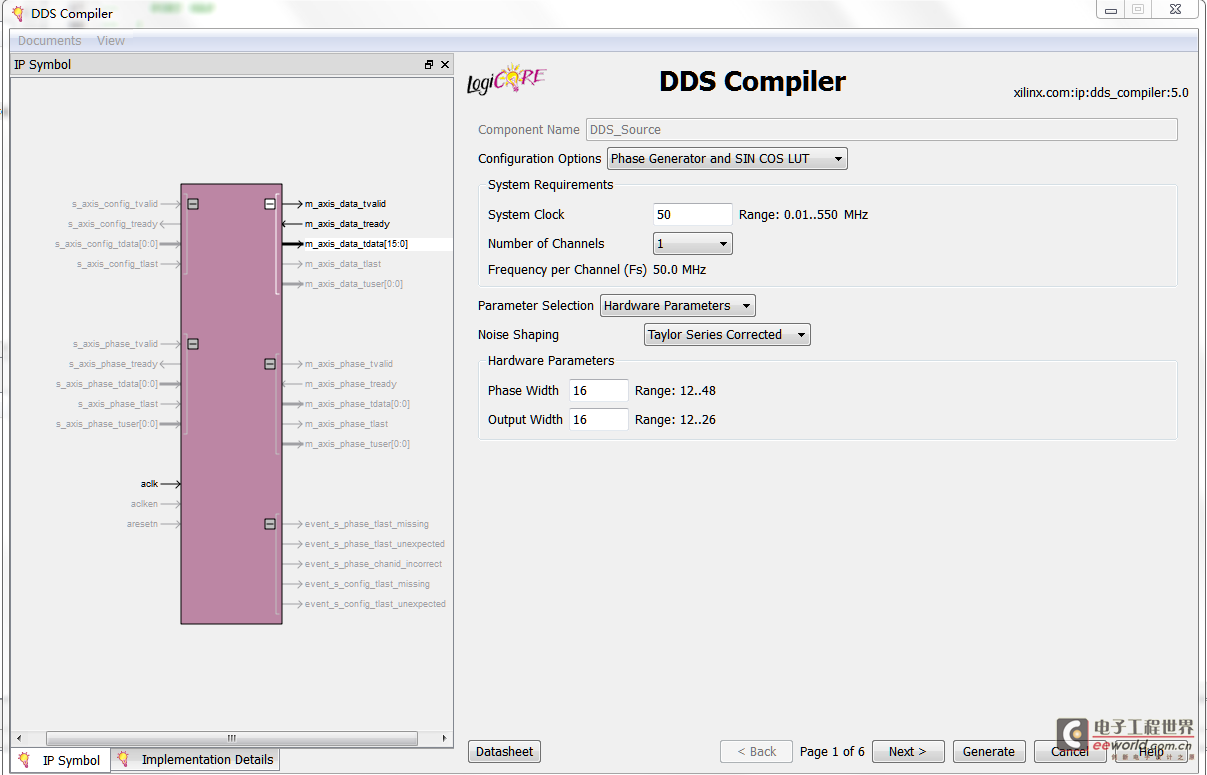

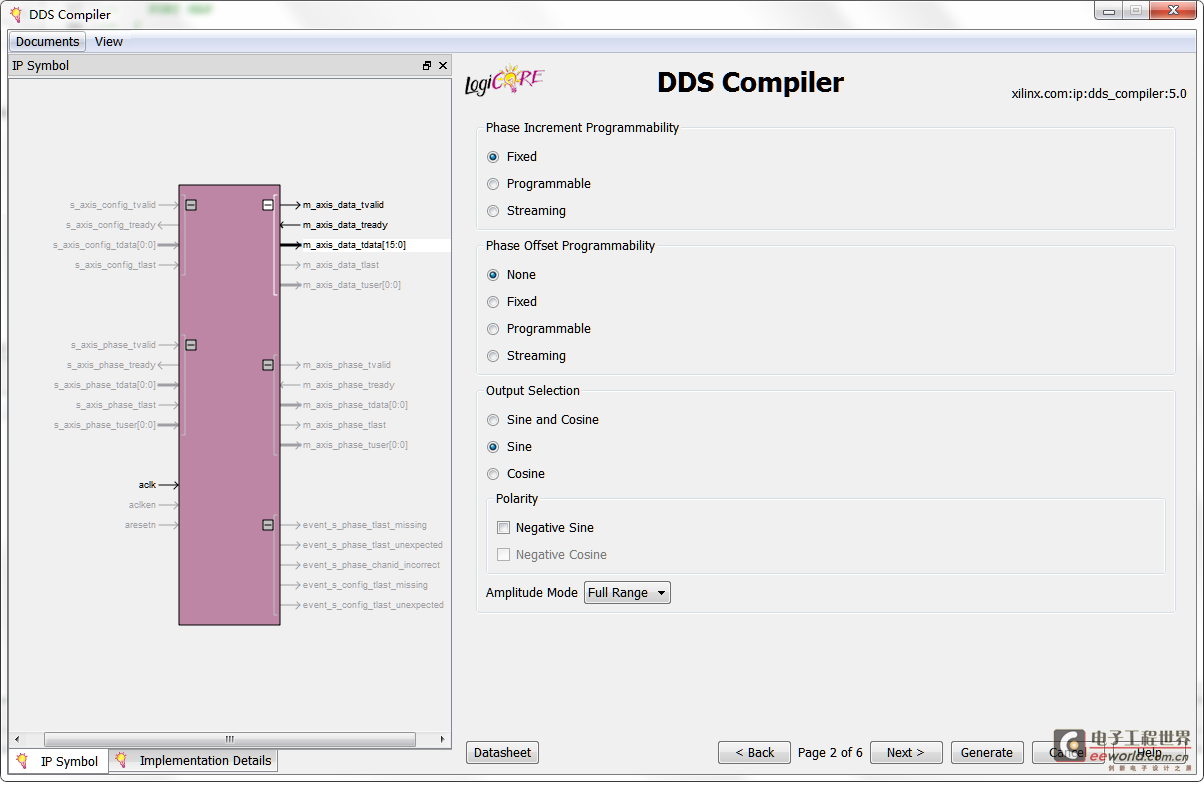

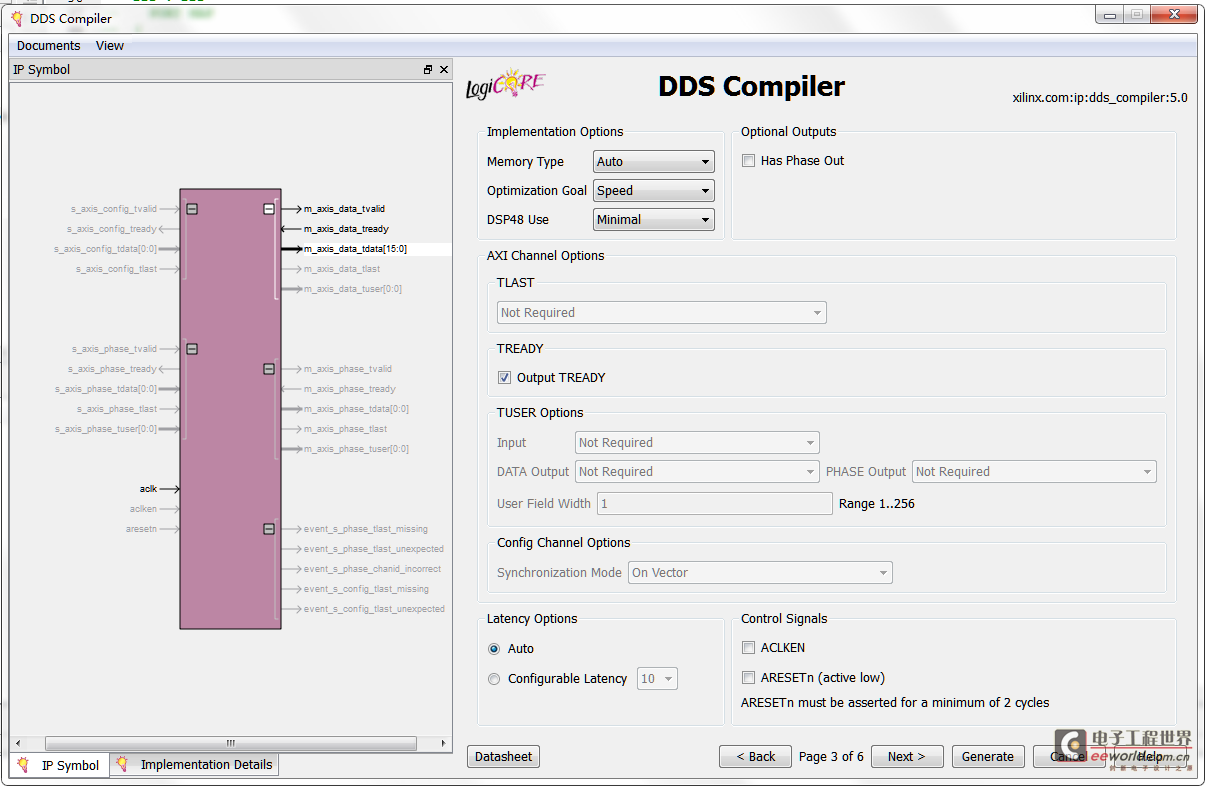

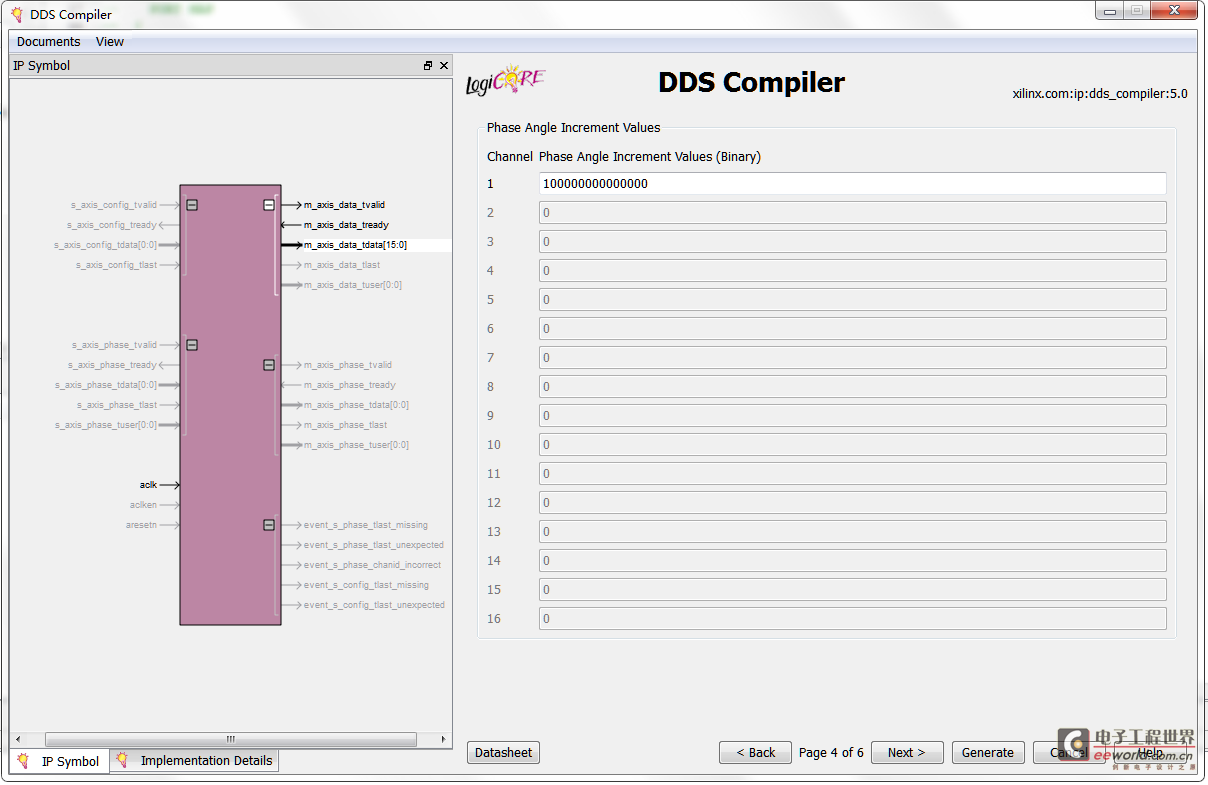

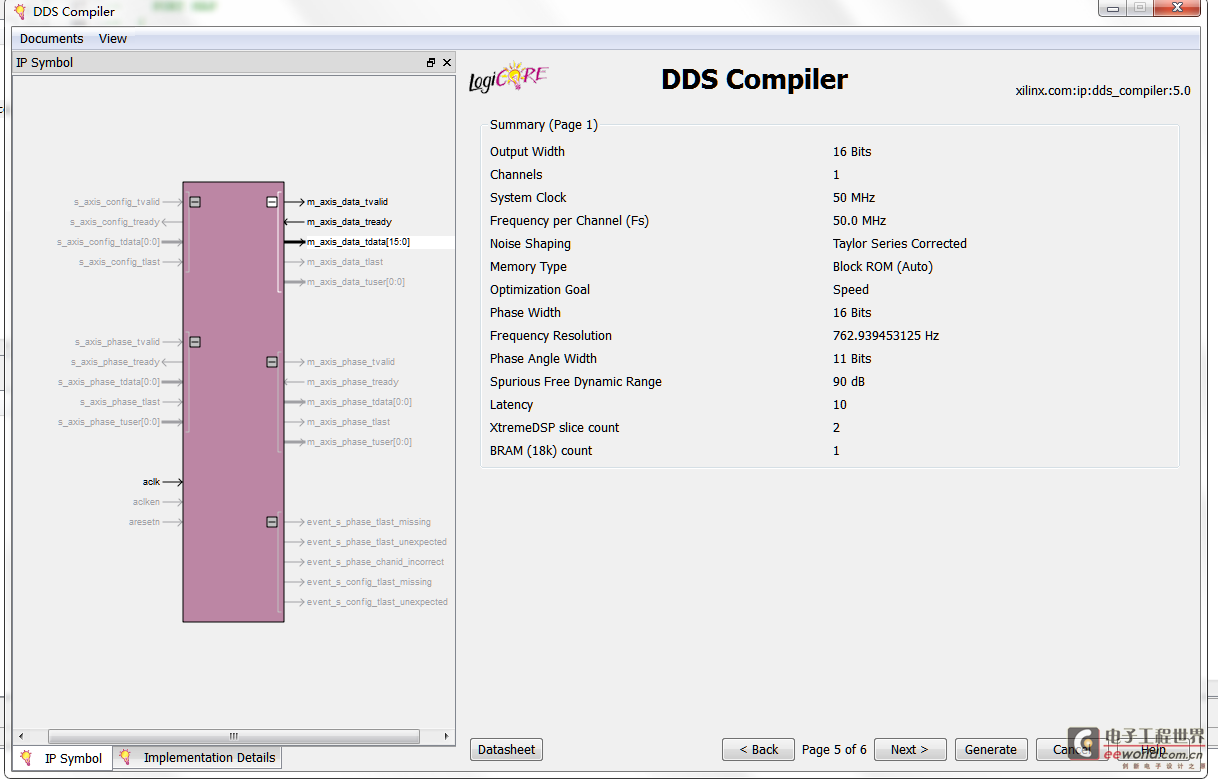

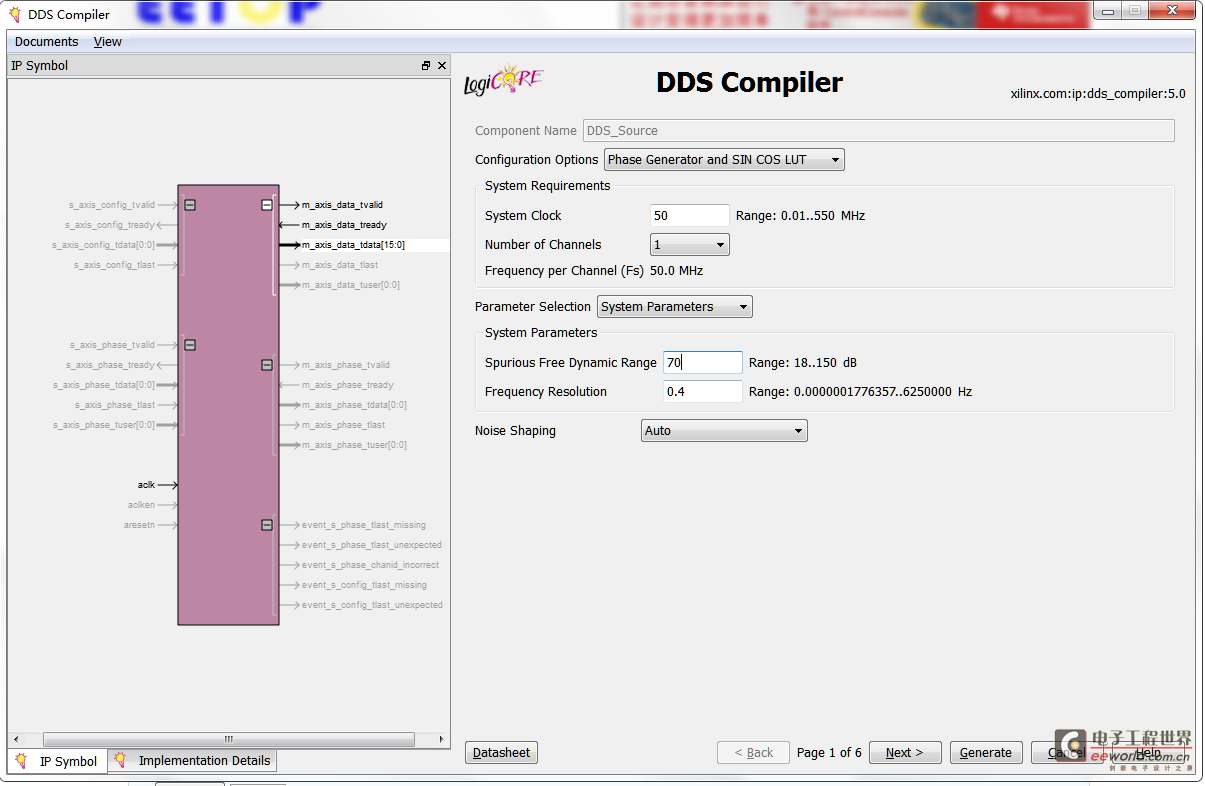

设置如下,外面给的aclk是50Mhz的,在这里要问一下,第一页System Clock是不是要和外面给的时钟一样?

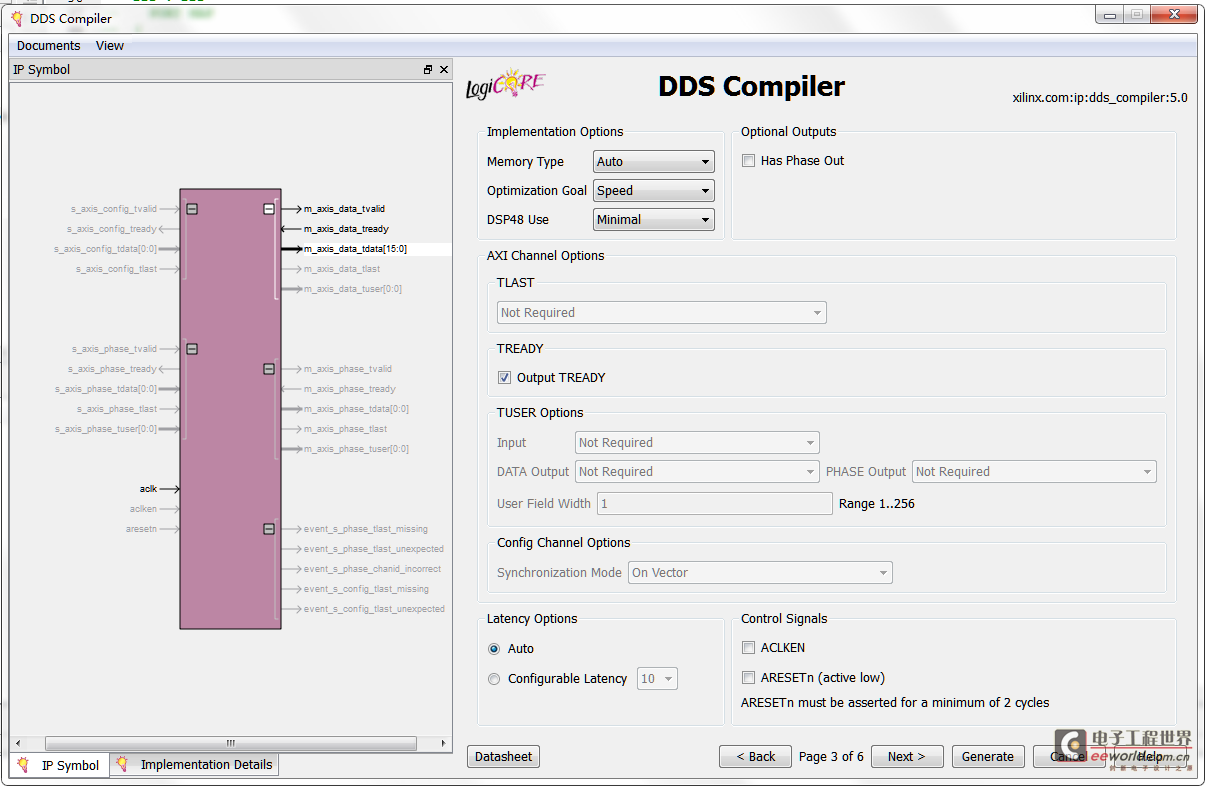

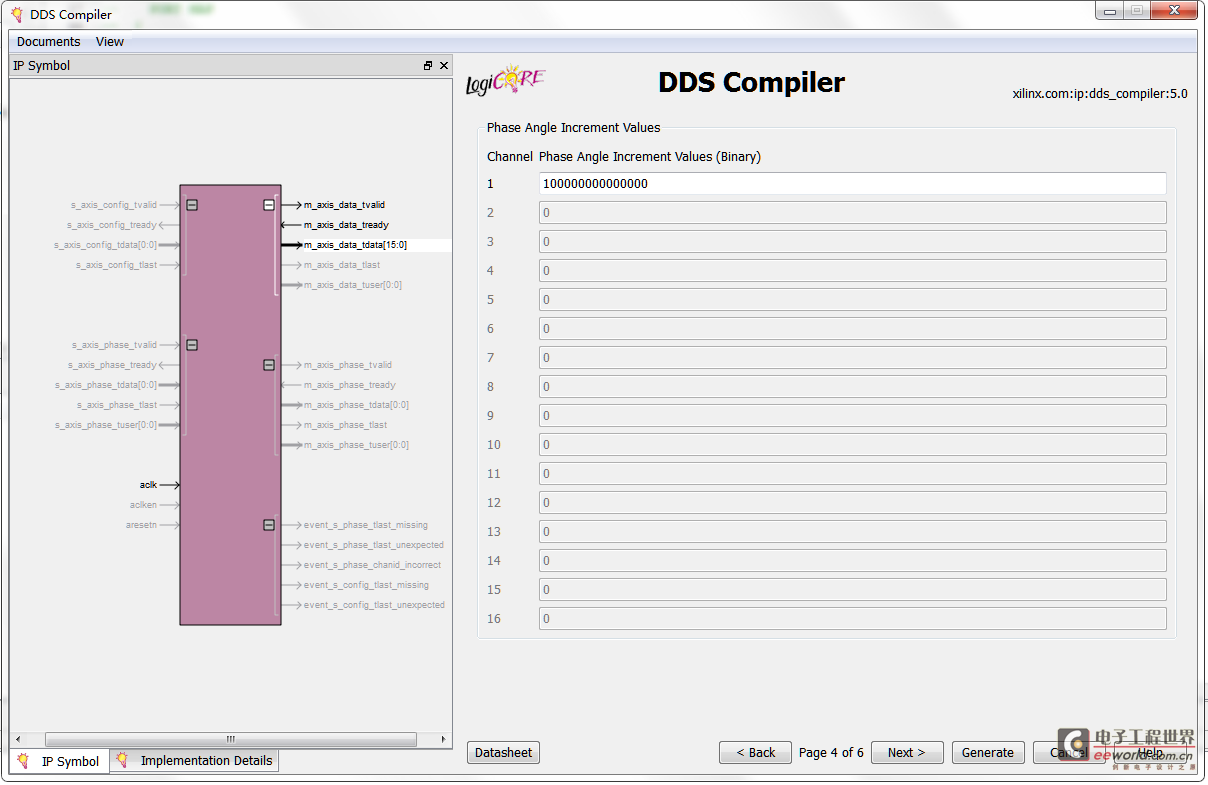

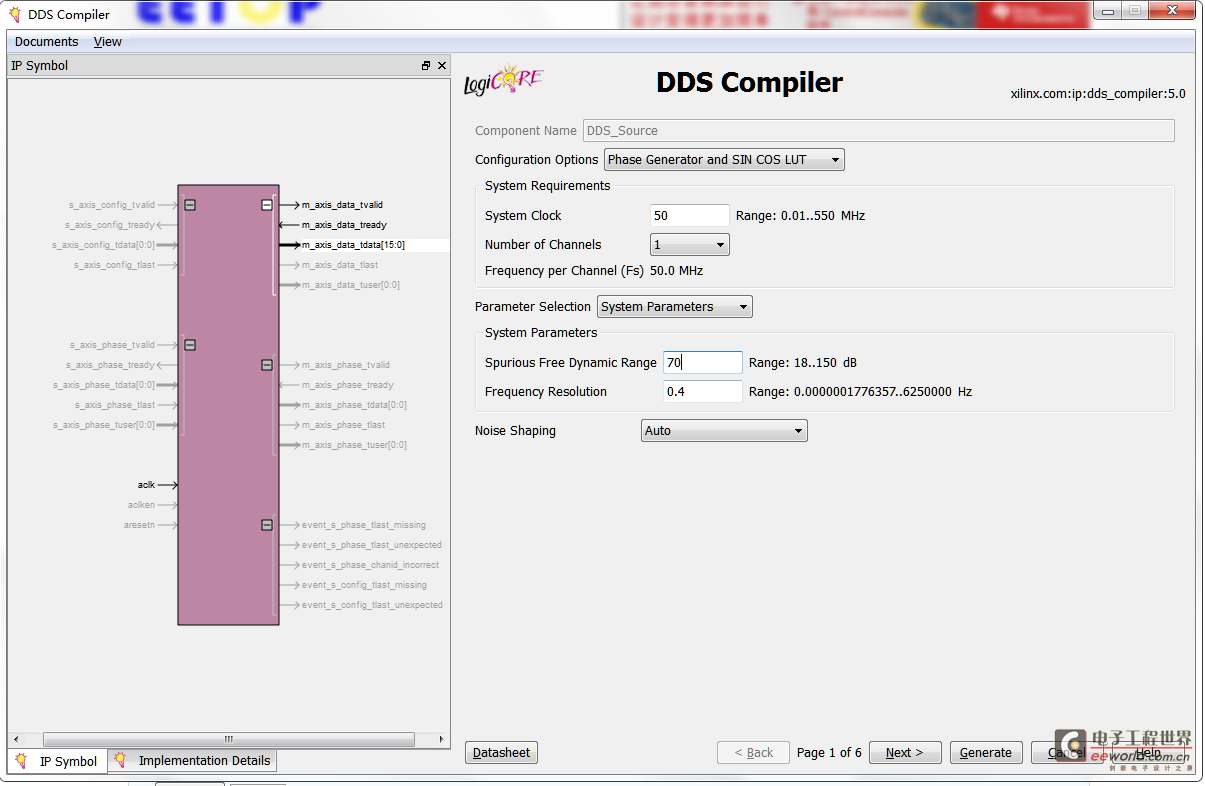

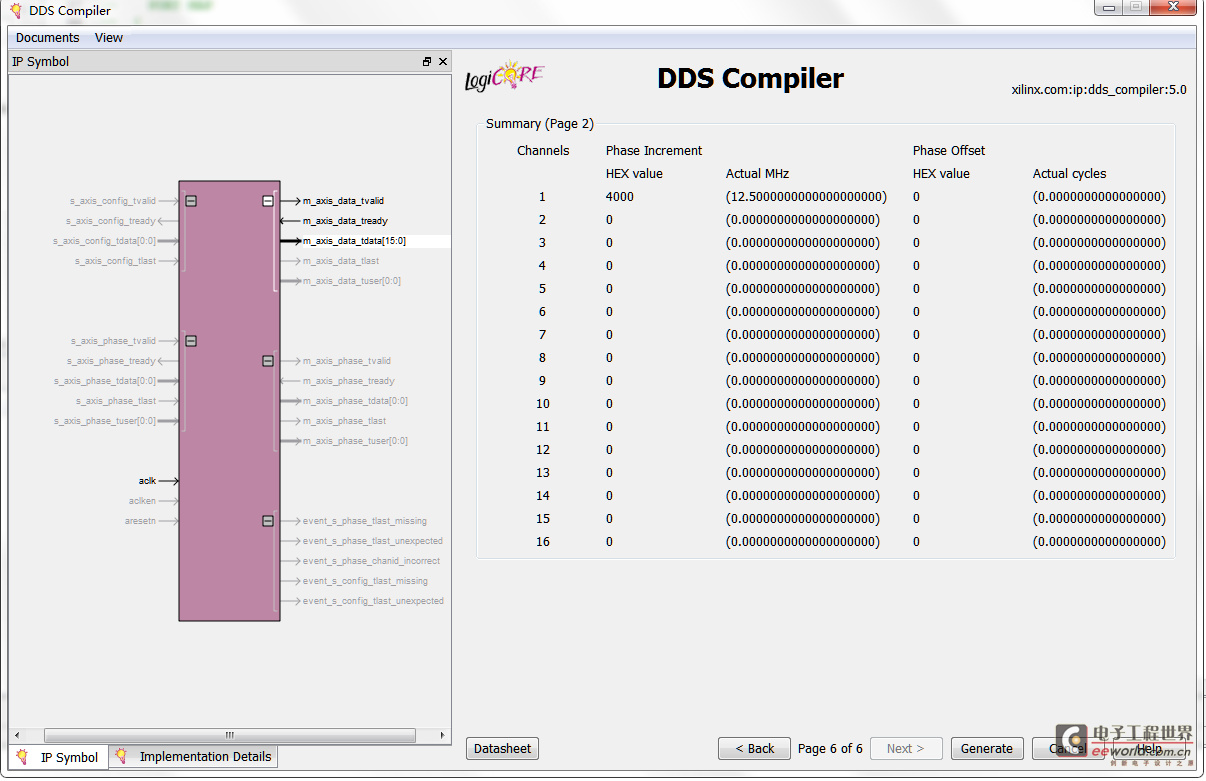

或者使用system parameters

但就是无法得出标准的正玄波,chipscope的时钟是100M的,请高手指教啊。。。 此帖出自小平头技术问答

设置如下,外面给的aclk是50Mhz的,在这里要问一下,第一页System Clock是不是要和外面给的时钟一样?

或者使用system parameters

但就是无法得出标准的正玄波,chipscope的时钟是100M的,请高手指教啊。。。 此帖出自小平头技术问答

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

正解 (相差倍数越高,波形越接近正弦波)

一周热门 更多>