本帖最后由 guaiguaidou 于 2015-7-27 10:48 编辑

最近学习特权同学的《深入浅出玩转FPGA》一书,想对里面的一个实验进行功能仿真(在书的p60)

但一直都得不到理想情况,请问这个是什么原因?

这是verilog代码:

module handshack

(

input clk,

input rst_n,

input req, //请求信号,高电平有效

input [7:0]datain,

output ack, //应答信号,高电平有效

output [7:0]dataout

);

reg reqr1,reqr2,reqr3;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

reqr1 <= 1'b1;

reqr2 <= 1'b1;

reqr3 <= 1'b1;

end

else

begin

reqr1 <= req;

reqr2 <= reqr1;

reqr3 <= reqr2;

end

end

//pos_req2比pos_req1延后一个时钟,确保数据被稳定锁存

wire pos_req1 = reqr1 & ~reqr2; //req上升沿标志位,高有效一个时钟周期

wire pos_req2 = reqr2 & ~reqr3; //req上升沿标志位,高有效一个时钟周期

reg [7:0]dataoutr;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n) dataoutr <= 8'h00;

else if(pos_req1) dataoutr <= datain;

end

assign dataout = dataoutr;

reg ackr;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n) ackr <= 1'b0;

else if(pos_req2) ackr <= 1'b1;

else if(!req) ackr <= 1'b0;

end

assign ack = ackr;

endmodule

下面是我写的testbend:

`timescale 1 ns/ 1 ps

module handshack_vlg_tst();

reg clk;

reg [7:0] datain;

reg req;

reg rst_n;

wire ack;

wire [7:0] dataout;

handshack i1 (

.ack(ack),

.clk(clk),

.datain(datain),

.dataout(dataout),

.req(req),

.rst_n(rst_n)

);

initial

begin

rst_n = 1; #20; rst_n = 0; #20; rst_n = 1;

clk = 1; forever #10 clk = ~clk;

end

reg [3:0]i;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

i <= 1'b0;

req <= 1'b0;

datain <= 8'd0;

end

else if(!ack)

case(i)

0,1,2:

begin req <= 1'b0;datain <= 8'd0;i <= i+1'b1;end

3,4,5,6:

begin req <= 1'b1;datain <= 8'd100;i <= i+1'b1;end

7:

i <= i;

endcase

else if(ack) req <= 1'b0;

end

endmodule

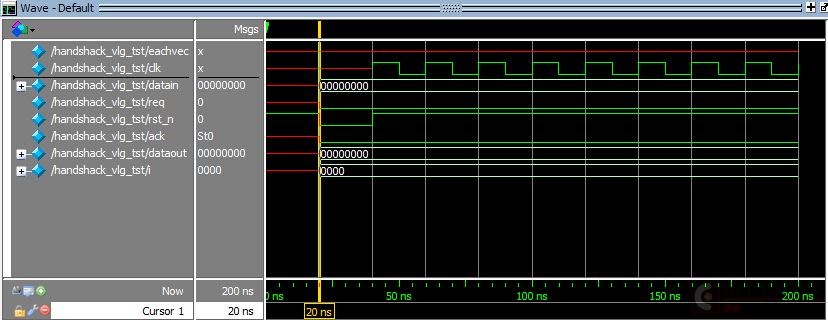

下面是仿真波形:

此帖出自小平头技术问答

最近学习特权同学的《深入浅出玩转FPGA》一书,想对里面的一个实验进行功能仿真(在书的p60)

但一直都得不到理想情况,请问这个是什么原因?

这是verilog代码:

module handshack

(

input clk,

input rst_n,

input req, //请求信号,高电平有效

input [7:0]datain,

output ack, //应答信号,高电平有效

output [7:0]dataout

);

reg reqr1,reqr2,reqr3;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

reqr1 <= 1'b1;

reqr2 <= 1'b1;

reqr3 <= 1'b1;

end

else

begin

reqr1 <= req;

reqr2 <= reqr1;

reqr3 <= reqr2;

end

end

//pos_req2比pos_req1延后一个时钟,确保数据被稳定锁存

wire pos_req1 = reqr1 & ~reqr2; //req上升沿标志位,高有效一个时钟周期

wire pos_req2 = reqr2 & ~reqr3; //req上升沿标志位,高有效一个时钟周期

reg [7:0]dataoutr;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n) dataoutr <= 8'h00;

else if(pos_req1) dataoutr <= datain;

end

assign dataout = dataoutr;

reg ackr;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n) ackr <= 1'b0;

else if(pos_req2) ackr <= 1'b1;

else if(!req) ackr <= 1'b0;

end

assign ack = ackr;

endmodule

下面是我写的testbend:

`timescale 1 ns/ 1 ps

module handshack_vlg_tst();

reg clk;

reg [7:0] datain;

reg req;

reg rst_n;

wire ack;

wire [7:0] dataout;

handshack i1 (

.ack(ack),

.clk(clk),

.datain(datain),

.dataout(dataout),

.req(req),

.rst_n(rst_n)

);

initial

begin

rst_n = 1; #20; rst_n = 0; #20; rst_n = 1;

clk = 1; forever #10 clk = ~clk;

end

reg [3:0]i;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

i <= 1'b0;

req <= 1'b0;

datain <= 8'd0;

end

else if(!ack)

case(i)

0,1,2:

begin req <= 1'b0;datain <= 8'd0;i <= i+1'b1;end

3,4,5,6:

begin req <= 1'b1;datain <= 8'd100;i <= i+1'b1;end

7:

i <= i;

endcase

else if(ack) req <= 1'b0;

end

endmodule

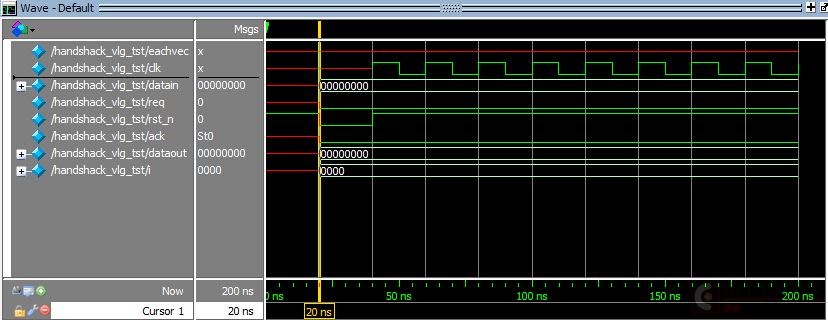

下面是仿真波形:

此帖出自小平头技术问答

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

额,解决的速度真快

谈谈怎么回事儿,让后来人有个借鉴 :)

初始化赋值问题,应该在initial里面对i、req、datain进行赋值的。不用在rst_n里面赋值

一周热门 更多>