本帖最后由 pinggougou 于 2015-5-24 01:21 编辑

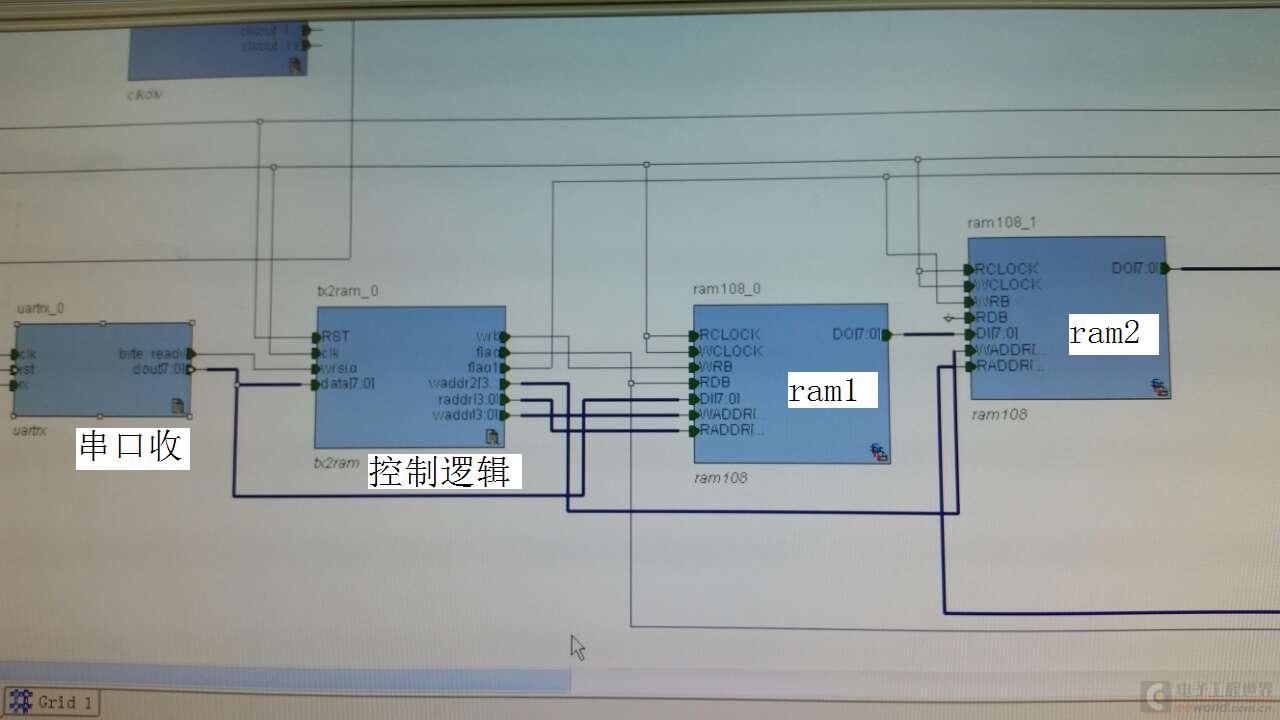

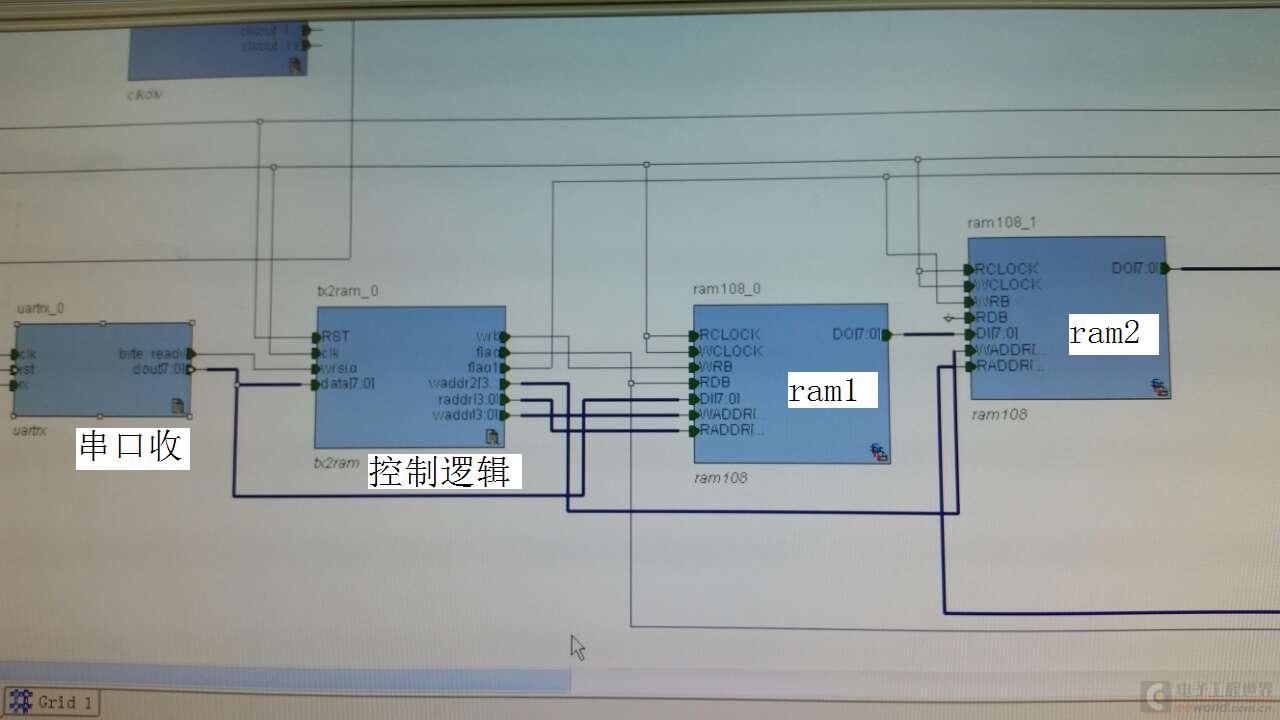

如图所示,串口收到的数据,存到ram块里去,这里用到两个ram块,以完成数据中转。

但在用控制逻辑实现数据从ram1转到ram2里的时候,出现ram1保存的最后一个数字总是填到了ram2的第一里面去。

譬如:ram1里数据:1,2,3,4,5

则 :ram2里数据:5,1,2,3,4。

控制逻辑模块用vhdl写的,用modelsimsim仿真也没有问题啊,烧到板子上却总是出现上面的情况。

vhdl代码如下:

此帖出自小平头技术问答

如图所示,串口收到的数据,存到ram块里去,这里用到两个ram块,以完成数据中转。

但在用控制逻辑实现数据从ram1转到ram2里的时候,出现ram1保存的最后一个数字总是填到了ram2的第一里面去。

譬如:ram1里数据:1,2,3,4,5

则 :ram2里数据:5,1,2,3,4。

控制逻辑模块用vhdl写的,用modelsimsim仿真也没有问题啊,烧到板子上却总是出现上面的情况。

vhdl代码如下:

- <blockquote>library ieee;

ram块,在wrb,rdb低电平时可以读写数据,然后在时钟的低电平写入或读出数据,读出数据需要一个持续一个低电平

此帖出自小平头技术问答

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

- library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_arith.all;

- --use ieee.std_logic_unsigned.all;

-

- entity tx2ram is

- port

- ( clk :in std_logic;

- wrsig :in std_logic; --串口接收模块有数据发来

- waddr1 :out std_logic_vector(3 downto 0); --RAM1写地址

- raddr1 :out std_logic_vector(3 downto 0); --RAM1读地址

- waddr2 :out std_logic_vector(3 downto 0); --RAM2写地址

- flag1 :buffer std_logic; --ram1读控制信号,低电平有效

- flag2 :out std_logic; --ram2写控制信号,低电平有效

- wrb :out std_logic

- );

- end entity;

-

- architecture rtl of tx2ram is

- type state is (s0,s1,s2);

-

- signal s :state;

- signal wrsigbuff:std_logic;

- signal wrsigrise :std_logic;

- signal waddr3 :std_logic_vector(3 downto 0);

- begin

- wrb<= not wrsigrise; --低电平时,可以向ram1里写数

- process(clk)

- variable v_waddr,v_raddr :std_logic_vector(3 downto 0);

- begin

- if falling_edge(clk) then

- wrsigbuff<=wrsig;

- wrsigrise<=not wrsigbuff and wrsig; --检测数据到来标志位的上升沿

- case s is

- when s0 =>flag1<='1';

- if wrsigrise='1' then --如果有数据到来,存储数据

- v_waddr:=v_waddr+1; --地址变换

- if v_waddr=conv_std_logic_vector(15,4) then --当存满15个数时,跳到下一状态

- v_waddr:="0000";s<=s1;

- else s<=s0;

- end if;

- else s<=s0;

- end if;

- when s1 => --写完数据后,将ram1里的数据写入ram2

- flag1<='0';

- v_raddr:=v_raddr+1; --读出ram1第v_raddr里的地址,写入ram2第v_raddr个地址里

- if v_waddr=conv_std_logic_vector(15,4) then --读完15个数时,跳到下一状态

- v_waddr:="0000";s<=s0;

- else s<=s1;

- end if;

- when others =>s<=s0;

- end case;

- waddr1<=v_waddr;

- raddr1<=v_raddr; --在读写数据标志位有效时,低电平写入数据

- waddr3<=v_raddr;

- waddr2<=waddr3; --ram2写数据地址,比ram1的读数据地址延迟一个周期

- flag2<=flag1;

-

- end process;

- end rtl;

复制代码一周热门 更多>