请教个配置问题:

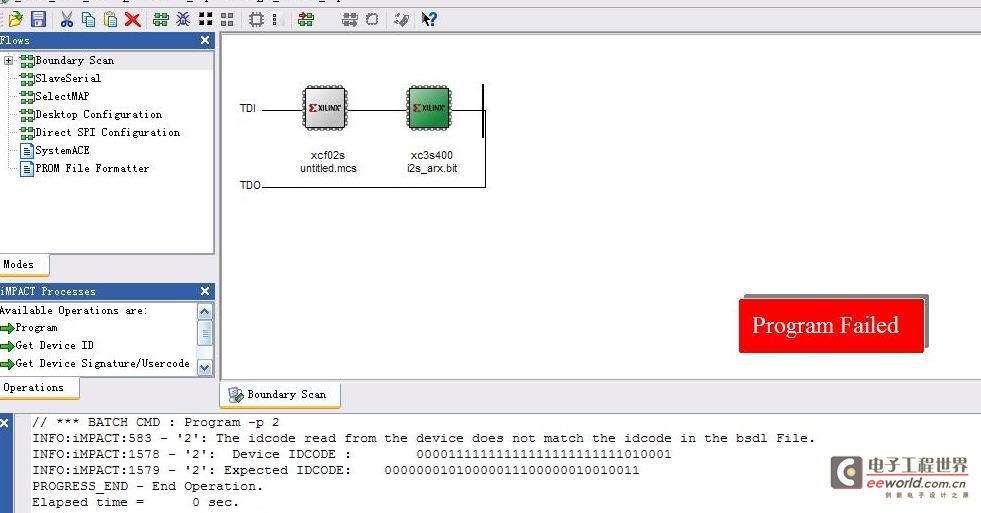

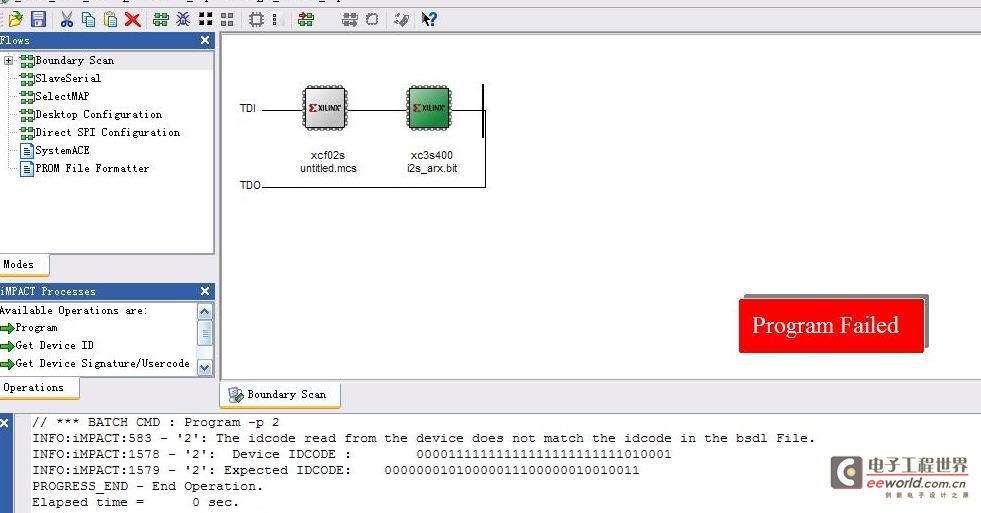

在初始化下载链时,能找到FPGA芯片与配置芯片,可是在下载程序时,无论是下载到配置芯片,还是直接下载FPGA芯片,都遇到IDCODE 不匹配的错误(如图所示),请问高手这是什么原因造成的?(配置芯片上存有程序,且现在程序能正常运行的

此帖出自小平头技术问答

在初始化下载链时,能找到FPGA芯片与配置芯片,可是在下载程序时,无论是下载到配置芯片,还是直接下载FPGA芯片,都遇到IDCODE 不匹配的错误(如图所示),请问高手这是什么原因造成的?(配置芯片上存有程序,且现在程序能正常运行的

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

1 Xilinx配置过程

主要讲一下Startup Sequence。

Startup Sequence由8个状态组成.

除了7是固定的之外,其它几个的顺序是用户可设置的,而且Wait for DCM和DCI是可选的。

其中默认顺序如下:

这些在ISE生成bit文件时通过属性页设定。

这几个状态的具体含义如下:

Release_DONE : DONE信号变高

GWE : 使能CLB和IOB,FPGA的RAMs和FFs可以改变状态

GTS : 激活用户IO,之前都是高阻。

EOS : 表示配置结束

DCI_MATCH : 表示所有的DCI(Digitally Controlled Impedance)控制器已经把内部电阻和外部参考电阻匹配完毕。

DCM_LOCK : 表示所有的DCM已经锁定。这个选项默认是选中的。

因此,我们可以得出如下结论:

(1)FPGA最后的Startup过程有8个周期,其中DONE变高仅仅是第4个周期。因此,在DONE变高之后还需要再给3个CCLK。否则DONE虽然变高了,FPGA程序并没有正确运行。

(2)ISE会在设计中搜索用户是否使用了DCI,如果是,FPGA会使用2个周期的Start Up Phase,等待DCI匹配上。即FPGA会在那儿等待,直到DCI匹配上。如果我们在上位机读取了配置文件,获得了文件大小,我们把它写到负责加载V4的SP3里,然后CCLK时钟就不给了。这就产生问题,因为DCI匹配需要时间,我们的问题就是,过了一段时间,DCI匹配完毕了,但是CCLK却没有了,因此FPGA一直处在Start UP的前2个Phase上,不会到DONE。导致无法配置成功。

看xilinx Development System Reference Guide(dev.pdf)中,写到

BitGen Match_cycle

The BitGen Match_cycle setting specifies a stall in the Startup cycle until digitally

controlled impedance (DCI) match signals are asserted.DCI matching does not begin on the Match_cycle that was set in BitGen. The Startup sequence simply waits in this cycle until DCI has matched. Given that there are a number of variables in determining how long it will take DCI to match, the number of CCLK cycles required to complete the Startup sequence may vary in any given system. Ideally, the configuration solution should continue driving CCLK until DONE goes high. When the Auto setting is specified, BitGen searches the design for any DCI I/O standards.

If DCI standards exist, BitGen uses Match_cycle:2. Otherwise, BitGen uses Match_cycle:NoWait.

关于DCI_MATCH的设置,在生成bit文件的StartUP Options里有个Match Cycle的选项,默认是Auto。含义是ISE会去确认用户是否使用了DCI,没有的话,Startup Sequence直接跳过这一步,否则会等待DCI匹配完毕。

一周热门 更多>