本帖最后由 tangjianyuan 于 2015-3-5 15:14 编辑

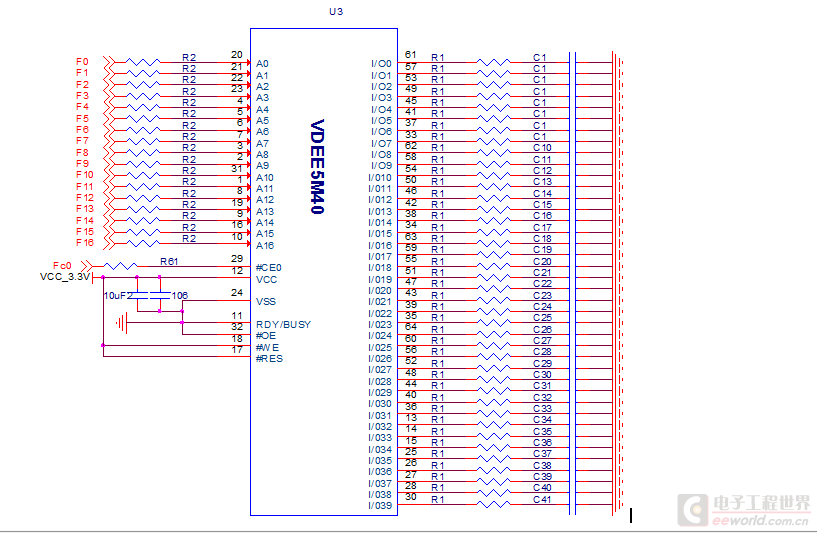

大家好,请问各位FPGA大神们,想问一下大家这个多频率怎么编写啊,这是一款EEPROM存储芯片,要求输入如下面频率信号。图中电源电压VCC=3.3V,R1 = 1×(1±10%)KΩ,R2 = 1×(1±10%)KΩ,C1 = 30×(1±10%)pF。输入信号F0 = 1MHz,F1 = F0/2,F2 = F1/2,F3 = F2/2,F4 = F3/2,F5 = F4/2,F6 = F5/2,F7 = F6/2,F8 = F7/2,F9 = F8/2,F10 = F9/2,F11 = F10/2,F12 = F11/2,F13 = F12/2,F14 = F13/2,F15 = F14/2,F16 = F15/2,FC0 = 500KHZ。请问F0,F1,F2,F3,F4,F5,,,的频率怎么分。

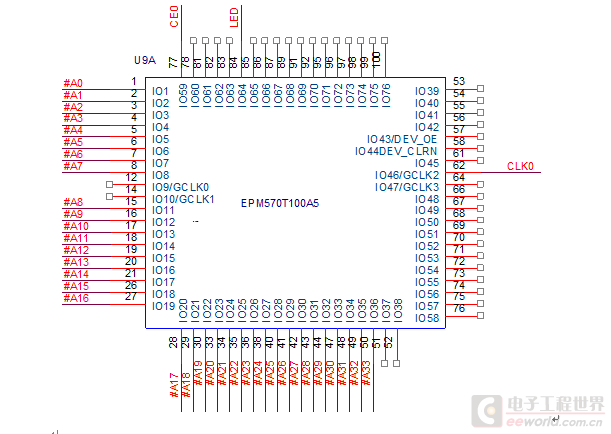

时钟频率由外部clk0产生50MHZ的晶振,从CLK0输入到CPLD芯片内部,但现在我有点不知道怎么把50HMZ的频率,每次都二分频,给到不同的地址上去,百度过,想到用二分频的方法,由于小弟对FPGA不很会用,只是在学校学习过VHDL语言,有些语法还不太会用。请大神们指点一下。下面是我预先写的一个程序,在处理地址上的不同频率,还不太对。望指点一下感激不尽。module VDEE5M40VS(clk_in,cs,led,rest,address);

input clk_in,rest;output [2:0] led;output [16:0] address;output cs;

reg cs;reg clk_out;reg clk_500k;reg [2:0] led;reg [49:0] j; // 1MHZ counter datareg [99:0] k; // 500khz counter datareg [31:0] count1;reg [31:0] num;reg [16:0] address;reg [35:0] count2;parameter N=36;

initial begin count1 <=32'h0000_0000; count2<=32'h0000_0000; num<= 32'h0000_0000; led<= 3'hf0; cs<=1'b0; address<= 17'h0000_0000;end

always @(posedge clk_in)begin if(count2==N/2-1) // 50MHZfrequency counter number 50 generate 1MHZ begin clk_out <=!clk_out; count2 <=0; end else count2<= count2+1'b1;

end/******************************************************************* LED Control 1s 闪烁********************************************************************/

always @(posedge clk_in) begin if(num == 32'd50000000) begin led[0]<=~led[0]; num<=32'b0; end else begin num <= num +1'b1; endend/******************************************************************** address control 这里的多频率/2,加载到不同的地址线上,不知改如何处理**********************************************************************/ always@(posedge clk_out) begin if(count1 <= 32'd50) begin if(count1 %2 ==1'b1) begin //we <= 1'b1; //oe <= 1'b1; address <= address+1'b1; end elsebegin //we <= 1'b1; // oe <= 1'b1; address <= address; end count1 <=count1+1'b1; end elsebegin led [2] <= ~led [2]; count1<= 32'h0000000; address<=17'h000000;

end end/******************************************************************** generate 500kHZ frequency**********************************************************************/always @(posedge clk_in) //50MHZ clk 时钟信号产生 500KHZ信号begin if(k==100) //500KHZ=50MHZ/100 begin k <=0; clk_500k <=~clk_500k; end

end/******************************************************************** chip cs0 control**********************************************************************/ always @(posedge clk_500k)begin if(led[2] <=1'b0) begin cs<= ~cs; end else cs<= 1'b1;

endendmodule

IC测试QQ群(111938408

此帖出自小平头技术问答

大家好,请问各位FPGA大神们,想问一下大家这个多频率怎么编写啊,这是一款EEPROM存储芯片,要求输入如下面频率信号。图中电源电压VCC=3.3V,R1 = 1×(1±10%)KΩ,R2 = 1×(1±10%)KΩ,C1 = 30×(1±10%)pF。输入信号F0 = 1MHz,F1 = F0/2,F2 = F1/2,F3 = F2/2,F4 = F3/2,F5 = F4/2,F6 = F5/2,F7 = F6/2,F8 = F7/2,F9 = F8/2,F10 = F9/2,F11 = F10/2,F12 = F11/2,F13 = F12/2,F14 = F13/2,F15 = F14/2,F16 = F15/2,FC0 = 500KHZ。请问F0,F1,F2,F3,F4,F5,,,的频率怎么分。

时钟频率由外部clk0产生50MHZ的晶振,从CLK0输入到CPLD芯片内部,但现在我有点不知道怎么把50HMZ的频率,每次都二分频,给到不同的地址上去,百度过,想到用二分频的方法,由于小弟对FPGA不很会用,只是在学校学习过VHDL语言,有些语法还不太会用。请大神们指点一下。下面是我预先写的一个程序,在处理地址上的不同频率,还不太对。望指点一下感激不尽。module VDEE5M40VS(clk_in,cs,led,rest,address);

input clk_in,rest;output [2:0] led;output [16:0] address;output cs;

reg cs;reg clk_out;reg clk_500k;reg [2:0] led;reg [49:0] j; // 1MHZ counter datareg [99:0] k; // 500khz counter datareg [31:0] count1;reg [31:0] num;reg [16:0] address;reg [35:0] count2;parameter N=36;

initial begin count1 <=32'h0000_0000; count2<=32'h0000_0000; num<= 32'h0000_0000; led<= 3'hf0; cs<=1'b0; address<= 17'h0000_0000;end

always @(posedge clk_in)begin if(count2==N/2-1) // 50MHZfrequency counter number 50 generate 1MHZ begin clk_out <=!clk_out; count2 <=0; end else count2<= count2+1'b1;

end/******************************************************************* LED Control 1s 闪烁********************************************************************/

always @(posedge clk_in) begin if(num == 32'd50000000) begin led[0]<=~led[0]; num<=32'b0; end else begin num <= num +1'b1; endend/******************************************************************** address control 这里的多频率/2,加载到不同的地址线上,不知改如何处理**********************************************************************/ always@(posedge clk_out) begin if(count1 <= 32'd50) begin if(count1 %2 ==1'b1) begin //we <= 1'b1; //oe <= 1'b1; address <= address+1'b1; end elsebegin //we <= 1'b1; // oe <= 1'b1; address <= address; end count1 <=count1+1'b1; end elsebegin led [2] <= ~led [2]; count1<= 32'h0000000; address<=17'h000000;

end end/******************************************************************** generate 500kHZ frequency**********************************************************************/always @(posedge clk_in) //50MHZ clk 时钟信号产生 500KHZ信号begin if(k==100) //500KHZ=50MHZ/100 begin k <=0; clk_500k <=~clk_500k; end

end/******************************************************************** chip cs0 control**********************************************************************/ always @(posedge clk_500k)begin if(led[2] <=1'b0) begin cs<= ~cs; end else cs<= 1'b1;

endendmodule

IC测试QQ群(111938408

此帖出自小平头技术问答

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

不知道你是不是需要这样的波形

0信号为1MHz

附参考代码

Test.v

- module Test(

- sys_clk,

- sys_rst,

- div_clk

- );

- input sys_clk;

- input sys_rst;

- output [15:0] div_clk;

- reg clk_2mhz;

- reg [15:0] clk_2mhz_count;

- reg [15:0] s_div_clk;

- always @(posedge sys_clk or negedge sys_rst)begin

- if(!sys_rst)begin

- clk_2mhz <= 1'b0;

- clk_2mhz_count <= 16'd0;

- end

- else begin

- if(clk_2mhz_count == 16'd24)begin

- clk_2mhz <= 1'b1;

- clk_2mhz_count <= 16'd0;

- end

- else begin

- clk_2mhz <= 1'b0;

- clk_2mhz_count <= clk_2mhz_count + 16'd1;

- end

- end

- end

- always @(posedge clk_2mhz or negedge sys_rst)begin

- if(!sys_rst)begin

- s_div_clk[0] <= 1'b0;

- end

- else begin

- s_div_clk[0] <= ~s_div_clk[0];

- end

- end

- always @(posedge s_div_clk[0] or negedge sys_rst)begin

- if(!sys_rst)begin

- s_div_clk[1] <= 1'b0;

- end

- else begin

- s_div_clk[1] <= ~s_div_clk[1];

- end

- end

- always @(posedge s_div_clk[1] or negedge sys_rst)begin

- if(!sys_rst)begin

- s_div_clk[2] <= 1'b0;

- end

- else begin

- s_div_clk[2] <= ~s_div_clk[2];

- end

- end

- always @(posedge s_div_clk[2] or negedge sys_rst)begin

- if(!sys_rst)begin

- s_div_clk[3] <= 1'b0;

- end

- else begin

- s_div_clk[3] <= ~s_div_clk[3];

- end

- end

- endmodule

复制代码Test_tb.sv

- module Test_tb();

- reg sys_clk;

- reg sys_rst;

- wire [15:0] div_clk;

- Test test_inst(

- .sys_clk(sys_clk),

- .sys_rst(sys_rst),

- .div_clk(div_clk)

- );

- initial begin

- sys_clk <= 1'b0;

- sys_rst <= 1'b0;

- #100ns;

- sys_rst <= 1'b1;

- end

- always #10ns sys_clk<=~sys_clk;

- endmodule

复制代码不过EEPROM这样驱动对不对俺搅得有些疑问:

1、FC0是F0的2分频,F0不就没用了吗?是否FC0应常为低电平?

2、RDY/BUSY脚似不应接地,应悬空才对。

always @(posedge sys_clk or negedge sys_rst)begin

if(!sys_rst)begin

clk_2mhz <= 1'b0;

clk_2mhz_count <= 16'd0;

end

else begin

if(clk_2mhz_count == 16'd24)begin

clk_2mhz <= 1'b1;

clk_2mhz_count <= 16'd0;

end

else begin

clk_2mhz <= 1'b0;

clk_2mhz_count <= clk_2mhz_count + 16'd1;

end

end

end

这里有的理解不过来,你放在是做一个地址计数吧,

你能在用文字讲一下思路吗?其实我这一张器件的寿命老炼图,我那张原理图上有很多VDEE5m40同样的模块,只是把地址线,控制线全接到CPLD上,再通过Cpld加入激励倒芯片管教上,而加的激励有要求就是上面这个频率要求,现在卡克在怎么精确把这个频率输送的对应的地址管脚,没有搞明白,望在能解释一下。

功能描述时看似有很多种频率,其实只是逐个做2分频,很规律,只需把存储器的地址线接到一个2进制计数器上,让计数器周而复始转就行了。

如用FPGA做也就是写个不断+1的计数器而已,只需1个process,几行字。

●关于FC0

图中FC0接的是存储器的片选,0有效。如果让FC0也在变,那么当FC0=1时存储器是不输出,是测试不到数据的。

●关于RDY/BUSY

俺没查到该型号存储器的datasheet,但按常识RDY/BUSY一般是输出脚,接地可能会冲突损坏芯片。另:RDY/BUSY多为开漏输出,上拉电阻后才能看到芯片的状态,不用时可悬空。

这段代码只是为了得到一个2MHz的时钟信号。

clk_div最后直接例化到地址线就可以了。如果还是不明白可以Q我(717213469)

一周热门 更多>