BDF如下

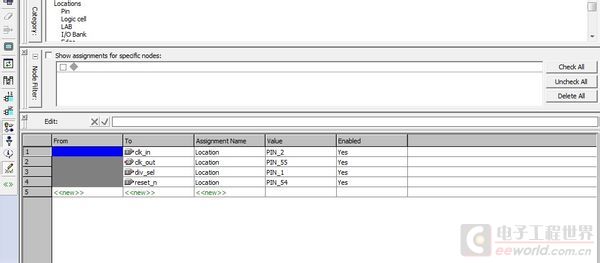

定义引脚截图如下

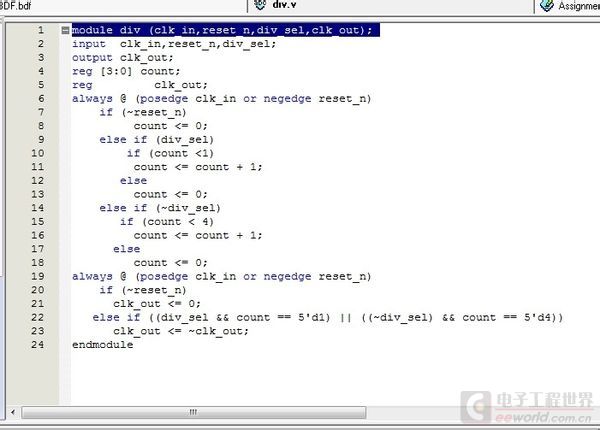

问题就在这,BDF里的DIV_SEL的四个引脚不能定义。只是一直在在单独定义每个模块。单个模块的功能是,当是1时2分频,当是0时5分频。然后把四个级联起来,由单片机分别给四个DIV_SEL接口给信号,比如是1101,就是2X2X5X2=40分频。 下面是源程序,module div (clk_in,reset_n,div_sel,clk_out);

input clk_in,reset_n,div_sel;

output clk_out;

reg [3:0] count;

reg clk_out;

always @ (posedge clk_in or negedge reset_n)

if (~reset_n)

count <= 0;

else if (div_sel)

if (count <1)

count <= count + 1;

else

count <= 0;

else if (~div_sel)

if (count < 4)

count <= count + 1;

else

count <= 0;

always @ (posedge clk_in or negedge reset_n)

if (~reset_n)

clk_out <= 0;

else if ((div_sel && count == 5'd1) || ((~div_sel) && count == 5'd4))

clk_out <= ~clk_out;

endmodule

我觉得是不是程序的问题?(虽然程序最后能单独仿真出波形)还是在级联图形的时候哪没弄对?芯片是altera 的epm240t100c5n由于是刚接触quartusii不久,东西也是自己看书,上网看资料一点一点摸索的,这最后一步了,实在是有点搞不出来了。所以还请大神们帮帮忙,小弟在此谢过。

此帖出自小平头技术问答

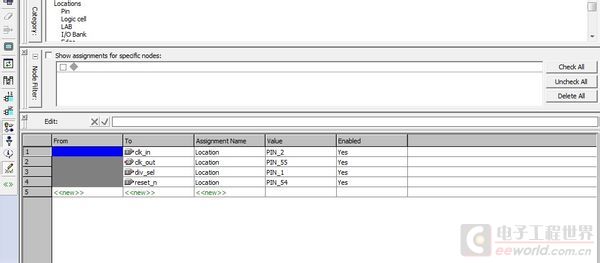

定义引脚截图如下

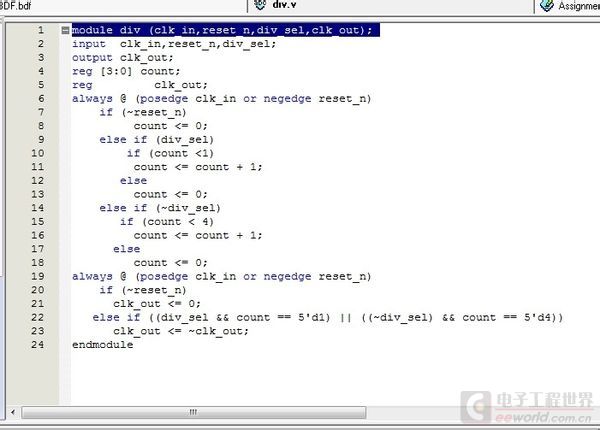

问题就在这,BDF里的DIV_SEL的四个引脚不能定义。只是一直在在单独定义每个模块。单个模块的功能是,当是1时2分频,当是0时5分频。然后把四个级联起来,由单片机分别给四个DIV_SEL接口给信号,比如是1101,就是2X2X5X2=40分频。 下面是源程序,module div (clk_in,reset_n,div_sel,clk_out);

input clk_in,reset_n,div_sel;

output clk_out;

reg [3:0] count;

reg clk_out;

always @ (posedge clk_in or negedge reset_n)

if (~reset_n)

count <= 0;

else if (div_sel)

if (count <1)

count <= count + 1;

else

count <= 0;

else if (~div_sel)

if (count < 4)

count <= count + 1;

else

count <= 0;

always @ (posedge clk_in or negedge reset_n)

if (~reset_n)

clk_out <= 0;

else if ((div_sel && count == 5'd1) || ((~div_sel) && count == 5'd4))

clk_out <= ~clk_out;

endmodule

我觉得是不是程序的问题?(虽然程序最后能单独仿真出波形)还是在级联图形的时候哪没弄对?芯片是altera 的epm240t100c5n由于是刚接触quartusii不久,东西也是自己看书,上网看资料一点一点摸索的,这最后一步了,实在是有点搞不出来了。所以还请大神们帮帮忙,小弟在此谢过。

此帖出自小平头技术问答

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

恩,是的。

您方便加我企鹅么?

一周热门 更多>