新手,请各位指教。

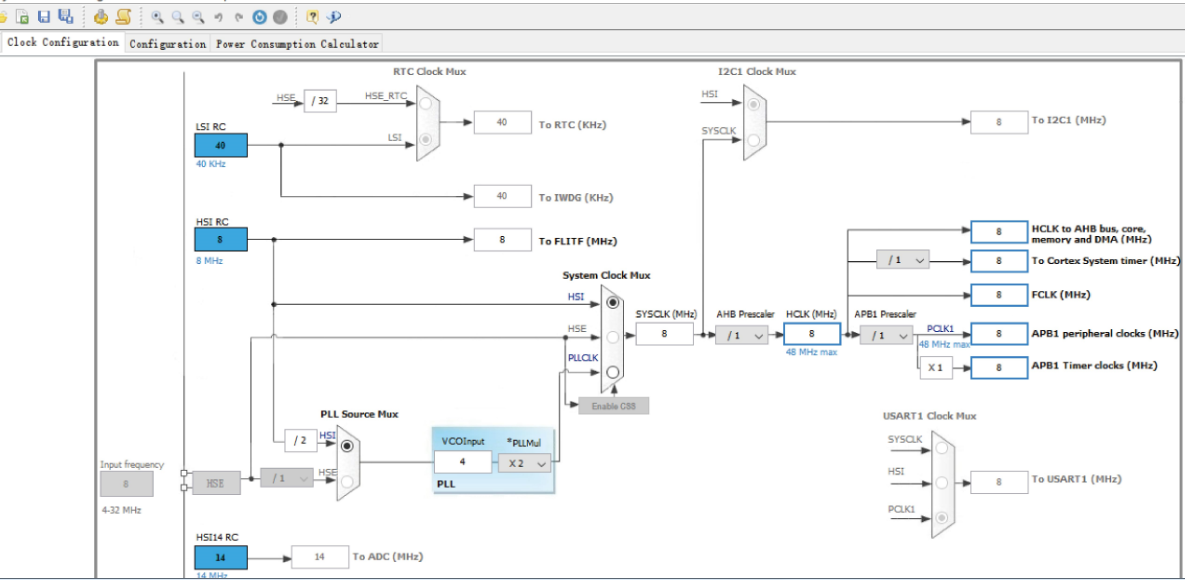

如下,mcu是f030f4p6,看时钟图没有看到apb2,是挂在hsi14下的

请问,如下两句代码能正确执行吗?系统时钟48m,如果apb2是48m,那么adcclk 4分频是12m

RCC_APB2PeriphClockCmd(RCC_APB2Periph_ADC1, ENABLE);

RCC_ADCCLKConfig(RCC_ADCCLK_PCLK_Div4);

还是说不要第一句,第二句配置为RCC_ADCCLKConfig(RCC_ADCCLK_HSI14);

以下是RCC_ADCCLKConfig的定义

/**

* @brief Configures the ADC clock (ADCCLK).

* @param RCC_ADCCLK: defines the ADC clock source. This clock is derived

* from the HSI14 or APB clock (PCLK).

* This parameter can be one of the following values:

* @arg RCC_ADCCLK_HSI14: ADC clock = HSI14 (14MHz)

* @arg RCC_ADCCLK_PCLK_Div2: ADC clock = PCLK/2

* @arg RCC_ADCCLK_PCLK_Div4: ADC clock = PCLK/4

* @retval None

*/

void RCC_ADCCLKConfig(uint32_t RCC_ADCCLK)

{

/* Check the parameters */

assert_param(IS_RCC_ADCCLK(RCC_ADCCLK));

/* Clear ADCPRE bit */

RCC->CFGR &= ~RCC_CFGR_ADCPRE;

/* Set ADCPRE bits according to RCC_PCLK value */

RCC->CFGR |= RCC_ADCCLK & 0xFFFF;

/* Clear ADCSW bit */

RCC->CFGR3 &= ~RCC_CFGR3_ADCSW;

/* Set ADCSW bits according to RCC_ADCCLK value */

RCC->CFGR3 |= RCC_ADCCLK >> 16;

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

一周热门 更多>