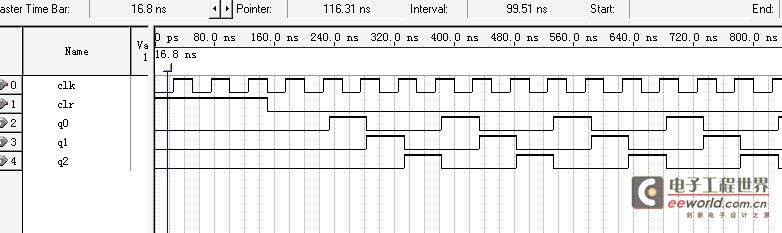

- module shunxu(q0,q1,q2,clk,clr);

output q0,q1,q2;

input clk,clr;

reg q0,q1,q2;

reg[2:0] x,y;

always @(posedge clk)

begin

if(clr)

begin y<='b000;x<='b001;end

else

begin

y<=x;

x<={x[1:0],x[2]};

end

q0<=y[0];

q1<=y[1];

q2<=y[2];

end

endmodule

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

阻塞与非阻塞

always @(a or b or c)

begin

x=c+y;//语句1

y=a+b;//语句2

end

y原来的值是5;

a=1;

b=1;

c=3;

我仿真的结果是 x=5+3=8 y=1+1=2

资料上的解释是说 语句1和语句2同时进行,但是由于是阻塞赋值,所以要等语句1执行完了之后才能执行第二条语句,所以语句1中的值是原来的值;

与我自己的仿真结果一致;

always @(a or b or c)

begin

x<=c+y;

y<=a+b;

end

y原来的值是5;

a=1;

b=1;

c=3;

仿真的结果是 x=8 y=2;

我看的资料上说 在此时刻 x=3+2=5 y=1+1=2 他的意思是说 a+b 的值给 y ;然后 y+c的值再给x;

仿真的结果和 资料上说的不一样

求指教!!!!

这是我前几天发的帖子,是不是和你问的一个问题啊?我觉得是第二个,而且我仿真出来的结果证明也是第二个,但是资料上说是第一个。我也比较郁闷呢。

一周热门 更多>