第一次发帖,写得不好还请大家指正!

最近在看正点原子写的《STM32不完全手册》,sys.h有一个关于NVIC的分组函数My_NVIC_PriorityGroupConfig,该函数的参数NVIC_Group为要设置的分组号,可选范围为0~4,总共5组。My_NVIC_PriorityGroupConfig函数代码如下:

// 设置NVIC分组 //NVIC_Group:NVIC 分组 0~4 总共 5 组 void MY_NVIC_PriorityGroupConfig(u8 NVIC_Group) { u32 temp,temp1; temp1=(~NVIC_Group)&0x07;//取后三位 temp1<<=8; temp=SCB->AIRCR; //读取先前的设置 temp&=0X0000F8FF; //清空先前分组 temp|=0X05FA0000; //写入钥匙 temp|=temp1; SCB->AIRCR=temp; //设置分组 }

搞了一天,其实就是在研究一句话 temp1=(~NVIC_Group)&0x07;//取后三位 为什么NVIC_Group要取反?和CM3分组不是反了吗?仔细查看《CM3权威指南》和对比《STM32不完全手册》可以发现,STM32是把CM3内核中第7分组定义为STM32的第0分组!原子哥撇开STM的库函数自己写,其实写的就是内核驱动,所以现在我们要控制的不是STM32,而是CM3,为了和STM32文档对应,那么我们应该对NVIC_Group取反!比如说我现在要用到STM32中的第1分组,其实是CM3中的第6分组,那我应该是把0x600写进CM3! 接下来是为什么STM32要对CM3的分组取反,即Crystal_oscillator说的MSB对齐。他给出了一个解释:通过让优先级以MSB 对齐,可以简化程序的跨器件移植。比如,如果一个程序早先在 支持4 位优先级的器件上运行,在移植到只支持3 位优先级的器件后,其功能不受影响。但 若是对齐到LSB,则会使MSB 丢失,导致数值大于7 的低优先级一下子升高了,甚至会反转小于等于7 的高优先级。如,8 号优先级因为损失了MSB,现在反而变成0号了! 我觉得这是一个原因,然后我又再查看了一下CM3,这时我们不烦假设自己是STM32的设计者,此时定义4位的优先级。

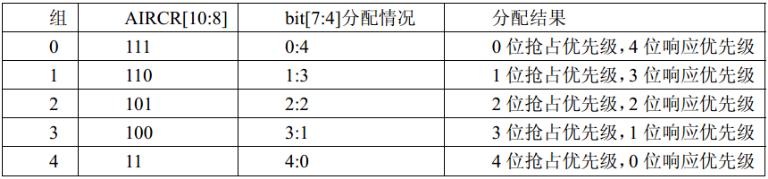

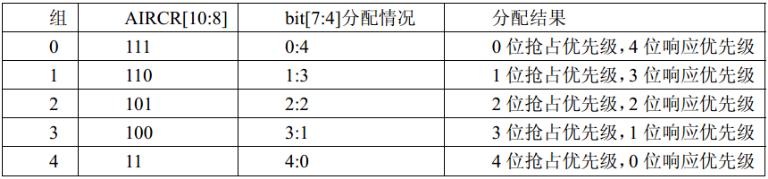

第一种方案,和STM32给的定义一样(对CM3的分组取反,并取寄存器高4位),得到以下结果:

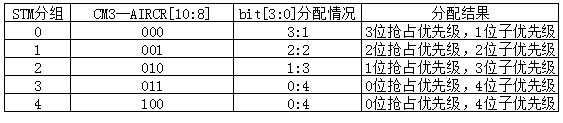

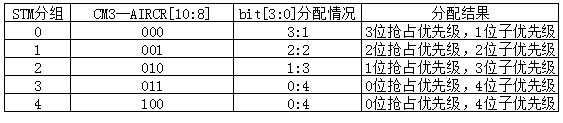

第二种方案,按照CM3的分组顺序,并取寄存器低4位(为什么不取高四位,自己写一下就明白了),得到以下结果:

CM3有个特别的规定,即8位寄存器中至少得有一位子优先级(响应优先级),所以造成两种分配方法的不同结果。如果按照第二种,那么STM32只存在4个分组。为什么选择第一种方案呢?个人觉得有以下原因:

1、存在0子优先级的分组。CM3规定,高级的抢占优先级可以打断低级的抢占优先级中断,而高级的子优先级并不具备打断低级子优先级的特权,所以4位子优先级的分组和4位抢占优先级的分组还是稍有不同的。这样提高了STM32的普适性,在某些情况下,可能需要用到4位抢占优先级!

2、如Crystal_oscillator所说的移植性问题。

对于这个问题,暂时先想到这里吧,继续下一个~时间不够啊~回来前还被老师批说STM32你们学的是库函数,没了库函数什么都干不了。原来原子哥前面教的是CM3内核的东西,难怪觉得有点晦涩。加油加油! 参考资料: 《CM3权威指南》 《STM32不完全手册》--正点原子@scut 《关于NVIC更深入的一点理解》--Crystal_oscillator http://bbs.ednchina.com/BLOG_ARTICLE_2092646.HTM

最近在看正点原子写的《STM32不完全手册》,sys.h有一个关于NVIC的分组函数My_NVIC_PriorityGroupConfig,该函数的参数NVIC_Group为要设置的分组号,可选范围为0~4,总共5组。My_NVIC_PriorityGroupConfig函数代码如下:

// 设置NVIC分组 //NVIC_Group:NVIC 分组 0~4 总共 5 组 void MY_NVIC_PriorityGroupConfig(u8 NVIC_Group) { u32 temp,temp1; temp1=(~NVIC_Group)&0x07;//取后三位 temp1<<=8; temp=SCB->AIRCR; //读取先前的设置 temp&=0X0000F8FF; //清空先前分组 temp|=0X05FA0000; //写入钥匙 temp|=temp1; SCB->AIRCR=temp; //设置分组 }

搞了一天,其实就是在研究一句话 temp1=(~NVIC_Group)&0x07;//取后三位 为什么NVIC_Group要取反?和CM3分组不是反了吗?仔细查看《CM3权威指南》和对比《STM32不完全手册》可以发现,STM32是把CM3内核中第7分组定义为STM32的第0分组!原子哥撇开STM的库函数自己写,其实写的就是内核驱动,所以现在我们要控制的不是STM32,而是CM3,为了和STM32文档对应,那么我们应该对NVIC_Group取反!比如说我现在要用到STM32中的第1分组,其实是CM3中的第6分组,那我应该是把0x600写进CM3! 接下来是为什么STM32要对CM3的分组取反,即Crystal_oscillator说的MSB对齐。他给出了一个解释:通过让优先级以MSB 对齐,可以简化程序的跨器件移植。比如,如果一个程序早先在 支持4 位优先级的器件上运行,在移植到只支持3 位优先级的器件后,其功能不受影响。但 若是对齐到LSB,则会使MSB 丢失,导致数值大于7 的低优先级一下子升高了,甚至会反转小于等于7 的高优先级。如,8 号优先级因为损失了MSB,现在反而变成0号了! 我觉得这是一个原因,然后我又再查看了一下CM3,这时我们不烦假设自己是STM32的设计者,此时定义4位的优先级。

第一种方案,和STM32给的定义一样(对CM3的分组取反,并取寄存器高4位),得到以下结果:

对于这个问题,暂时先想到这里吧,继续下一个~时间不够啊~回来前还被老师批说STM32你们学的是库函数,没了库函数什么都干不了。原来原子哥前面教的是CM3内核的东西,难怪觉得有点晦涩。加油加油! 参考资料: 《CM3权威指南》 《STM32不完全手册》--正点原子@scut 《关于NVIC更深入的一点理解》--Crystal_oscillator http://bbs.ednchina.com/BLOG_ARTICLE_2092646.HTM

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

直接上传吧。

一周热门 更多>