做个秒表 0-59

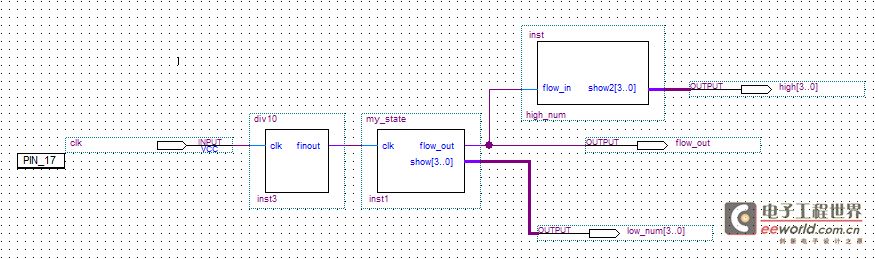

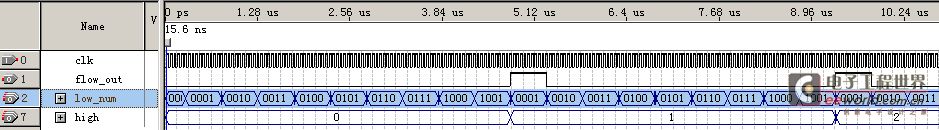

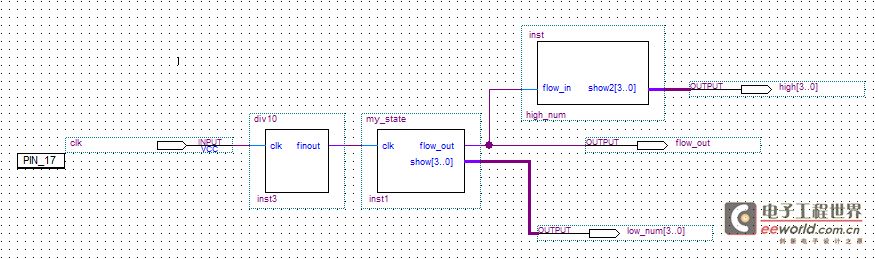

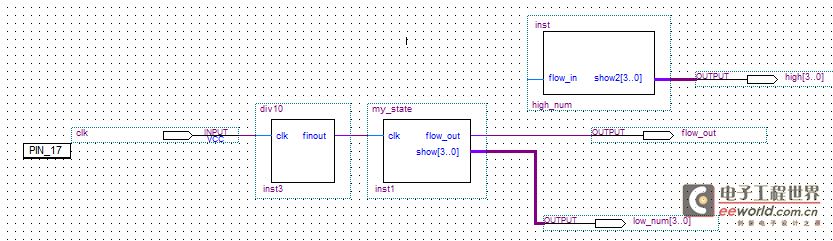

flow_out flow_in 连接时 的时序仿真结果如下

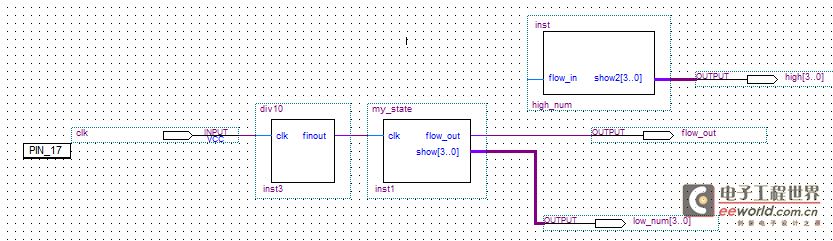

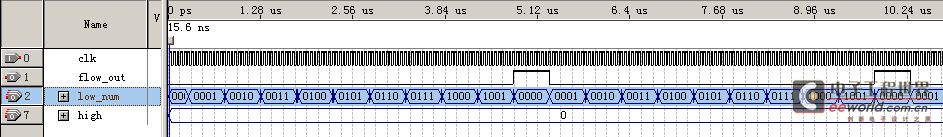

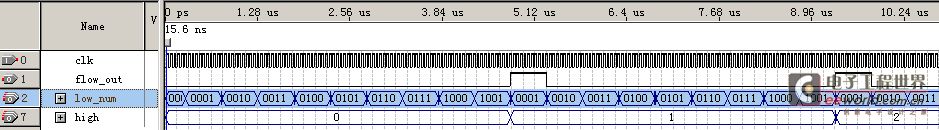

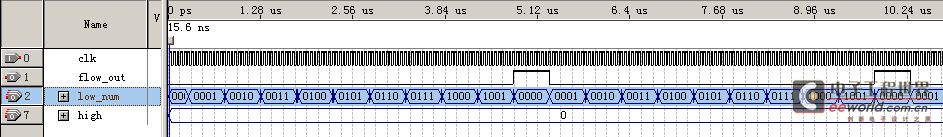

flow_out flow_in 不连接时 的时序仿真结果如下

请问为什么 flow_out 和flow_in 连接时 的结果里的 flow_out 是在low_num 为0001 时 有输出1而 flow_out和 flow_in 没连接时 的结果里的 flow_out 是在low_num 为0000 时 有输出1而 难道连接 flow_out和 flow_in 会影响前面一级的输出(flow_out)?附件是我的设计文件(求指教)因为state文件里少了个分频文件 现在更新为state2为 [ 本帖最后由 wzyuliyang 于 2011-12-20 16:29 编辑 ] 此帖出自小平头技术问答

flow_out flow_in 连接时 的时序仿真结果如下

flow_out flow_in 不连接时 的时序仿真结果如下

请问为什么 flow_out 和flow_in 连接时 的结果里的 flow_out 是在low_num 为0001 时 有输出1而 flow_out和 flow_in 没连接时 的结果里的 flow_out 是在low_num 为0000 时 有输出1而 难道连接 flow_out和 flow_in 会影响前面一级的输出(flow_out)?附件是我的设计文件(求指教)因为state文件里少了个分频文件 现在更新为state2为 [ 本帖最后由 wzyuliyang 于 2011-12-20 16:29 编辑 ] 此帖出自小平头技术问答

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity my_state is

port ( clk: in std_logic;

flow_out:out std_logic;

show:out std_logic_vector(3 downto 0));

end;

architecture one of my_state is

type mystate is (s0,s1,s2,s3,s4,s5,s6,s7,s8,s9,s10);

signal current_state,next_state :mystate;

begin

process (clk)

begin

flow_out<='0';

case current_state is

when s0=> show<="0000";next_state<=s1;

when s1=> show<="0001";next_state<=s2;

when s2=> show<="0010";next_state<=s3;

when s3=> show<="0011";next_state<=s4;

when s4=> show<="0100";next_state<=s5;

when s5=> show<="0101";next_state<=s6;

when s6=> show<="0110";next_state<=s7;

when s7=> show<="0111";next_state<=s8;

when s8=> show<="1000";next_state<=s9;

when s9=> show<="1001";next_state<=s10;

when s10=> show<="0000";next_state<=s1;flow_out<='1';

end case;

end process;

process(clk)

begin

if clk'event and clk='1' then

current_state<=next_state;

end if;

end process;

end;

而flow_out flow_in 连接时low_num输出为0 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2.....

问题解决了否?

一周热门 更多>