`timescale 1ns / 1ps

// synthesis translate_on

module ADC_TLC549 (

// inputs:

clk,

read_n,

// outputs:

AD_DATA,

AD_CS,

AD_CLK,

irq,

readdata

)

; input AD_DATA;

output AD_CS;

output AD_CLK;

output irq;

output [7: 0] readdata;

input read_n;

input clk;

wire AD_DATA;

reg AD_CLK_r;

reg [10:0] DCLK_DIV;

reg [4:0] COUNTER;

reg [7:0] data_temp;

reg [7:0] data_reg; wire [7: 0] readdata;

wire AD_CS; parameter CLK_FREQ = 'D50_000_000;//系统时钟50MHZ

parameter DCLK_FREQ = 'D1_000_000;//AD_CLK输出时钟1MHZ assign readdata = read_n ? 8'h00 : data_temp; always @(posedge clk)

if(DCLK_DIV < (CLK_FREQ / DCLK_FREQ))

DCLK_DIV <= DCLK_DIV+1'b1;

else

begin

DCLK_DIV <= 0;

AD_CLK_r <= ~AD_CLK_r;

end

always @(posedge AD_CLK_r)

COUNTER <= COUNTER+1'b1; /*AD_CS建立时间较长,从COUNER[0]开始使能*/

assign AD_CS = COUNTER <= 'd9 ? 1'b0 : 1'b1; /*COUNER[2]开始输出8个采集时钟*/

assign AD_CLK_EN = (COUNTER >= 'd2 && COUNTER <= 'd9) ? 1'b1 : 1'b0;

assign AD_CLK = AD_CLK_EN ? AD_CLK_r : 1'b1; /*采集完毕输出一个中断请求,中断请求不是必需的*/

assign irq = (COUNTER == 'd10) ? 1'b1 : 1'b0;

always @(negedge AD_CLK_r)

if(AD_CLK_EN)

begin

data_reg[0] <= AD_DATA;

data_reg[7:1] <= data_reg[6:0];//串并转换

end

else

data_temp <= data_reg ;

//control_slave, which is an e_avalon_slave endmodule

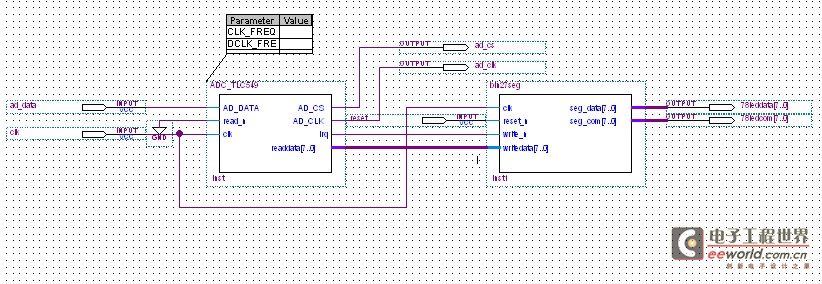

这个是实现AD转换的。

module bin27seg(clk,reset_n,write_n,writedata,seg_data,seg_com);

input clk;

input reset_n;

//input chipselect;

input write_n; input [7:0]writedata;

output [7:0]seg_data;

output [7:0]seg_com; reg [7:0]outdata;

reg [7:0]datain[7:0];

reg [7:0]seg_com;

reg [7:0]seg_data;

reg [7:0]bcd_led;

reg [36:0]count;

reg [31:0] writedata_r;

always @(negedge reset_n or posedge clk)

begin

if(!reset_n)

begin

datain[0]<=8'b00000000;

datain[1]<=8'b00000000;

datain[2]<=8'b00000000;

datain[3]<=8'b00000000;

datain[4]<=8'b00000000;

datain[5]<=8'b00000000;

datain[6]<=8'b00000000;

datain[7]<=8'b00000000;

end

else if(!write_n)

begin

writedata_r = writedata*12'd2500/9'd256;

/*

datain[0]<=writedata_r[3:0];

datain[1]<=writedata_r[7:4];

datain[2]<=writedata_r[11:8];

datain[3]<=writedata_r[15:12];*/

datain[0]<=writedata_r%10;

datain[1]<=writedata_r/10%10;

datain[2]<=writedata_r/100%10;

datain[3]<=writedata_r/1000%10;

end

end always @(posedge clk)

begin

count=count+1;

end always @(count[14:12])

begin

case(count[14:12])

3'b000:

begin

bcd_led = datain[0];

seg_com = 8'b1111_1110;

end

3'b001:

begin

bcd_led=datain[1];

seg_com=8'b1111_1101;

end

3'b010:

begin

bcd_led=datain[2];

seg_com=8'b1111_1011;

end

3'b011:

begin

bcd_led=datain[3];

seg_com=8'b1111_0111;

end

3'b100:

begin

bcd_led=datain[4];

seg_com=8'b1110_1111;

end

3'b101:

begin

bcd_led=datain[5];

seg_com=8'b1101_1111;

end

3'b110:

begin

bcd_led=datain[6];

seg_com=8'b1011_1111;

end

3'b111:

begin

bcd_led=datain[7];

seg_com=8'b0111_1111;

end

endcase end always @(seg_com or bcd_led)

begin

case(bcd_led[3:0])

4'h0:seg_data=8'hc0;

4'h1:seg_data=8'hf9;

4'h2:seg_data=8'ha4;

4'h3:seg_data=8'hb0;

4'h4:seg_data=8'h99;

4'h5:seg_data=8'h92;

4'h6:seg_data=8'h82;

4'h7:seg_data=8'hf8;

4'h8:seg_data=8'h80;

4'h9:seg_data=8'h90;

4'ha:seg_data=8'h88;

4'hb:seg_data=8'h83;

4'hc:seg_data=8'hc6;

4'hd:seg_data=8'ha1;

4'he:seg_data=8'h86;

4'hf:seg_data=8'h8e;

endcase

end endmodule

这个是板子要求把结果显示在LED上面。 原理图我也附上来了~第一段代码中颜 {MOD}标记的就是看不懂的,第二个代码就是彻底不懂什么意思了~再次谢谢大家了~

此帖出自小平头技术问答

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

先说第一个问题:我感觉它输出的是500K的AD_CLK,不是1M.电路先计50个时钟周期的clk,假如这段时间AD_CLK是高,电路再计50个时钟周期的clk,那么这段时间的AD_CLK就是低了,AD_CLK的周期就是100个时钟周期,那么一算就是50M/100=500K的AD_CLK. 等下大家一起来解决这个问题。

明天来看第二个问题,现在太困了,呵呵 。已经23.:32了。

[ 本帖最后由 江汉大学南瓜 于 2011-8-12 09:27 编辑 ]一周热门 更多>