QQ截图20180605200720.jpg (193.31 KB, 下载次数: 0)

下载附件

2018-6-5 20:05 上传

QQ截图20180605200720.jpg (193.31 KB, 下载次数: 0)

下载附件

2018-6-5 20:05 上传

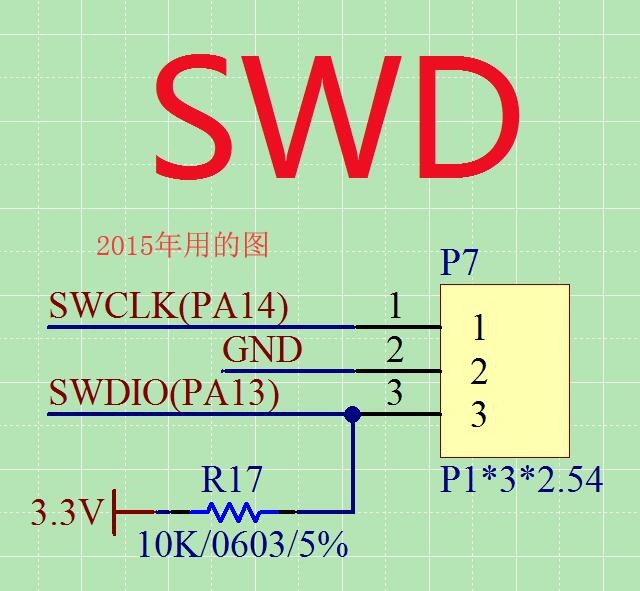

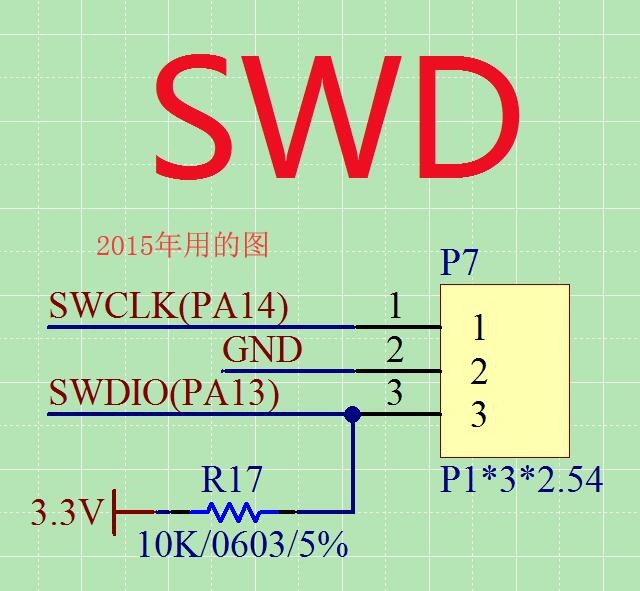

后来对SWDIO SWDCLK都上拉了,下载程序也很小心,三年来都没坏过。

现在在设计一个新板子,考虑对SWD口加ESD,避免不小心带电插拔时候打坏。。

这个ESD,用5V的合适 还是3.3V的合适?

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

QQ截图20180605200720.jpg (193.31 KB, 下载次数: 0)

下载附件

2018-6-5 20:05 上传

QQ截图20180605200720.jpg (193.31 KB, 下载次数: 0)

下载附件

2018-6-5 20:05 上传

当时做了失效实验了。

100%确定就是SWD的带电插拔时候搞坏的。

同用429,没加电阻上拉,加了ESD(有时候焊接不好的就直接去除了),一个也没坏过

这种TVS一般都已经有这种考虑,3V3的,Breakdown的电压最低是5V的。

不知道你用的什么型号的,会出现你描述的这种情况。

QQ截图20180606202638.jpg (316.61 KB, 下载次数: 0)

下载附件

2018-6-6 20:24 上传

一周热门 更多>