大致简介:

小弟最近在看<<权威指南>>,想稍微深入点了解下cm3/cm4内核机制,遇到如下问题,恳请指教...

开发环境:

stm32f103zet6+mdk5.14 硬件仿真

具体问题:

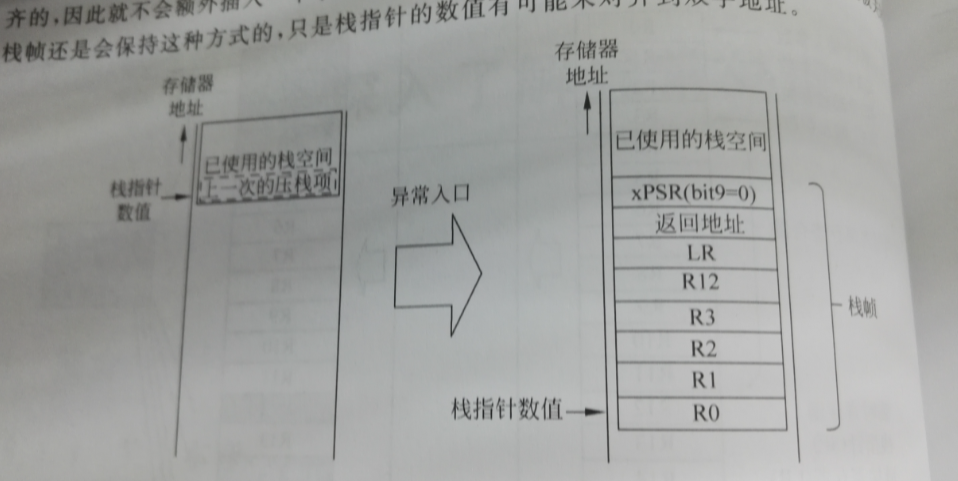

<<权威指南>>上说,进入异常/中断时的压栈顺序如下图(暂时不考虑浮点寄存器):

001.png (124.65 KB, 下载次数: 0)

下载附件

2017-5-31 17:27 上传

001.png (124.65 KB, 下载次数: 0)

下载附件

2017-5-31 17:27 上传

第一张图:

xPSR->XXX->XXX->R12->R3->R2->R1->R0

问题1: XXX XXX 分别是指什么啊???

问题2: EXC_RETURN搞哪去了???

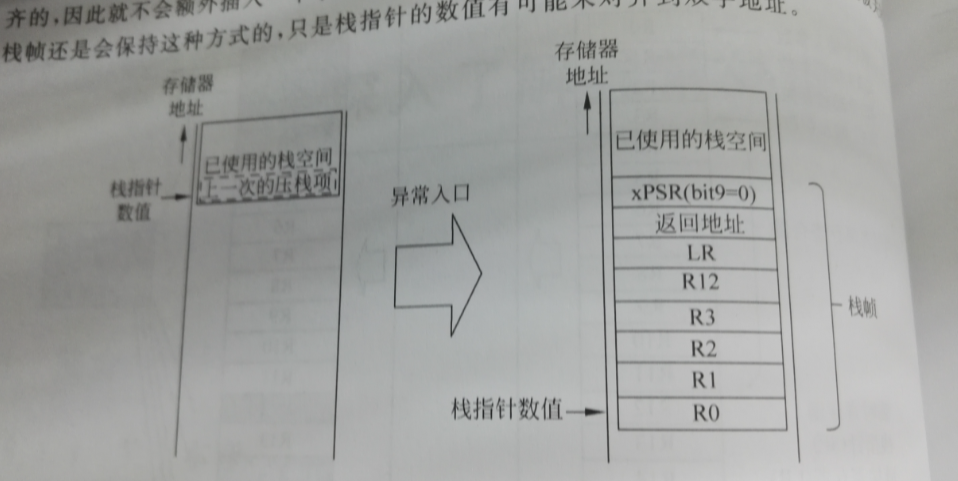

第二张图:

问题3: 此时都已经进入ISR服务函数内部,现在才存储EXC_RETURN?会不会太晚?

问题4: 如果是这样的话,那总共压栈的字内存就已经超过8字了(计算不考虑压入的R8-R4用作保存局部变量,那总共压栈的字数也有9个字了啊)?

恳请大神指教~~~

小弟最近在看<<权威指南>>,想稍微深入点了解下cm3/cm4内核机制,遇到如下问题,恳请指教...

开发环境:

stm32f103zet6+mdk5.14 硬件仿真

具体问题:

<<权威指南>>上说,进入异常/中断时的压栈顺序如下图(暂时不考虑浮点寄存器):

001.png (124.65 KB, 下载次数: 0)

下载附件

2017-5-31 17:27 上传

001.png (124.65 KB, 下载次数: 0)

下载附件

2017-5-31 17:27 上传

第一张图:

xPSR->XXX->XXX->R12->R3->R2->R1->R0

问题1: XXX XXX 分别是指什么啊???

问题2: EXC_RETURN搞哪去了???

第二张图:

问题3: 此时都已经进入ISR服务函数内部,现在才存储EXC_RETURN?会不会太晚?

问题4: 如果是这样的话,那总共压栈的字内存就已经超过8字了(计算不考虑压入的R8-R4用作保存局部变量,那总共压栈的字数也有9个字了啊)?

恳请大神指教~~~

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

1> 大神说的应该是正确的,入栈保存8个字,分别应该是xPSR->PC(返回地址)->LR->R12->R3->R2->R1->R0

2>从图1和图2的的汇编创口根本找不到压栈汇编代码,可见这部分是由编译器自动完成的.出栈应该也是同样的道理.

3>只要进入异常/中断,上述8个寄存器是必须压入堆栈的,这个是"官方标配",如果在ISR内部需要使用局部变量或者再次进行函数调用,就需要额外保存寄存器,这属于"豪华套餐".

4>图1中将LR进行保存,是因为图1中ISR内部有函数调用,会再次使用LR,所以需要将LR的值进行保存,而图2中就不需要...

如果有理解错误的地方,还请大神继续指教,谢谢了...

001.png (100.39 KB, 下载次数: 0)

下载附件

2017-6-1 15:54 上传

第4点的理解是不对的~~

一周热门 更多>