本帖最后由 习学发开 于 2015-4-22 19:36 编辑

菜鸟,更多的都是书本知识,实践少,如果有重大错误实属正常,希望大家理解!

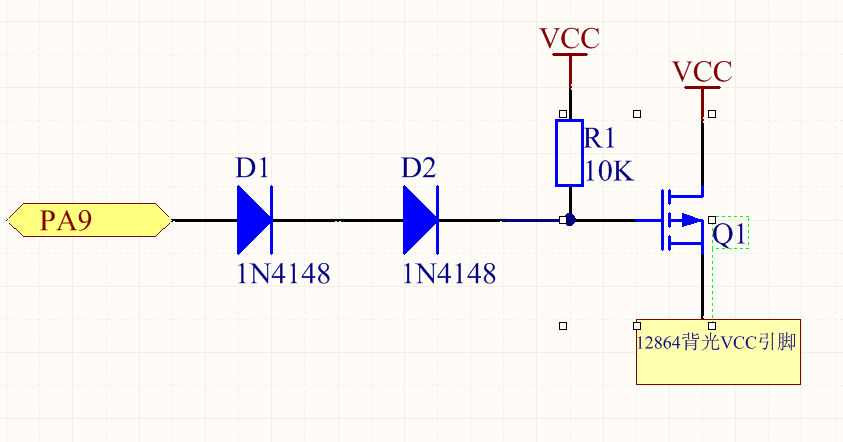

背光控制方案.PNG (24.79 KB, 下载次数: 0)

下载附件

2015-4-22 17:10 上传

背光控制方案.PNG (24.79 KB, 下载次数: 0)

下载附件

2015-4-22 17:10 上传

另外就是管子符号貌似不对,我在AD自带的杂项库里面找了半天,只找到这个。

管子是PMOS SI2301,估计大家也都看出来了。

菜鸟,更多的都是书本知识,实践少,如果有重大错误实属正常,希望大家理解!

背光控制方案.PNG (24.79 KB, 下载次数: 0)

下载附件

2015-4-22 17:10 上传

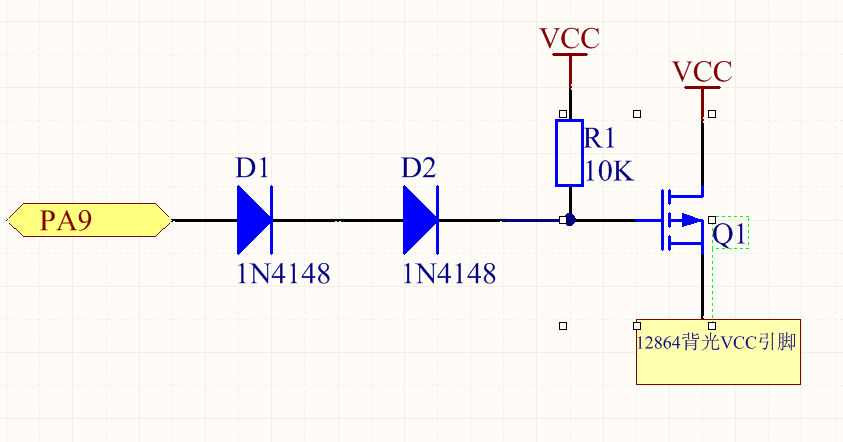

背光控制方案.PNG (24.79 KB, 下载次数: 0)

下载附件

2015-4-22 17:10 上传

另外就是管子符号貌似不对,我在AD自带的杂项库里面找了半天,只找到这个。

管子是PMOS SI2301,估计大家也都看出来了。

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

q1的G是对vcc上拉的,可以认为是vcc

pa9拉低后可以认为是0

你觉得呢 G会变低吗

逻辑低有效的输入引脚,为了防止悬空而出现未定的情况而拉一个上拉电阻,

是非常常见的做法吧? 集成电路那么多FET可以那么做,为什么单个MOSFET就不行了呢?

反正我是风中凌乱了~~

另外弱弱问下,设G极电压为Vg,按我的接法,

PA输出低电平,也就是一个非常接近0V的

电压之后,Vg大概是在多少范围之内?

其实你可以这样改

谢谢,我把上拉电阻和二极管都去掉可以吗?

一周热门 更多>