最近在做一个异步的fifo,有一些疑问想请教大家:

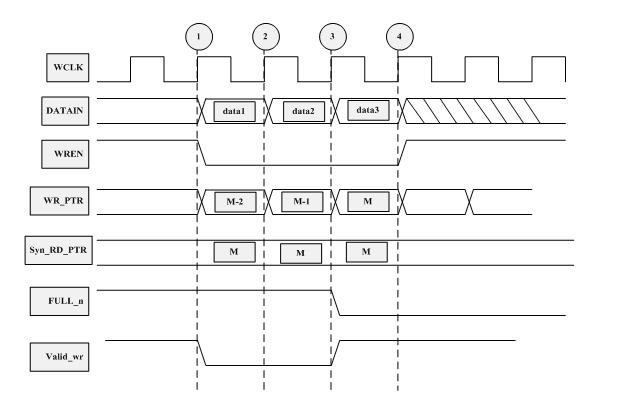

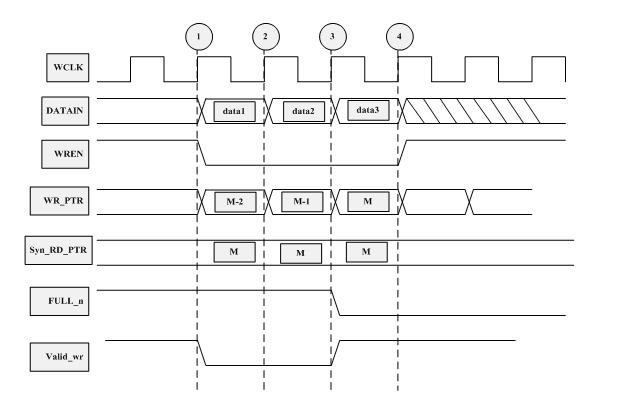

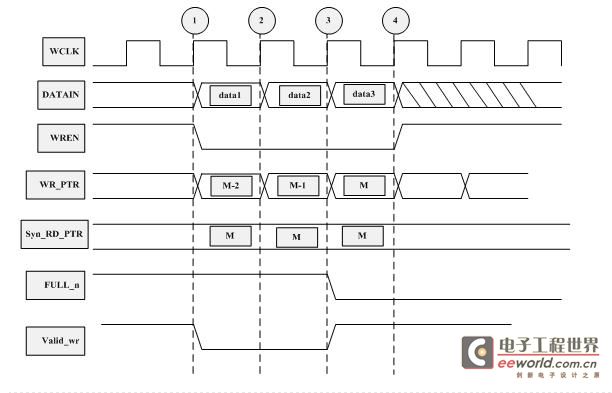

首先,我使用的SRAM模型是这样的:在写时钟wrclk的上升沿检测写使能valid_wr,如果有效,则在相应的地址wraddr中写入数据datain,在读时钟rclk的上升沿检测读使能valid_rd,如果有效,则读出相应地址raddr的数据dataout。(valid_wr和使能wr_en及full_n有关,valid_rd和使能rd_en及empty_n有关),我在空满标志位产生上有一个疑问,比如说写数据吧,如下图所示:

在这个图中,假设只写数据没有读数据,假设外部总线其所发出的数据为DATAIN和WREN,(注意到所给数据只在clk的上升沿变化),在clk第一个上升沿(如图)发送第一个数据,此时wr_ptr为M-2,而同步后的读指针syn_rd_ptr为M,且不变,在第二个上升沿fifo检测到rwen,并且full无效且valid_wr有效,则写入数据data1,wr_ptr加1变为M-1,full不变,与此同时外部总线检测(也在上升沿,即在clk2这点)full,没有满,则继续发数据data2,注意,这时候两个指针只差一个,在第3个clk上升沿,fifo检测到wr_en,且valid_wr有效,则写入data2,而由于写信号引起了指针相等,则此时ful有效,即表示fifo满了,问题来了,此时(clk3上升沿)外部总线要检测full信号以决定是否继续发数据,但监测点full为高,即表示未满,则外部总线还可以继续发送数据,而此时valid_wr已经无效,数据不会写进SRAM中。我就很奇怪,这样做确实可以防止fifo被重复写,但总线上发出的数据并没有被写进去,好像丢了一样,我自己分析是不是总线在检测full信号时并不是在上升沿去做,如果在下降沿来检测full信号,则就可以看到full的变化,在上图中就是wr_en和data_in都向后推半个周期,这样就看似合理了,就像iic总线中主机和从机的关系那样,主机下降沿发数据,从机上升沿接数据,但现在的电路中很少使用双沿,搞不明白,还请大家帮助一下。

最近在做一个异步的fifo,有一些疑问想请教大家:

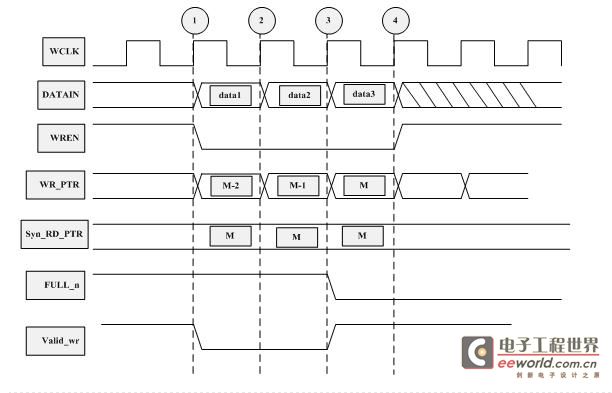

首先,我使用的SRAM模型是这样的:在写时钟wrclk的上升沿检测写使能valid_wr,如果有效,则在相应的地址wraddr中写入数据datain,在读时钟rclk的上升沿检测读使能valid_rd,如果有效,则读出相应地址raddr的数据dataout。(valid_wr和使能wr_en及full_n有关,valid_rd和使能rd_en及empty_n有关),我在空满标志位产生上有一个疑问,比如说写数据吧,如下图所示:

在这个图中,假设只写数据没有读数据,假设外部总线其所发出的数据为DATAIN和WREN,(注意到所给数据只在clk的上升沿变化),在clk第一个上升沿(如图)发送第一个数据,此时wr_ptr为M-2,而同步后的读指针syn_rd_ptr为M,且不变,在第二个上升沿fifo检测到rwen,并且full无效且valid_wr有效,则写入数据data1,wr_ptr加1变为M-1,full不变,与此同时外部总线检测(也在上升沿,即在clk2这点)full,没有满,则继续发数据data2,注意,这时候两个指针只差一个,在第3个clk上升沿,fifo检测到wr_en,且valid_wr有效,则写入data2,而由于写信号引起了指针相等,则此时ful有效,即表示fifo满了,问题来了,此时(clk3上升沿)外部总线要检测full信号以决定是否继续发数据,但监测点full为高,即表示未满,则外部总线还可以继续发送数据,而此时valid_wr已经无效,数据不会写进SRAM中。我就很奇怪,这样做确实可以防止fifo被重复写,但总线上发出的数据并没有被写进去,好像丢了一样,我自己分析是不是总线在检测full信号时并不是在上升沿去做,如果在下降沿来检测full信号,则就可以看到full的变化,在上图中就是wr_en和data_in都向后推半个周期,这样就看似合理了,就像iic总线中主机和从机的关系那样,主机下降沿发数据,从机上升沿接数据,但现在的电路中很少使用双沿,搞不明白,还请大家帮助一下。

此帖出自

小平头技术问答

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

读写FIFO 或SRAM 把握以下两个原则,保证你没任何问题:

1。 写FIFO 或SRAM 时, 写信号,数据和地址 同时有效, 数据在一个时钟周期就可以写入FIFO或SRAM;

2. 读FIFO或SRAM 时,读信号,地址同时有效,数据在延迟一个系统时钟周期,数据有效。

一周热门 更多>