本帖最后由 huangyiting1990 于 2013-9-15 15:40 编辑

如题!第一行是时钟信号。第二行是数据,第三行是锁存。驱动74HC595,上一级的程序无法改变,下级的数码管需要更换,所以我只想到在中间级加一个译码似的MCU。但是这个信号太快了,几天了一直苦于无法读取这个波形,贴上来大家出出主意。

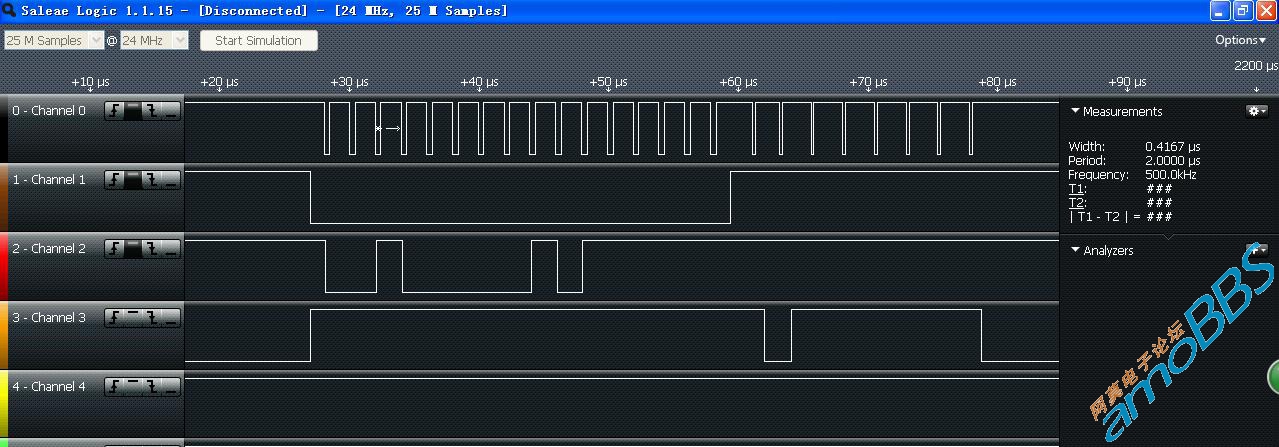

第一张图的信号依次是:1时钟 2:锁存 3:595数据 4 165数据

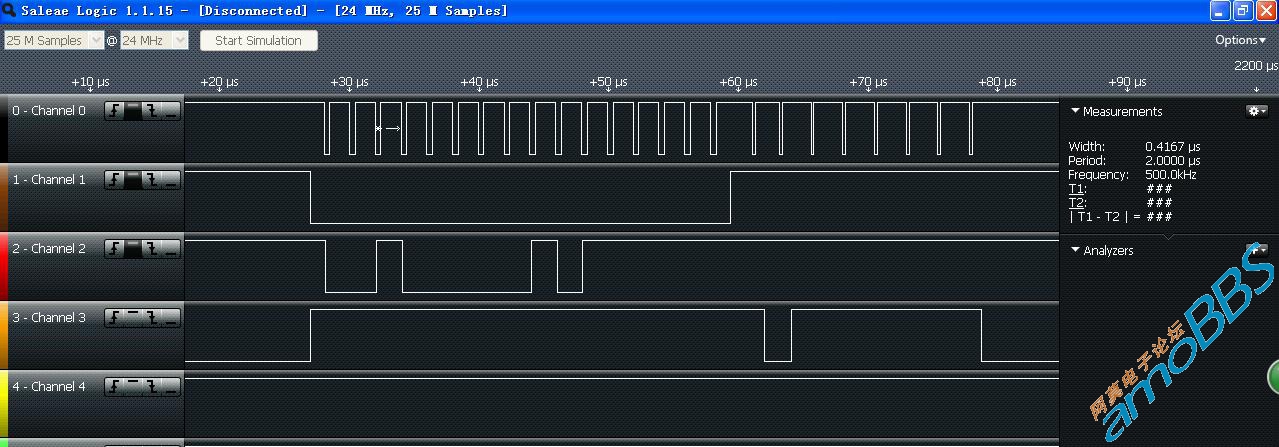

第二张图的信号一次是:1时钟 2:595数据 3:锁存

微博桌面截图_20130915150800.jpg (340.82 KB, 下载次数: 8)

下载附件

2013-9-15 15:13 上传

微博桌面截图_20130915150800.jpg (340.82 KB, 下载次数: 8)

下载附件

2013-9-15 15:13 上传

更新点我的发现:

我观察了一下我的上级板子上的电路 总共有6条线下来:1电源 2 时钟 3 595锁存 4 595数据 5 74HC165数据 6 GND 而且上级板子上用的是STC11F40 (22.1184M晶振,而且所用管脚都是P2 一般IO口)而我想在下级用STC的11f02(33.1776M晶振)来接收上级的595数据应该也是行的通的呀。结果3天了还是没头绪。再问问看 大家 说说上一级的板子是怎么来接收165的数据的呢?(时钟信号都一样呀)

如题!第一行是时钟信号。第二行是数据,第三行是锁存。驱动74HC595,上一级的程序无法改变,下级的数码管需要更换,所以我只想到在中间级加一个译码似的MCU。但是这个信号太快了,几天了一直苦于无法读取这个波形,贴上来大家出出主意。

第一张图的信号依次是:1时钟 2:锁存 3:595数据 4 165数据

第二张图的信号一次是:1时钟 2:595数据 3:锁存

微博桌面截图_20130915150800.jpg (340.82 KB, 下载次数: 8)

下载附件

2013-9-15 15:13 上传

微博桌面截图_20130915150800.jpg (340.82 KB, 下载次数: 8)

下载附件

2013-9-15 15:13 上传

更新点我的发现:

我观察了一下我的上级板子上的电路 总共有6条线下来:1电源 2 时钟 3 595锁存 4 595数据 5 74HC165数据 6 GND 而且上级板子上用的是STC11F40 (22.1184M晶振,而且所用管脚都是P2 一般IO口)而我想在下级用STC的11f02(33.1776M晶振)来接收上级的595数据应该也是行的通的呀。结果3天了还是没头绪。再问问看 大家 说说上一级的板子是怎么来接收165的数据的呢?(时钟信号都一样呀)

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

对于FPGA一窍不通,只玩过51,现在入手大概多长周期?

如果对FPGA一窍不通,还有没其他方法?

好想法

一周热门 更多>