1概述

1概述 基于Vivado的板级调试介绍,可以参考文档《玩转Zynq-基础篇:基于Vivado的在线板级调试概述.pdf》。这里我们以zstar_ex55工程为例,对FPGA的Virtual IO(简称VIO)使用进行介绍和实战操练。

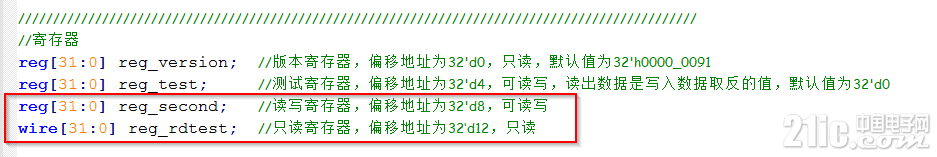

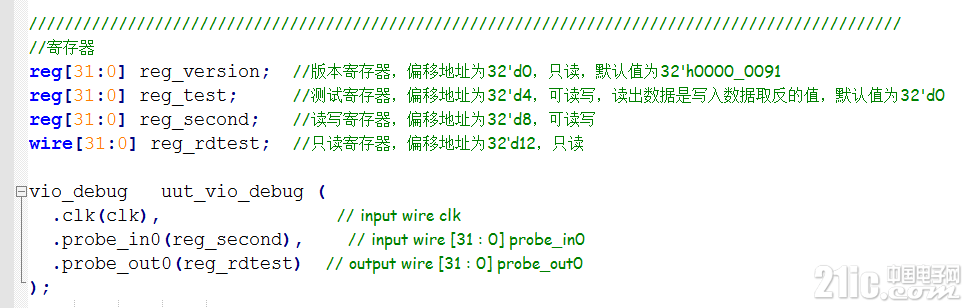

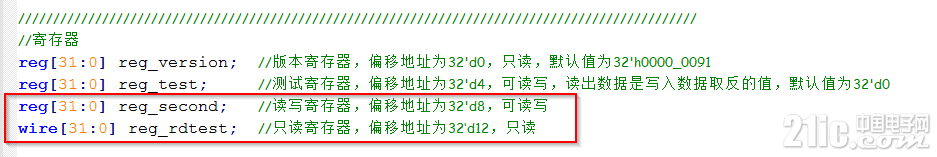

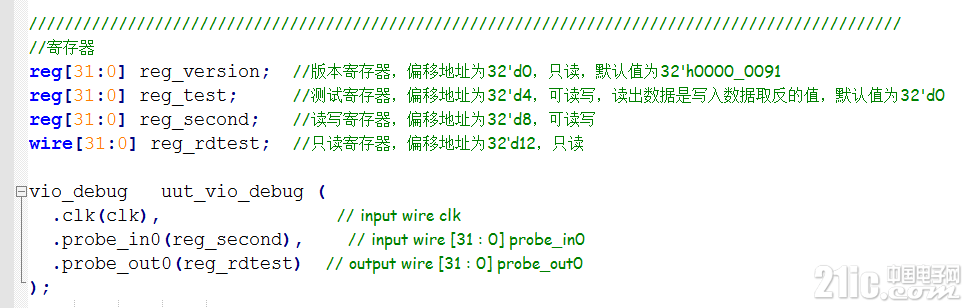

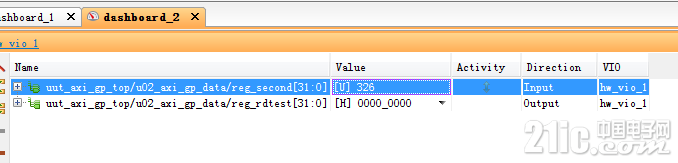

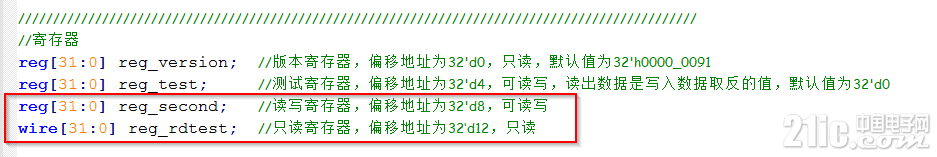

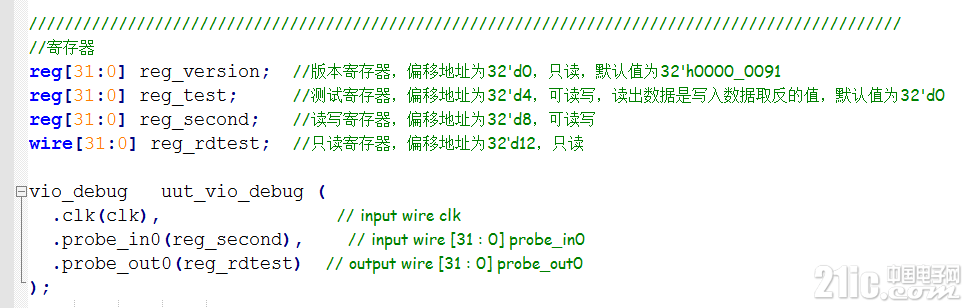

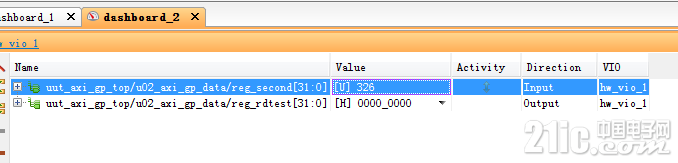

2 探测阶段 识别出VIO的待探测信号如图所示,对于VIO而言,reg_rdtest是我们要写入到axi_gp_data.v模块的信号;reg_second则是我们从axi_gp_data.v模块读出的数据。换句话说,如果我们要使用VIO探测这些信号,reg_rdtest就是我们要从VIO中产生的信号(VIO的output);reg_second就是我们在VIO上显示的信号(VIO的input)。

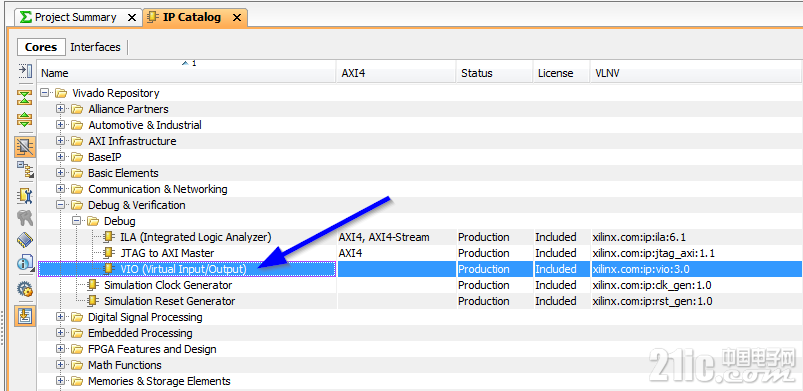

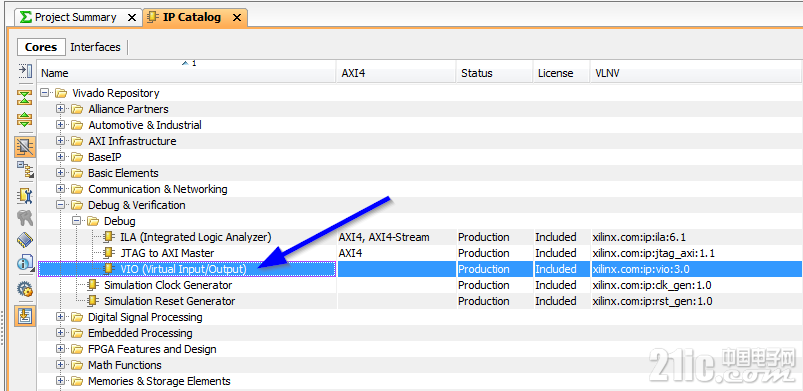

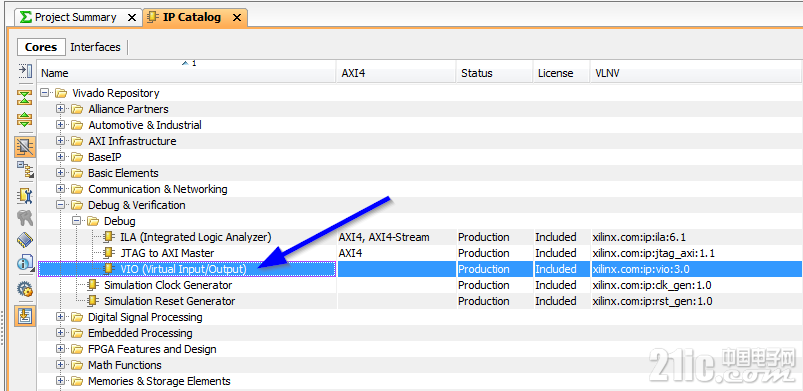

图识别出探测信号 如图所示,在IP Catalog中点击Debug & Verification --> Debug -->VIO(Virtual Input/Output)开启VIO的IP核配置页面。

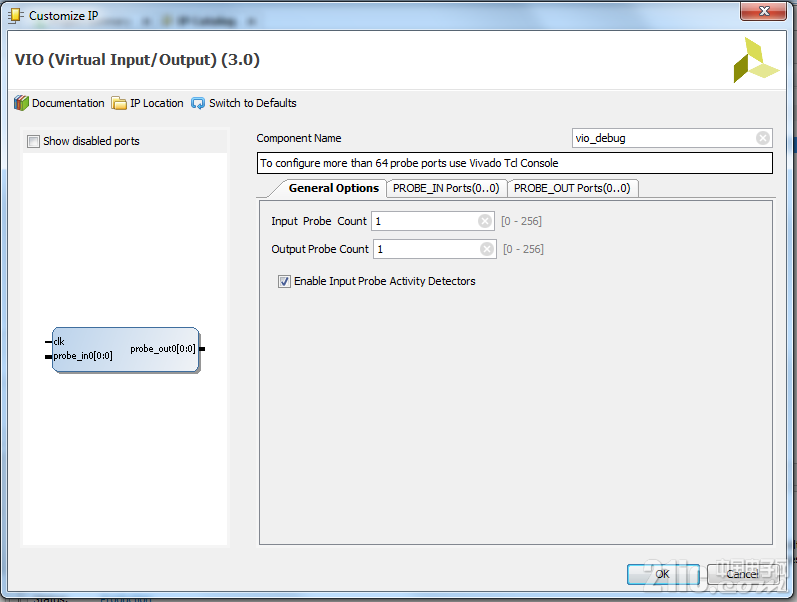

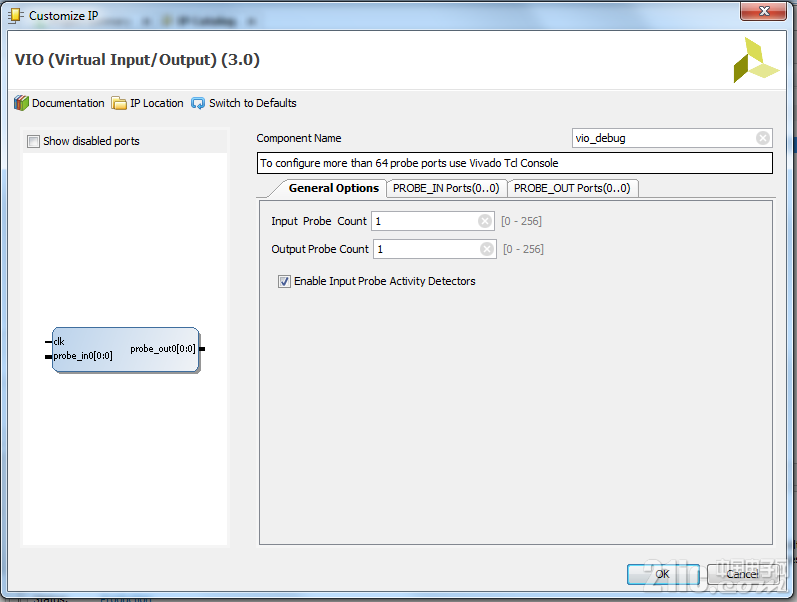

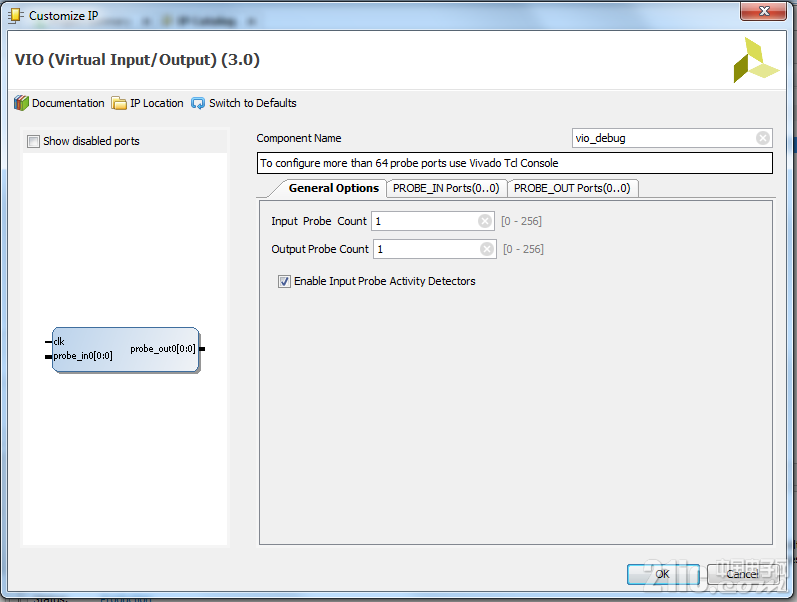

图 VIO IP核 如图所示,VIO配置页面中,General Options中设定Input Probe Count的数量,即FPGA中output到VIO中进行观察显示的信号数量(每个信号的位宽可以在PROBE_IN Ports中设置);同时设定OutputProbe Count的数量,即需要送到FPGA中进行实时变化的信号数量(每个信号的位宽可以在PROBE_OUTPorts中设置)。reg_second这个信号是input probe,因此设置Input Probe Count为1;reg_rdtest这4个信号是output probe,因此设置Output Probe Count也为1。

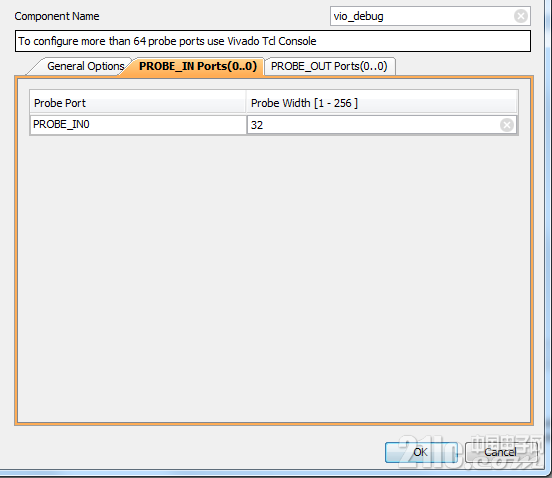

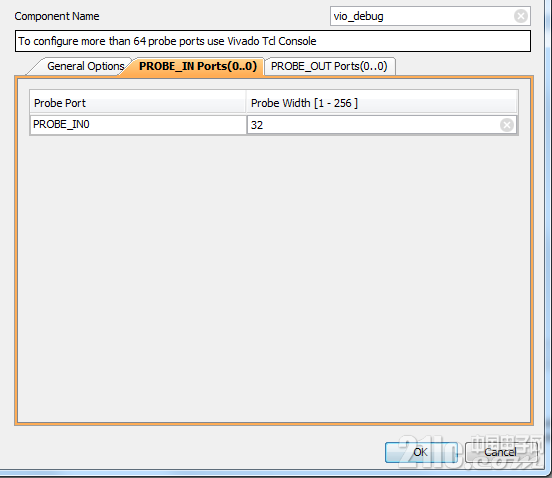

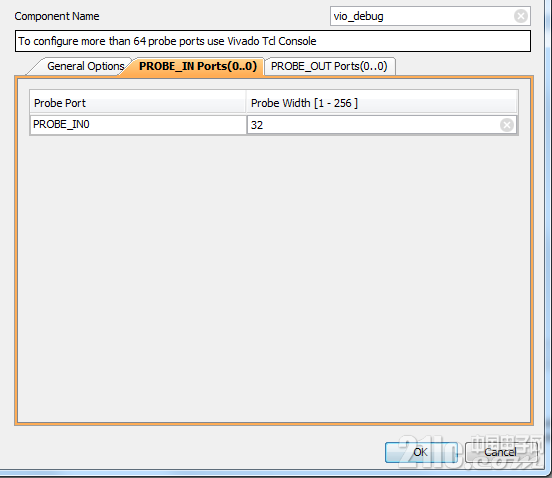

图 VIO配置的General Options页面 如图所示,在PROBE_INPorts中可以设置每个input信号的位宽,reg_second这个input port的位宽是32,因此设定PROBE_IN0的位宽为32。

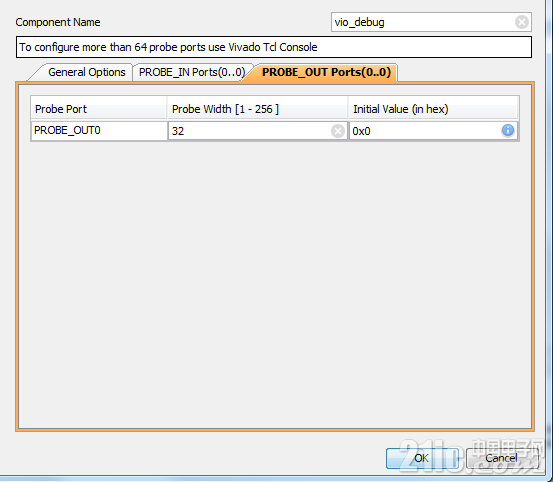

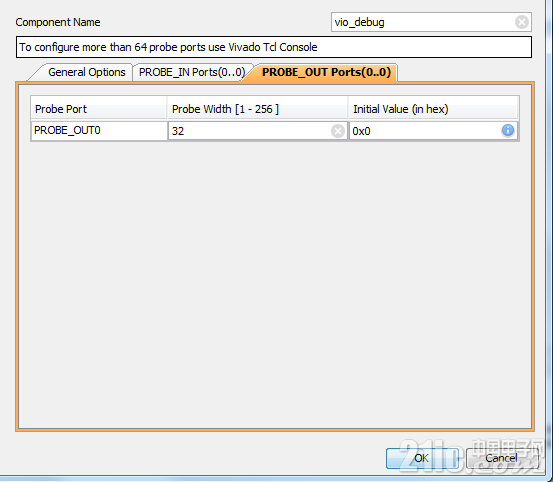

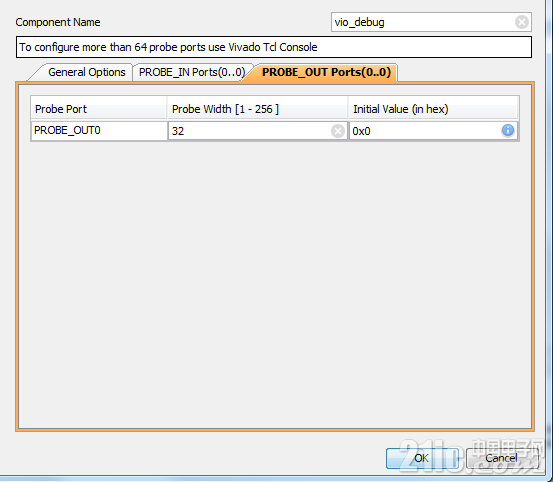

图 VIO配置的PROBE_IN Ports页面 如图所示,在PROBE_OUTPorts中可以设置每个output信号的位宽。reg_rdtest的位宽是32,因此设置PROBE_OUT0的位宽是32。

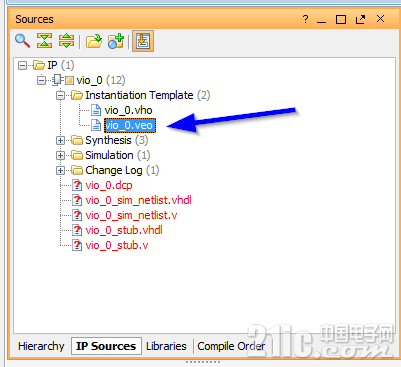

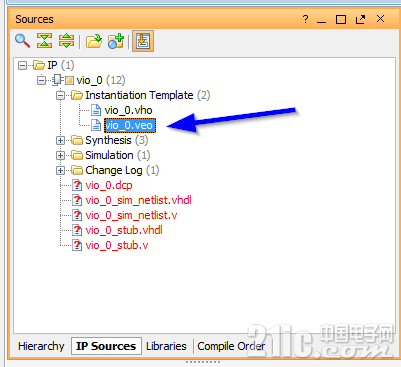

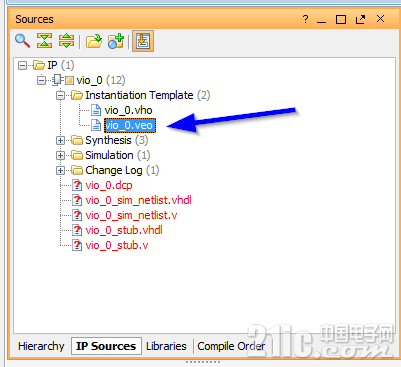

图 VIO配置的PROBE_OUT Ports页面 如图所示,在Source -->IP Sources下,可以看到出现了vio_0的IP,Instantiation Template展开后可以看到有VHDL和Verilog两种版本的例化模板。

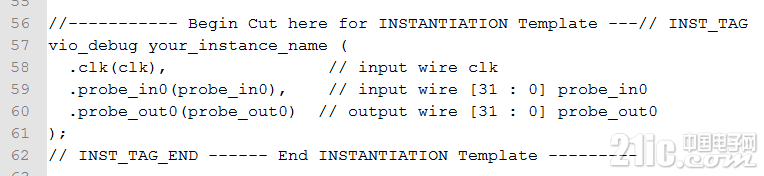

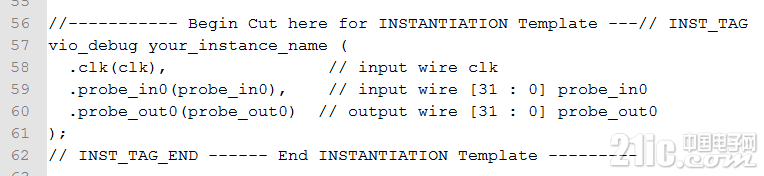

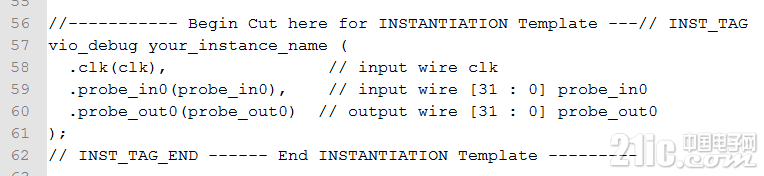

图VIO例化模板文件 例化模板文件的代码如图所示。复制例化模板的代码,修改对应括号内的信号名称和FPGA系统中的匹配,就完成了VIO的代码集成。

图例化模板文件代码 如图所示,在模块axi_gp_data.v中,例化VIO模块如下。

图例化VIO IP核模块

3 实现阶段 完成VIO的基本配置和IP核例化后,对工程进行全编译,生成bit文件。

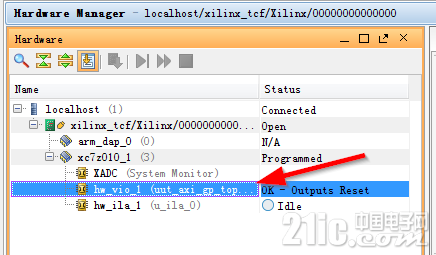

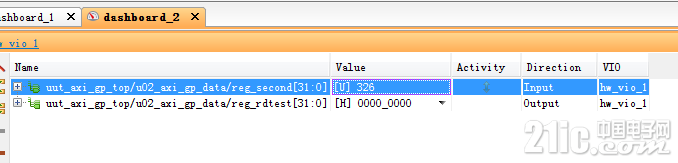

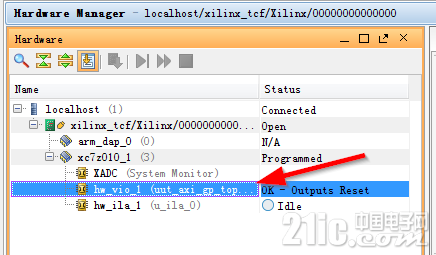

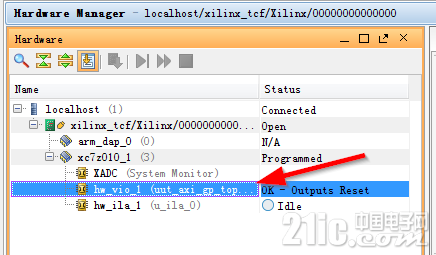

4 分析阶段 如图所示,将工程编译产生的.bit文件下载到FPGA中,并将嵌入式软件产生的.elf文件在处理器上运行起来。 如图所示,在HardwareManager --> Hardware下,双击打开hw_vio_1,即例化的VIO的调试界面。

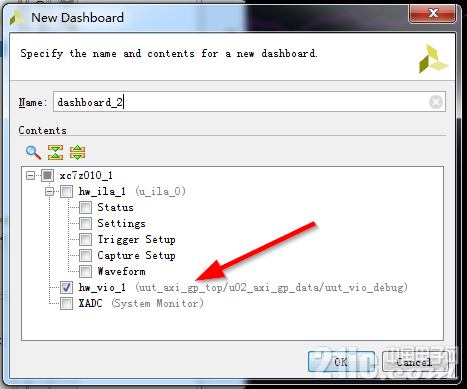

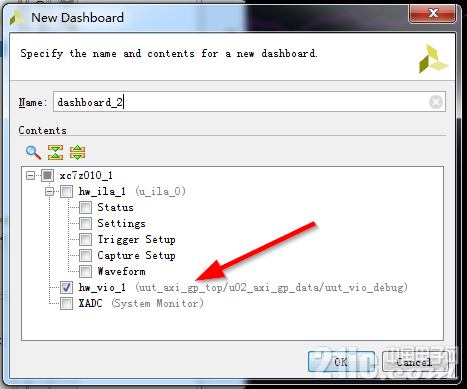

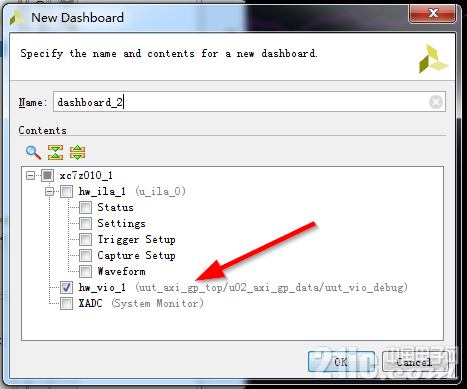

图 Hardware窗口 弹出的New Dashboard对话框中,如图所示,勾选hw_vio_1,点击OK。

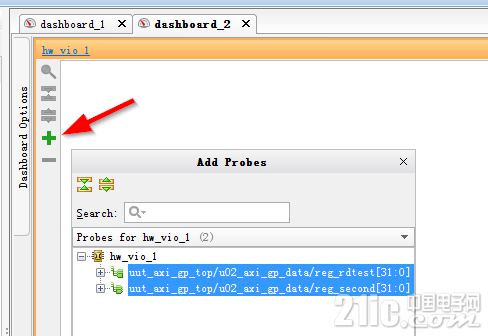

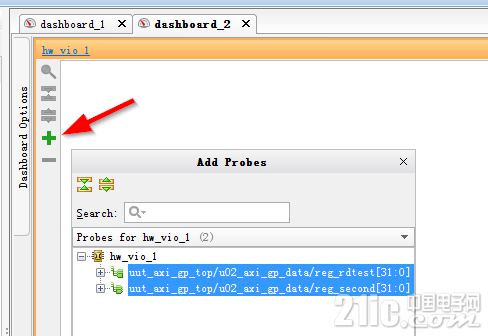

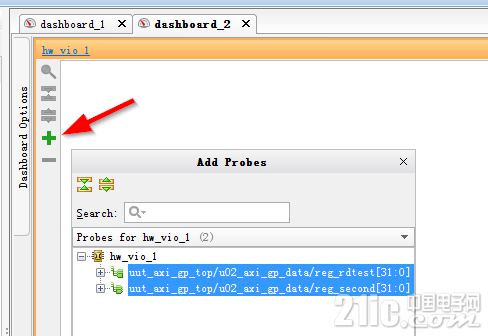

图 New Dashboard对话框 如图所示,在dashboard_2界面中,点击左侧的“+”号,弹出Add Probes中,选中所有的信号,点击OK。就将所有的VIO连接好的信号添加到dashboard_2的调试界面中。

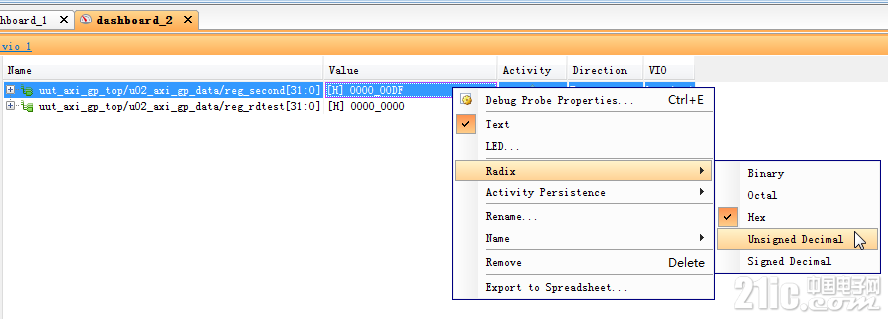

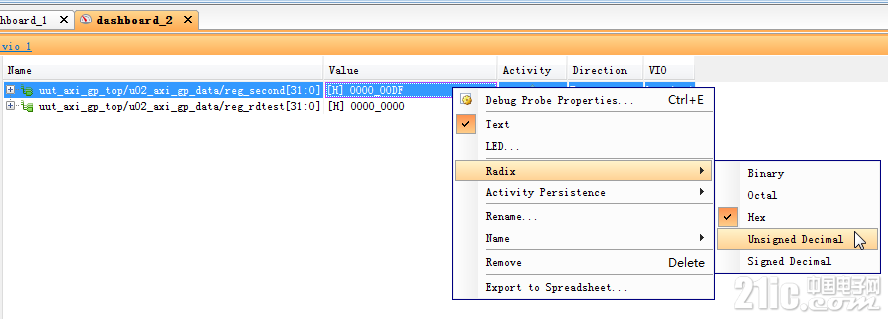

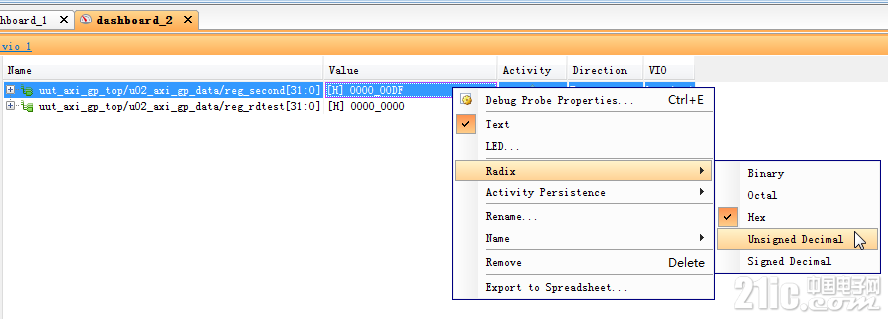

图添加可用的VIO接口信号 如图所示,点击选中信号名所在行,右键单击,在弹出菜单中点击Radix就可以看到所有支持的Vaule显示进制,可以点击UnsignedDecimal,即无符号十进制。

此时,reg_second寄存器就以十进制显示每秒递增1的数据。

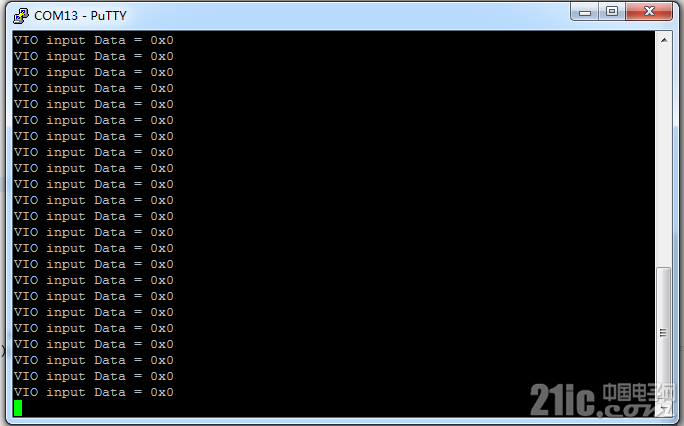

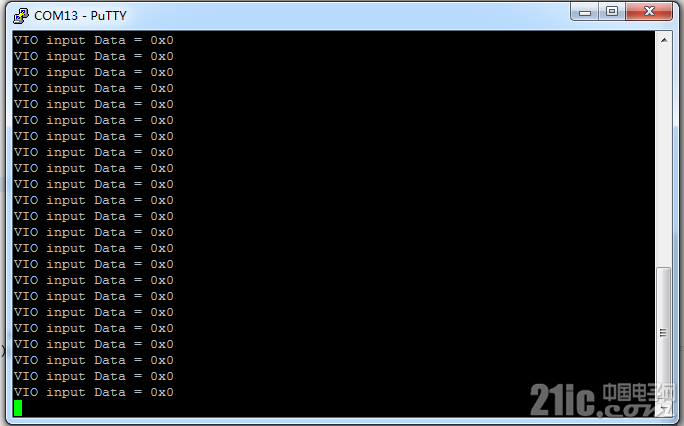

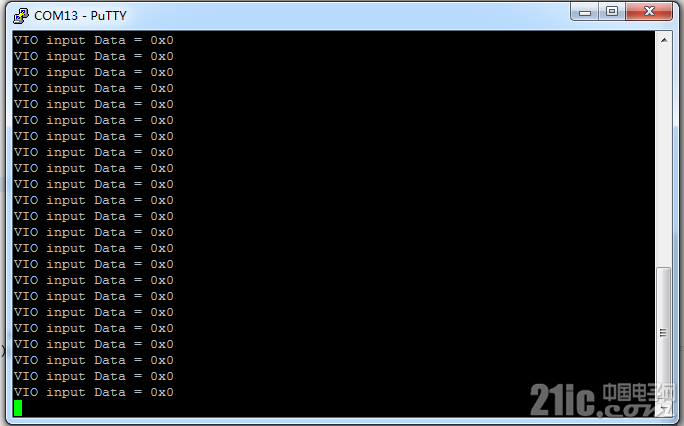

连接的PuTTY打印窗口中,每隔5秒左右会打印一行数据,即reg_rdtest寄存器的值。

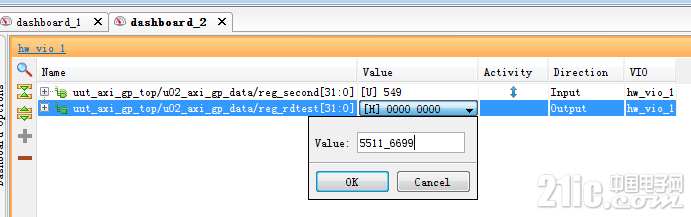

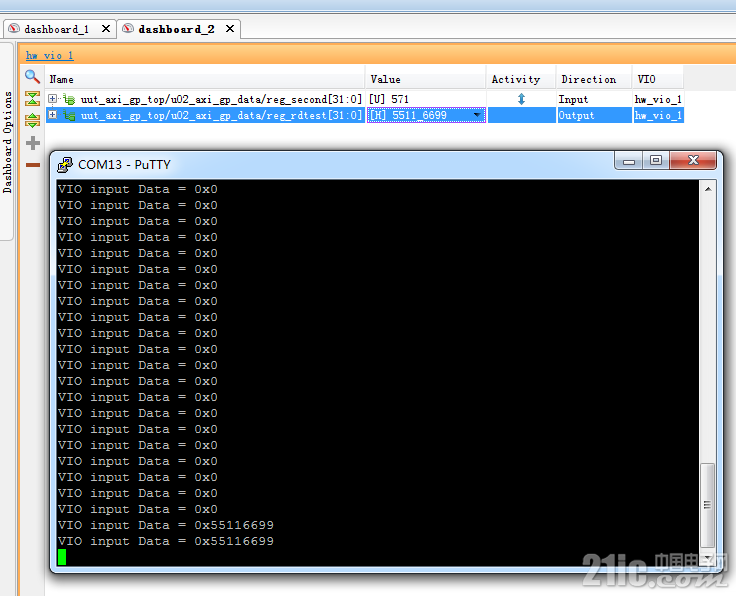

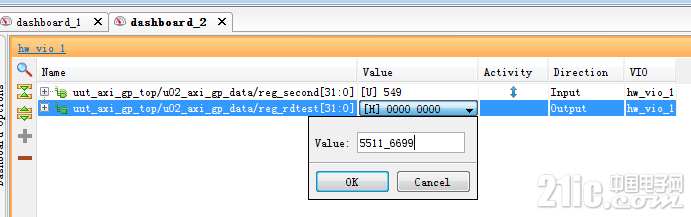

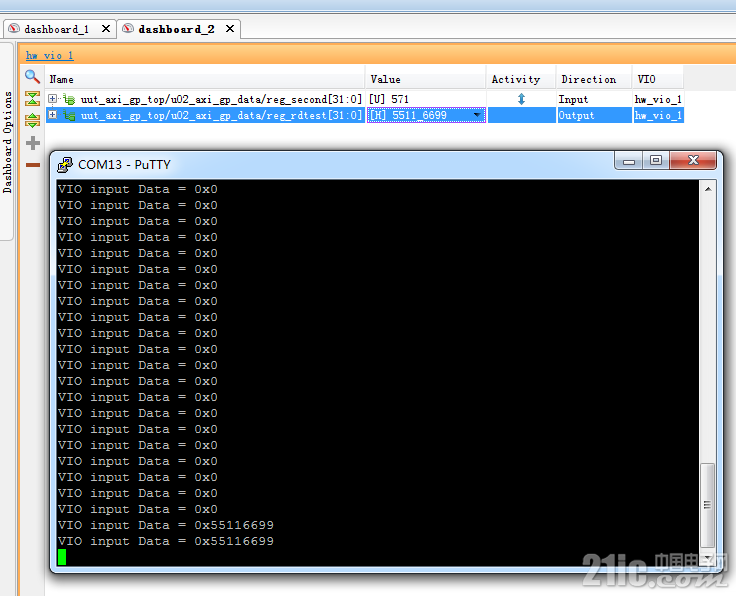

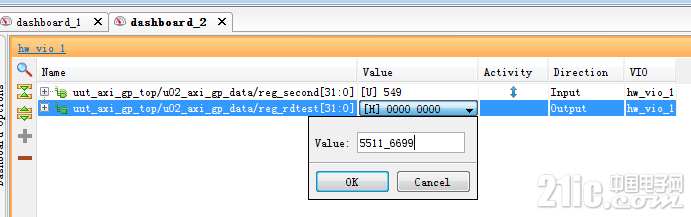

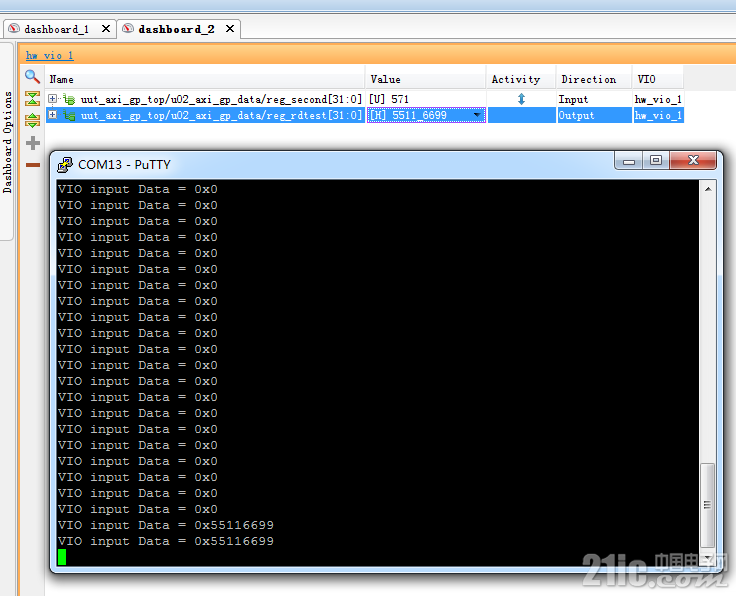

在VIO的调试窗口中,我们也注意到reg_rdtest寄存器默认显示16进制[H]0000_0000,可以将鼠标移动的该值上面点击并修改数据为[H]5511_6699。

随后我们可以看到PuTTY上打印的VIO input Data也随之更新了。

一周热门 更多>