1 概述

1 概述 基于Vivado的板级调试介绍,可以参考文档《玩转Zynq-基础篇:基于Vivado的在线板级调试概述.pdf》。这里我们以zstar_ex54工程为例,对FPGA的在线逻辑分析仪使用进行介绍和实战操练。

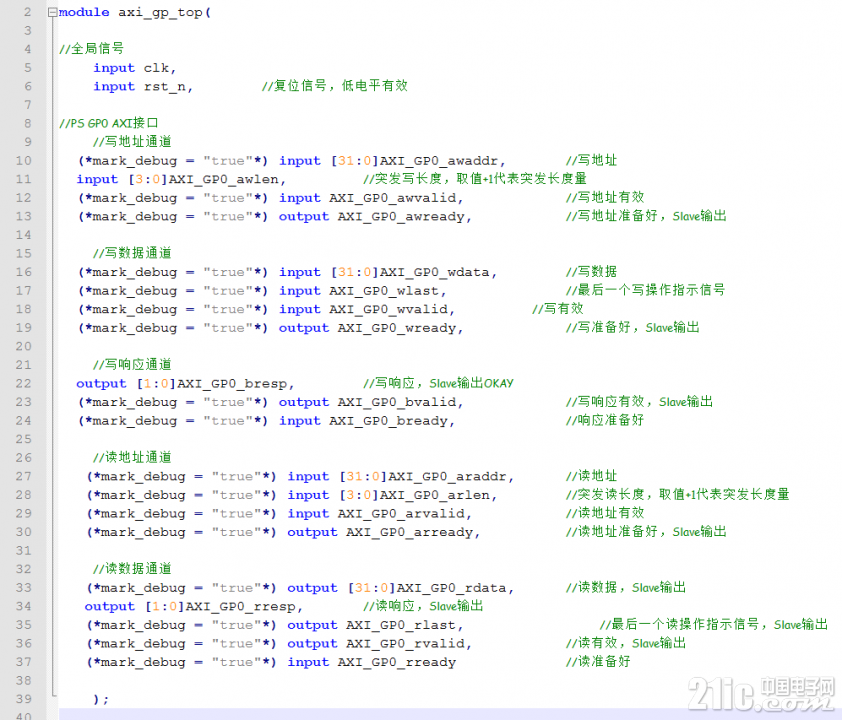

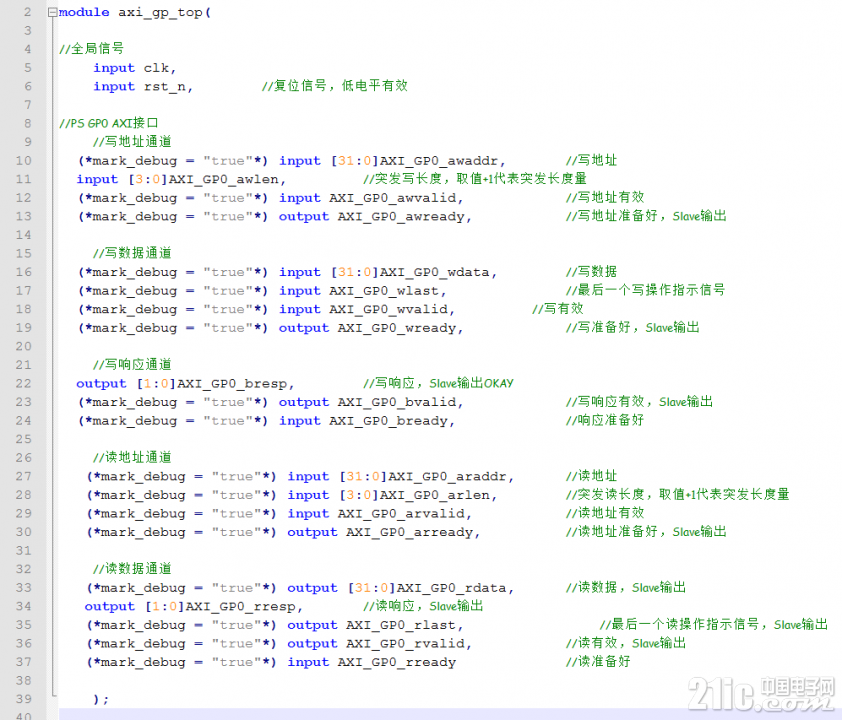

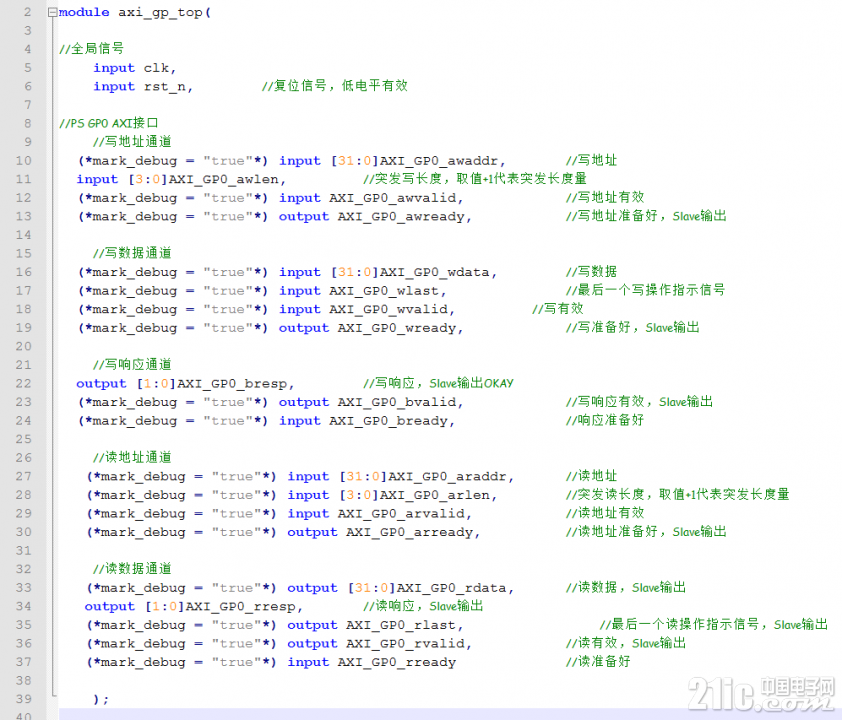

2 标记探测信号 在axi_gp_top.v模块中,可以看到AXI GP总线的很多信号前面都有(*mark_debug= "true"*)这个语句,它的作用就是将代码中需要引出进行在线逻辑分析仪观察的信号,就如同一个个探棒一样将信号标记起来。

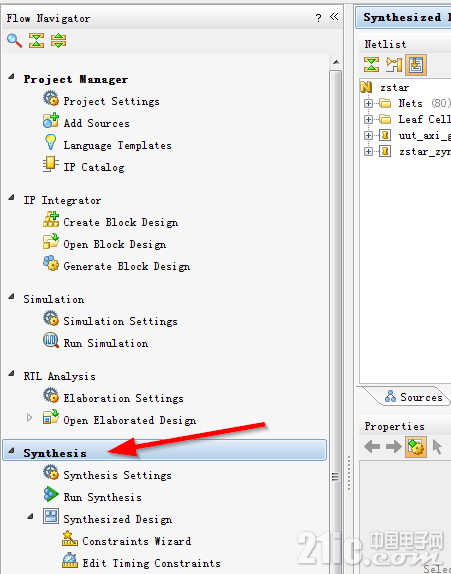

3 工程编译与Debug信号设置

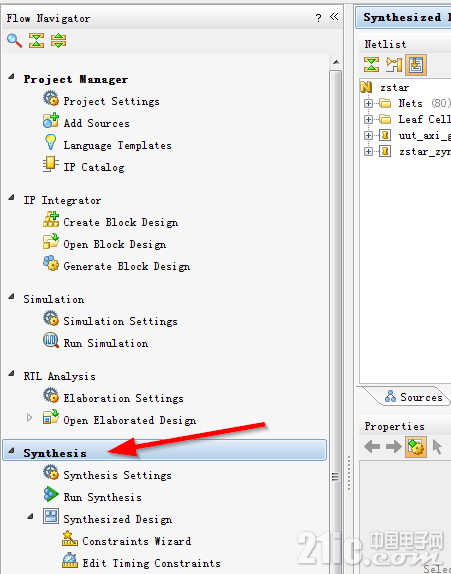

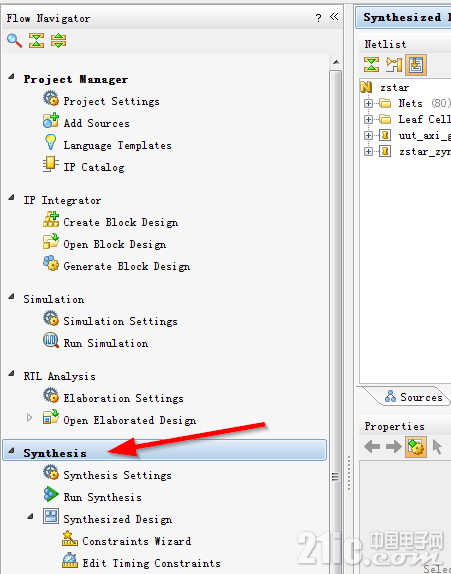

3 工程编译与Debug信号设置 工程的代码设计完成,并且标记好需要探测的信号后,点击Synthesis--> Run Synthesis对当前工程执行综合编译。

完成编译后,打开SynthesizedDesign --> Set Up Debug.

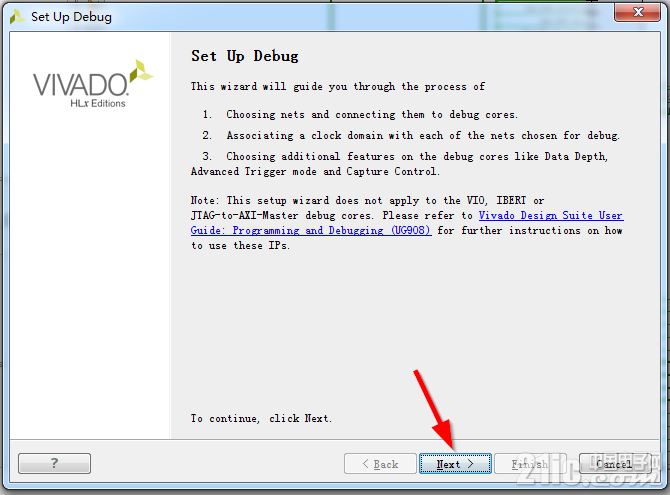

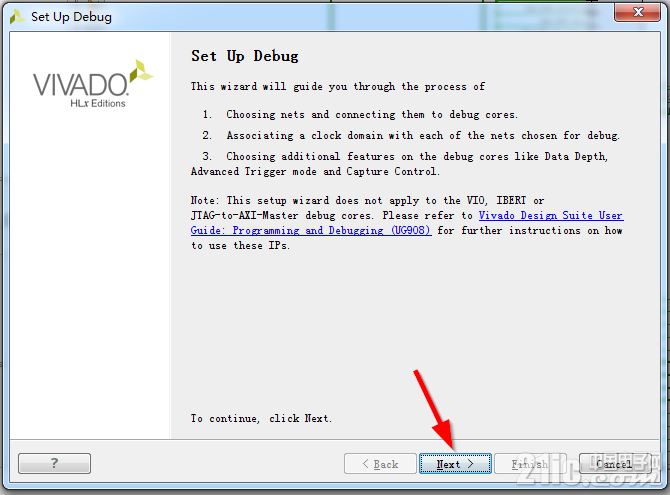

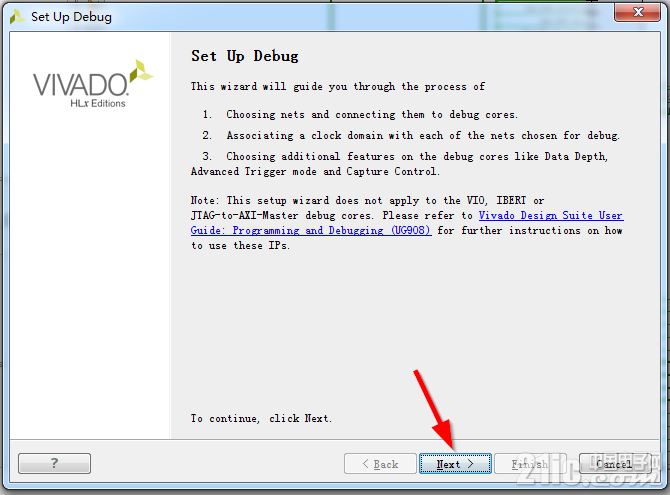

如图所示,点击Next。

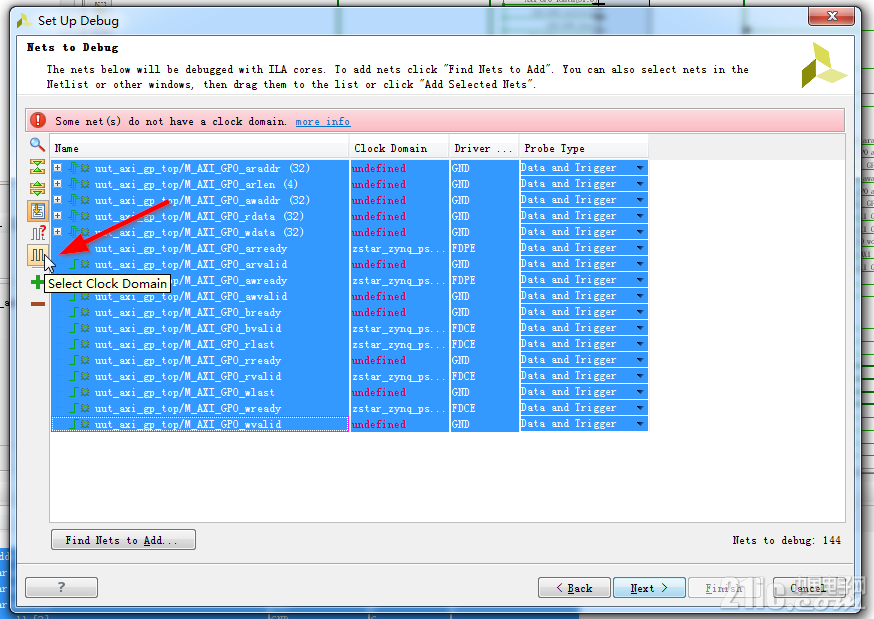

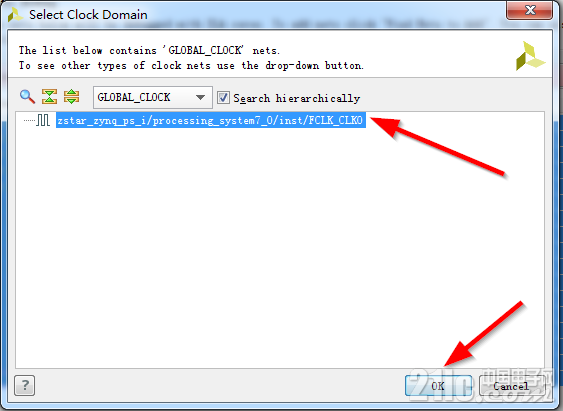

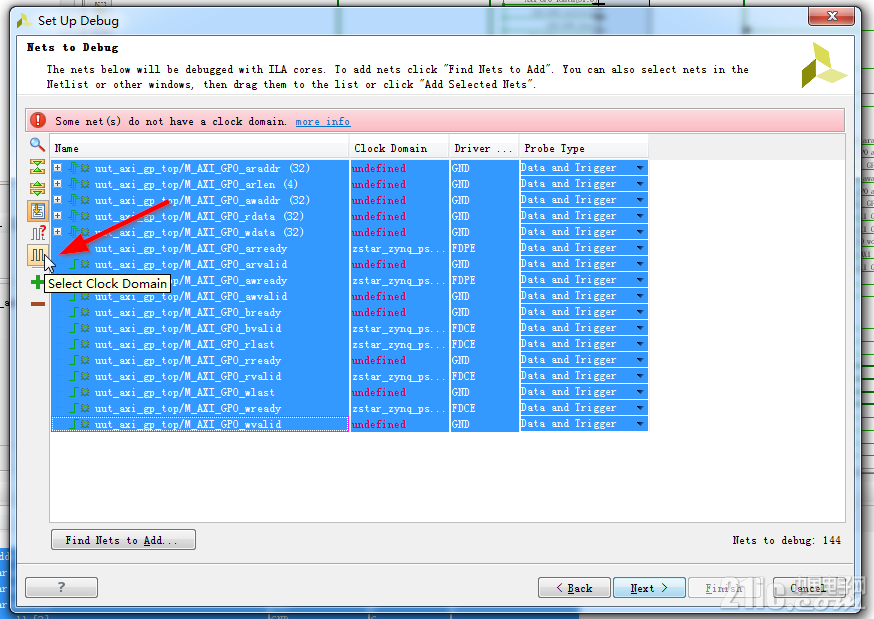

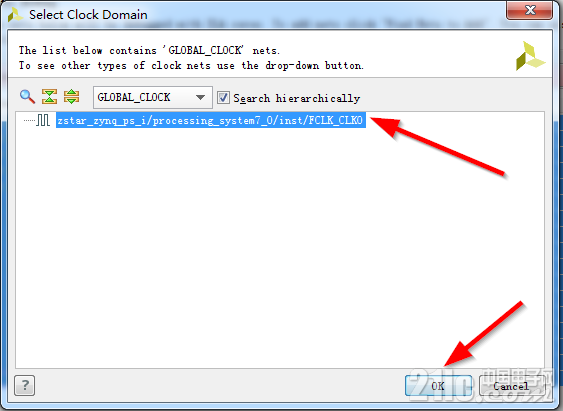

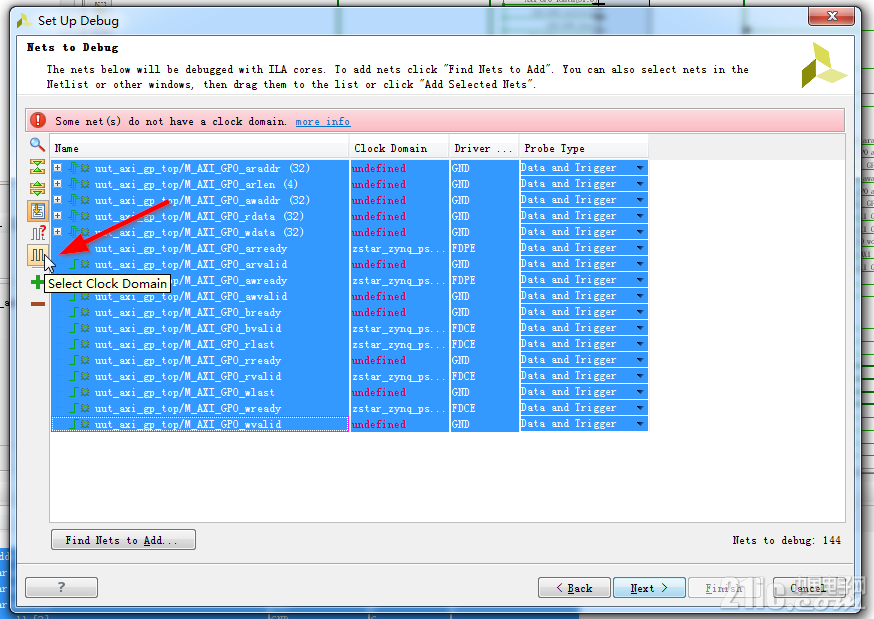

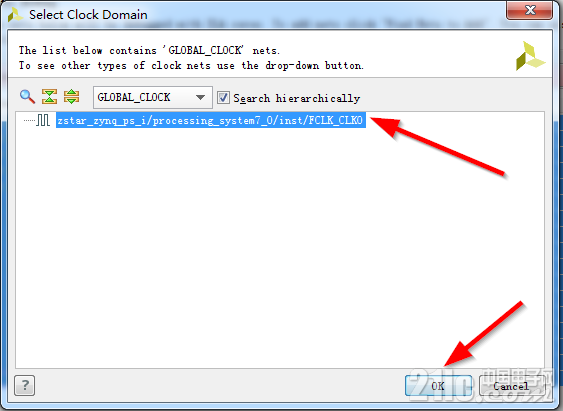

Netsto Debug界面可以添加或删除设置代码中标记了mark_debug的信号,并对其采样和触发属性做设置。● 名称(Name)列中显示了在代码中标记了“(*mark_debug = "true"*)”的所有信号。若需要在这里删除或添加信号,可以使用左侧的“+”或“-”符号进行操作。● 时钟域(Clock Domain)将作为信号采样的同步时钟,默认为信号在逻辑代码中的同步时钟。若需要修改时钟域,可以点击右侧的方波形状符号操作。● 驱动单元(Drive Cell)显示信号的驱动类型。● 探针类型(Probe Type)显示信号的采样类型,可以是数据信号(Data)、触发信号(Trigger)或同时作为数据和触发信号(Data andTrigger)。一般我们都设置为Dataand Trigger,在调试过程中,所有信号都可以随意的设置被采样信号和触发信号。 选中这些带调试信号,点击时钟图标(图示的SelectClock Domain)。

如图所示,Select Clock Domain页面中选中时钟FCLK_CLK0,点击OK。这就是信号的采样时钟。

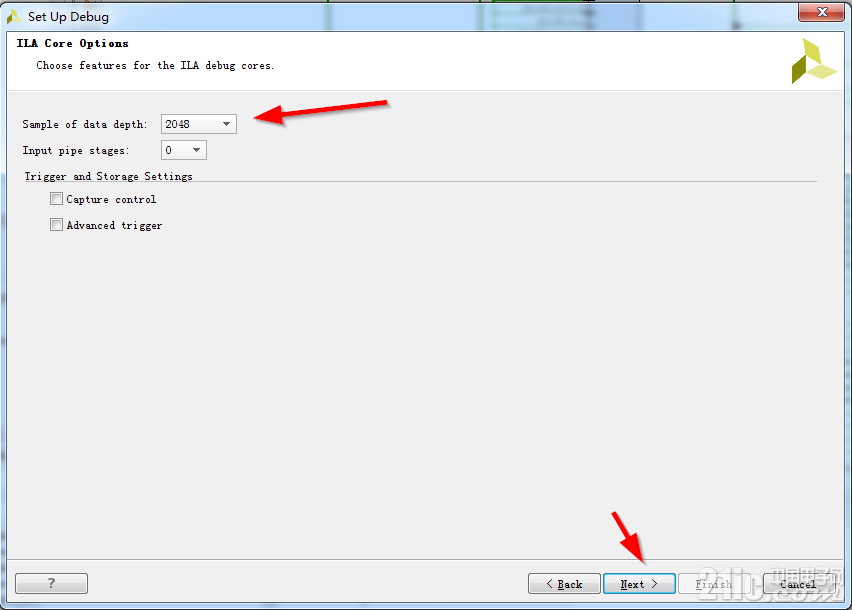

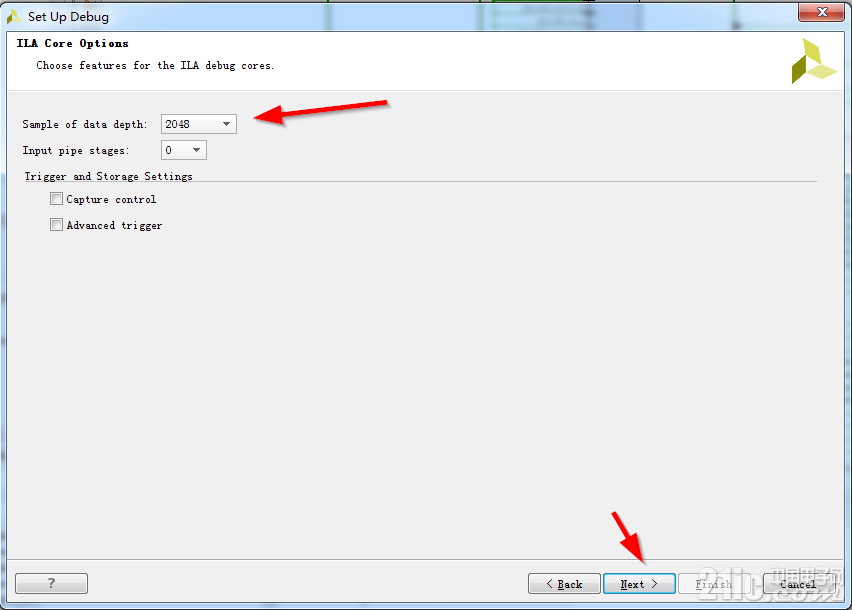

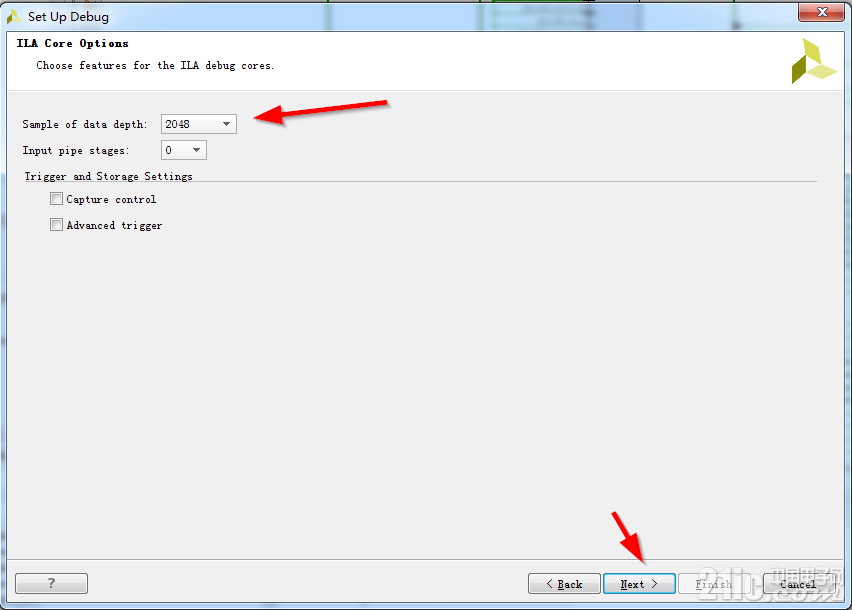

ILACore Options页面中,可以设定探测信号的采样深度、缓存寄存器等级和信号采集触发相关控制选项。完成设置后,点击Next进入下一页面。● 采样深度(Sample of data depth),用于设置信号的连续采样点数量。当然,这个值越大,采样的数据越多,越利于调试探测,但是这需要更多的FPGA片内RAM的资源消耗,所以这个值的大小取决于实际系统可用的RAM。这里设定32768个点,至少保证能够采样到一帧9600bps的UART接收数据。● 探测信号经过的寄存器等级(Input pipestates)设定,此选项主要用于确保设计中的关键信号不会因为ILA探测信号的加入而受到影响。对于设计本身时序余量充足的情况,这个值可以设置为0。 触发和存储设置(Triggerand Storage Settings)中可以使能采集控制(Capturecontrol)和高级触发(Advancedtrigger)。使能采集控制,ILA支持的基本采集控制模式可用。使能高级触发,ILA支持的一些高级触发模式可用。 完成设定后,点击Next。

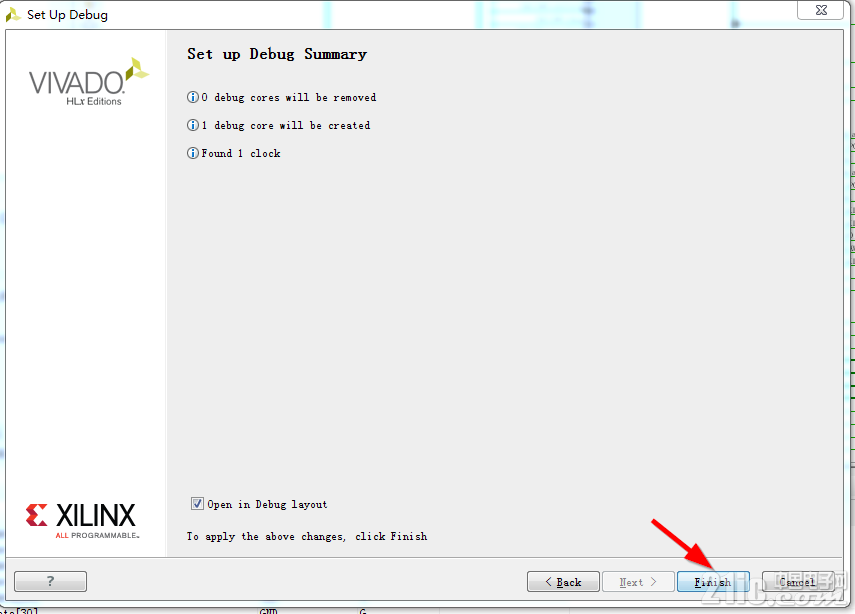

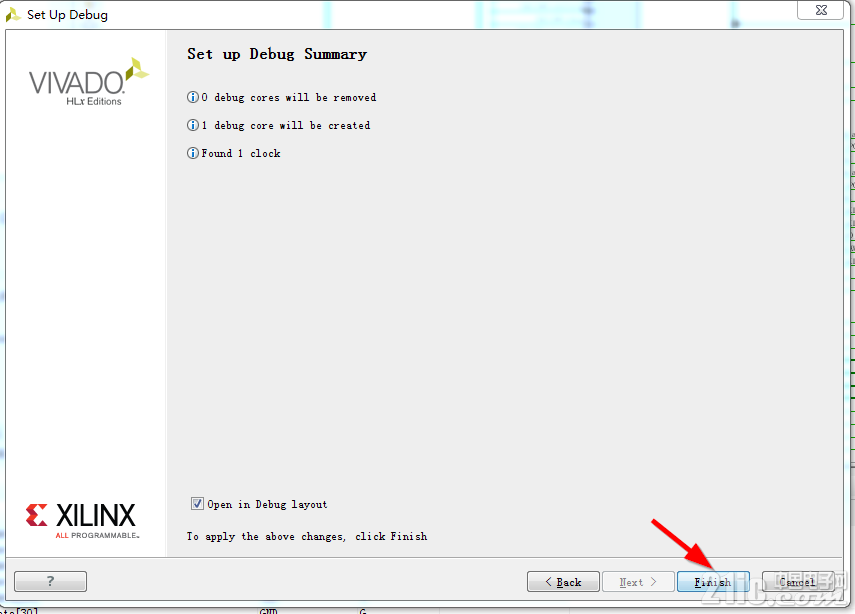

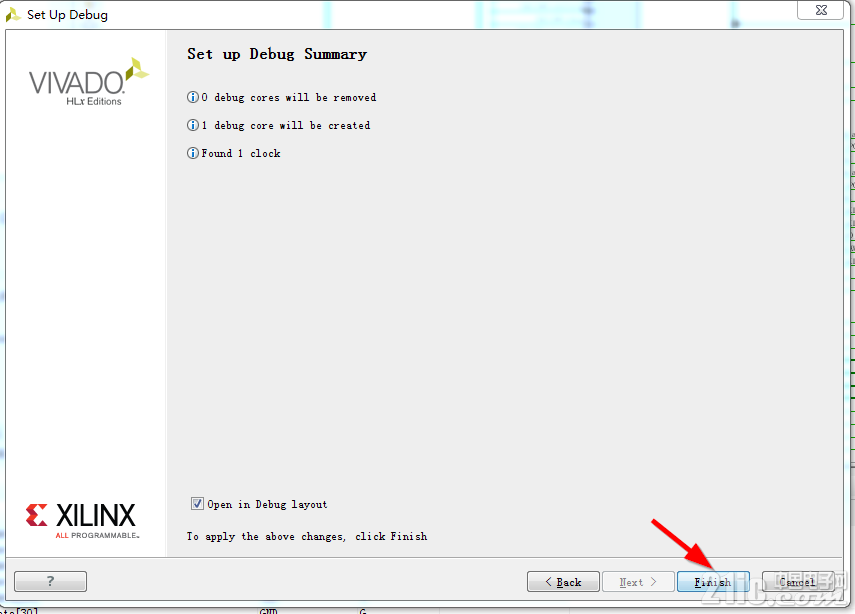

最后是Set up Debug Summary页面,点击Finish完成设定。

点击Program and Debug à GenerateBitstream重新编译工程,产生下载配置的bit文件。

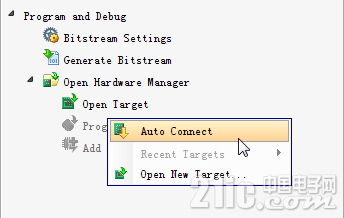

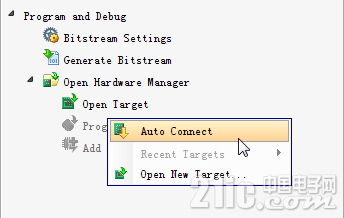

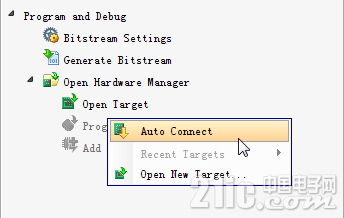

3 板级调试观察 在已经下载bit文件,并且elf文件已经在Zstar板子上运行起来以后。回到Vivado中,如图所示,展开Program and Debug --> Open Hardware Manager,点击Open Target,弹出菜单中选择AutoConnect。

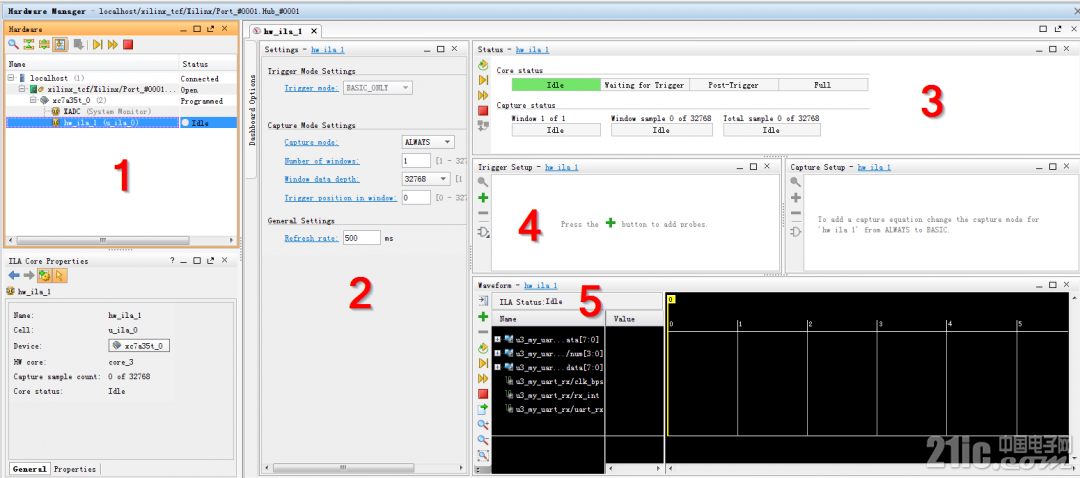

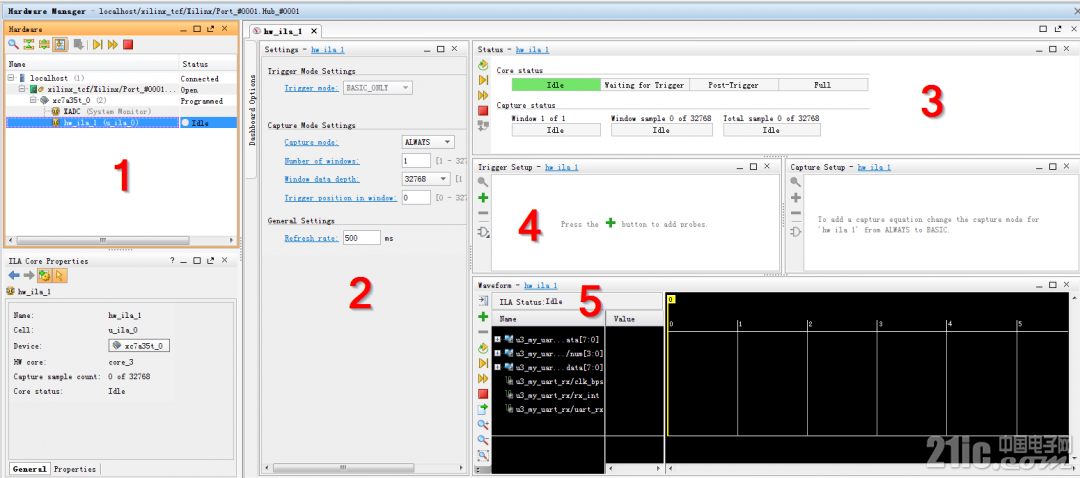

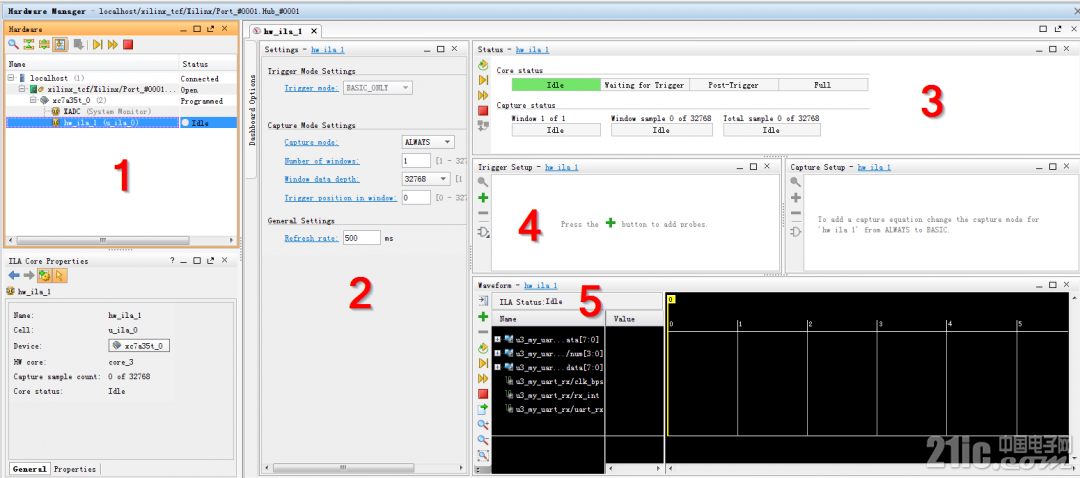

随后弹出如图所示的Hardware Manager界面。● 1:Hardware窗口,这里将会出现FPGA中所有可以通过JTAG进行调试的选项,例如XADC以及本实例专门增加的在线逻辑分析仪ILA(hw_ila_1)。双击hw_ila_1,将弹出相应的调试界面。● 2:Setting窗口,这里可以对信号的采样和触发控制进行设置。● 3:Status窗口,这里显示当前数据采样或触发的状态。● 4:Trigger Setup窗口,这里可以添加触发信号并编辑触发条件。● 5:Waveform窗口,这里显示信号触发后的采样波形。

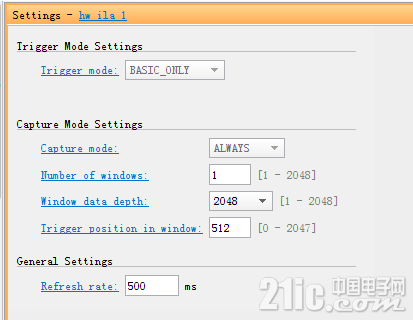

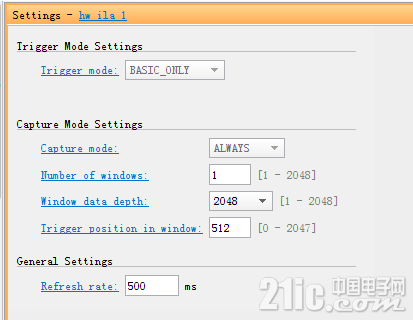

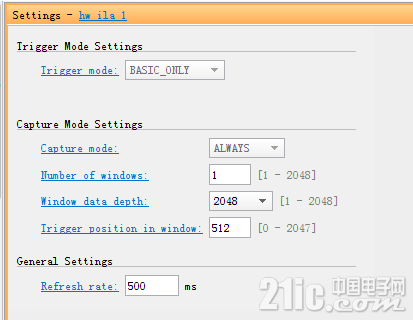

图 Hardware Manager界面 本实例的Setting窗口设置如图所示。● 触发模式(Trigger mode)反应的是Set Up Debug里的设定,我们是BASIC_ONLY设置。● 采样模式(Capture mode)的选项有BASIC和ALWAYS,我们设定ALWAYS。● 窗口数量(Number of windows)的值可以设定同样的触发条件下,连续多次的触发显示在不同的窗口中。当然了,窗口数量的增加,势必会使得单个窗口的采样深度变小。换句话说,所有窗口采样深度的总和不能大于总的采样深度。● 单个窗口的数据采样深度(Windowdata depth),最大值等于我们的SetUp Debug里的设定。● 触发信号在窗口中的位置(Triggerposition in window),这里的值表示当信号触发后,触发信号在显示波形中的位置。● 刷新率(Refresh rate),刷新率主要是针对连续触发的。

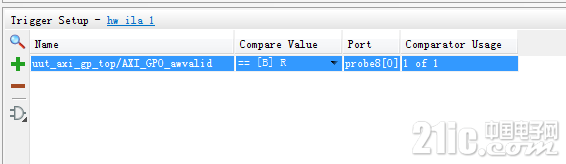

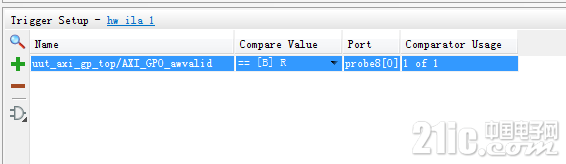

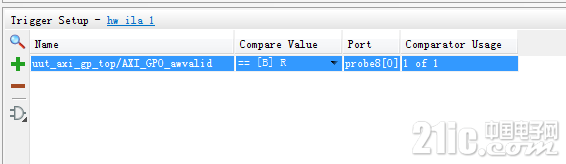

图 Settings窗口 TriggerSetup窗口用于添加触发信号并设定触发条件。如图所示,在界面左侧点击“+”号后,所有可用的触发信号出现在弹出的列表中。选择uut_axi_gp_top/AXI_GP0_awvalid信号作为触发条件,CompareValue中选择== [B] R,表示触发条件是触发信号为上升沿(Rise)。

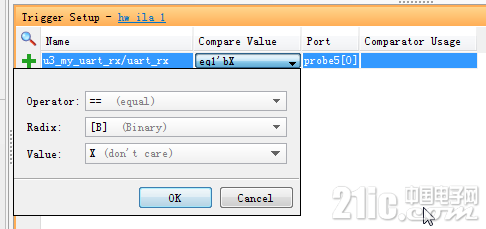

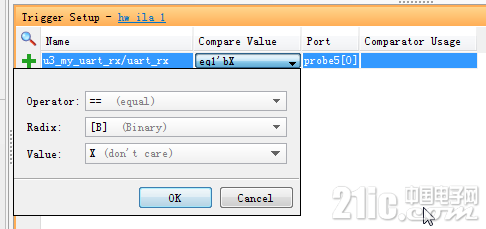

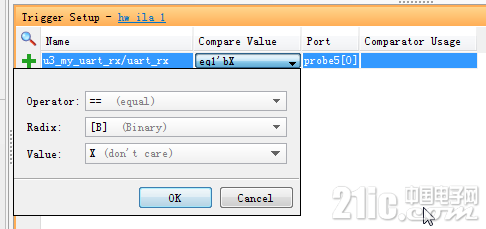

图 正在添加信号的Trigger Setup窗口 如图所示,点击Compare Value列的下拉三角符号,会弹出触发条件设定的对话框。● 运算符(Operator)中可以选择符号“==”或者“!=”。● 进制(Radix)中可以设定后面值(Value)的进制,可选项有二进制([B] Binary)、八进制([O] Octal)、十六进制([H]Hexadecimal)、有符号十进制([U]Unsigned Decimal)和无符号十进制([S]Signed Decimal)。● 值(Value),即运算符后面的取值。可选项有0(逻辑0)、1(逻辑1)、X(任何值)、R(上升沿)、F(下降沿)、B(上升或下降沿)、N(没有变化)。

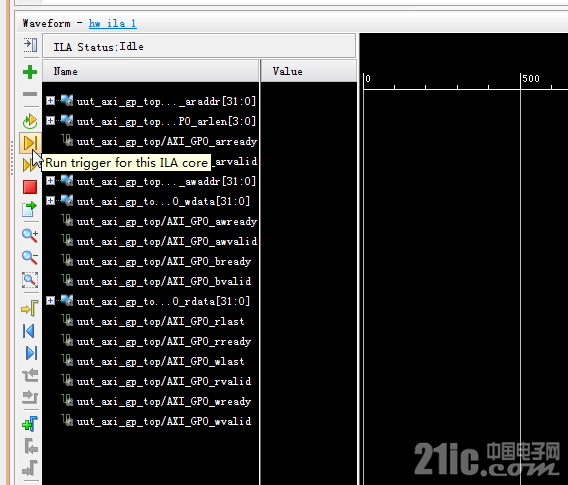

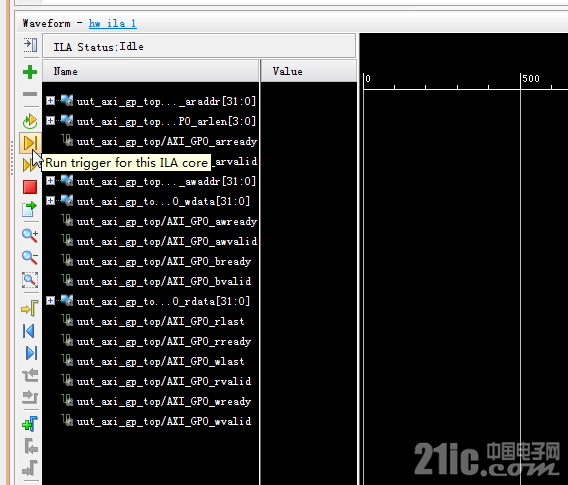

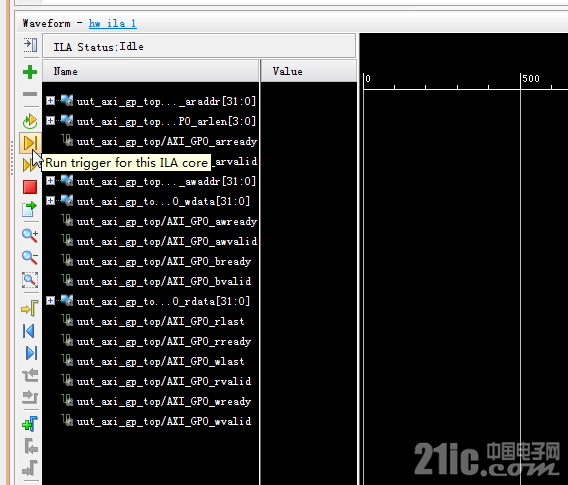

图 触发条件设置 如图所示,Waveform窗口显示弹出信号在触发条件满足后的波形。窗口左侧的小图标可以控制探测信号的添加、删减,波形采样的单次运行、连续运行、停止,波形的放大、缩小以及光标线的移动等。点击图示的Run trigger for this ILA core按钮则启动一次触发。

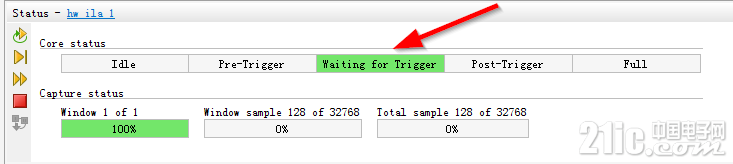

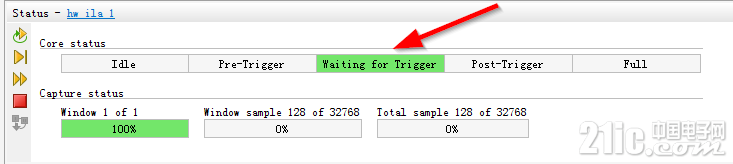

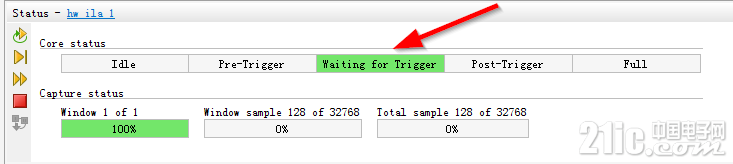

图 Waveform窗口 如图所示,此时Status一直处于Waiting for Trigger状态,等待触发条件的发生。

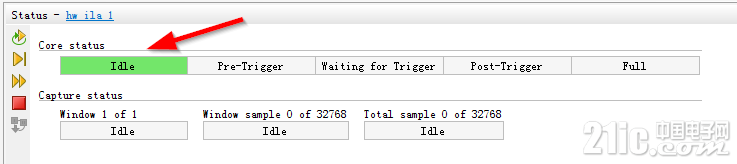

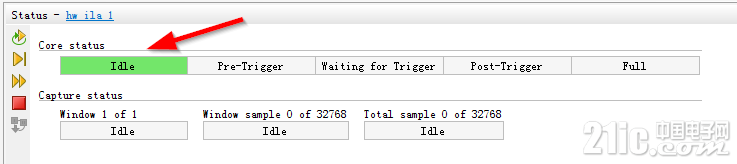

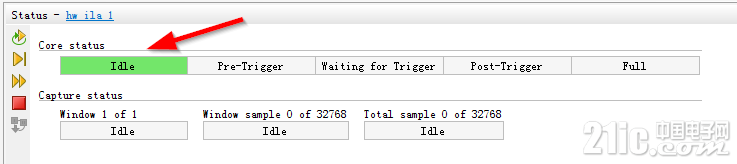

图 等待触发状态 触发条件发生时,如图所示,Status会依次经过Post-Trigger和Full状态并回到Idle状态。

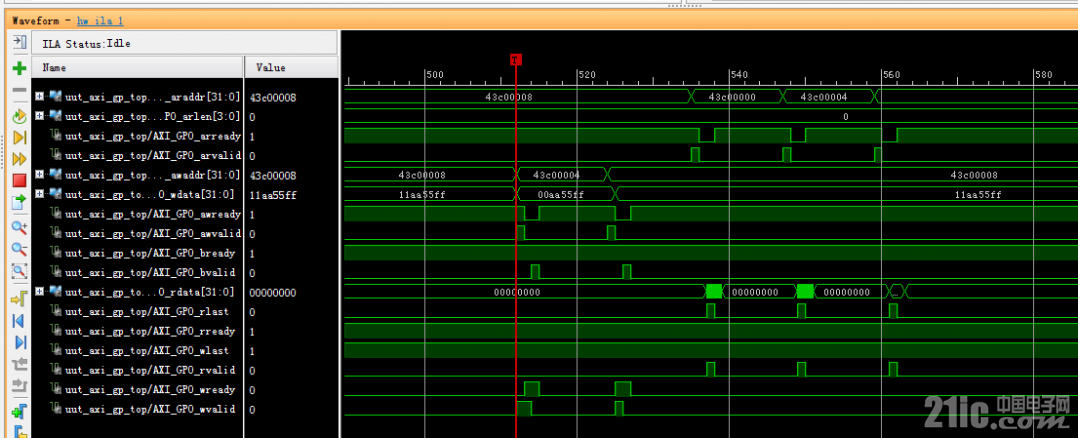

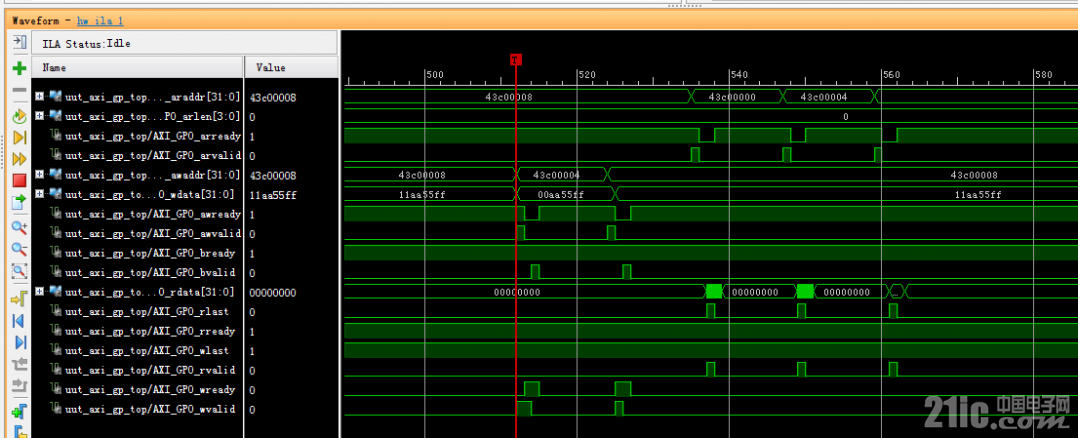

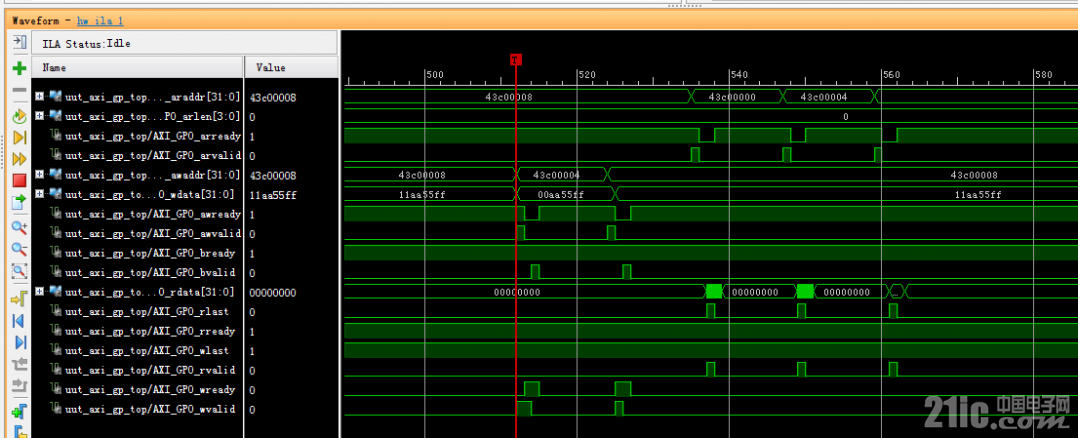

图 触发完成返回Idle状态 如图所示,Waveform窗口中出现了一连串的AXI GP总线读写的波形。大家可以更具波形对照AXI协议进行分析。

图 触发波形

一周热门 更多>