本帖最后由 zyingjie 于 2016-8-23 14:29 编辑

立帖为证

/**************************************************************************/

/****************************2016-08-23 V02版本完成*********************************/

/**************************************************************************/

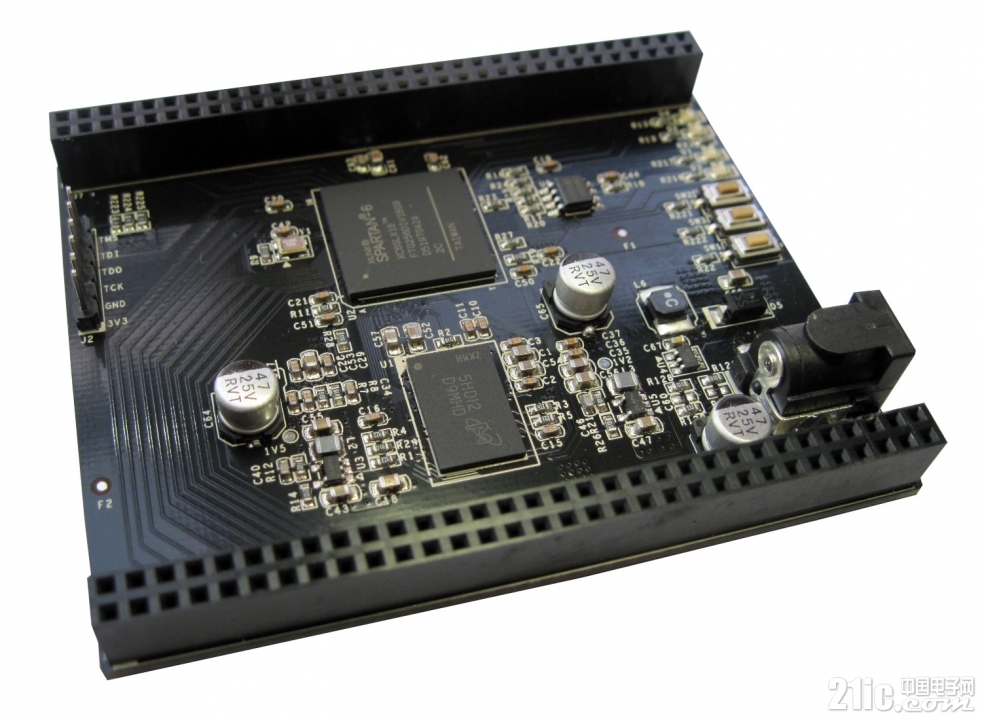

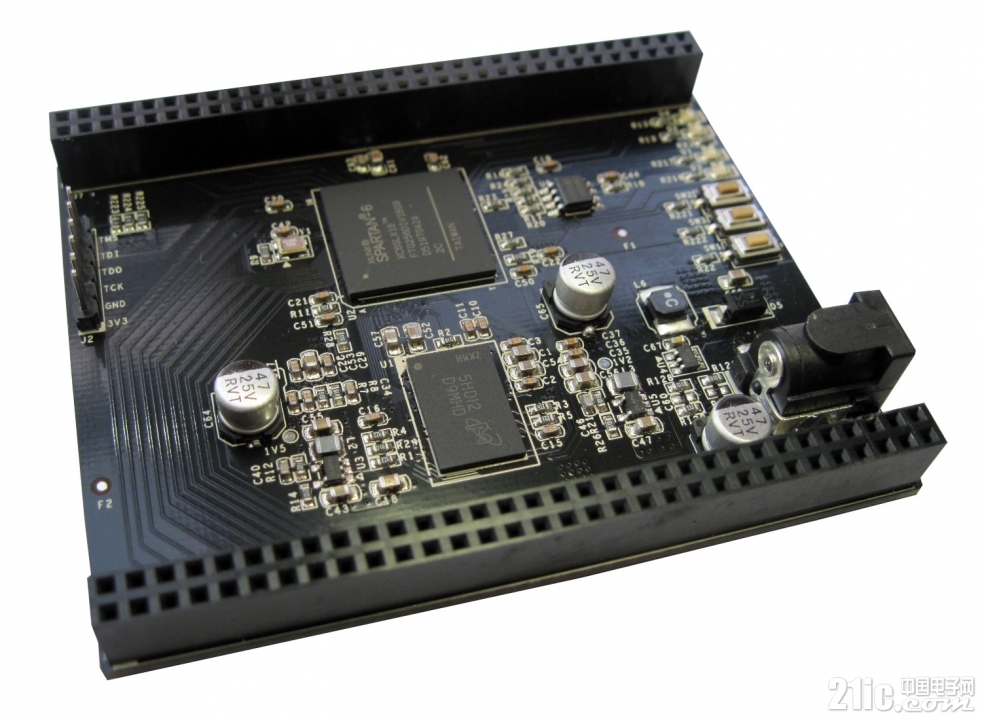

黑 {MOD}底板果然好看多了。

/**************************************************************************/

/****************************2016-07-26 完成*********************************/

/**************************************************************************/

2Gbit全地址空间测试完成,用的是Xilinx提供的MCB IP硬核,下面是原理图,测试程序和说明书,

请翻滚帖子至最后, 欢迎下载。

/**************************************************************************/

/****************************2016-07-23 更新*********************************/

/**************************************************************************/

经测试,第一版的DDR3可以正常稳定运行在400MHz,全地址空间读写数据无任何问题。

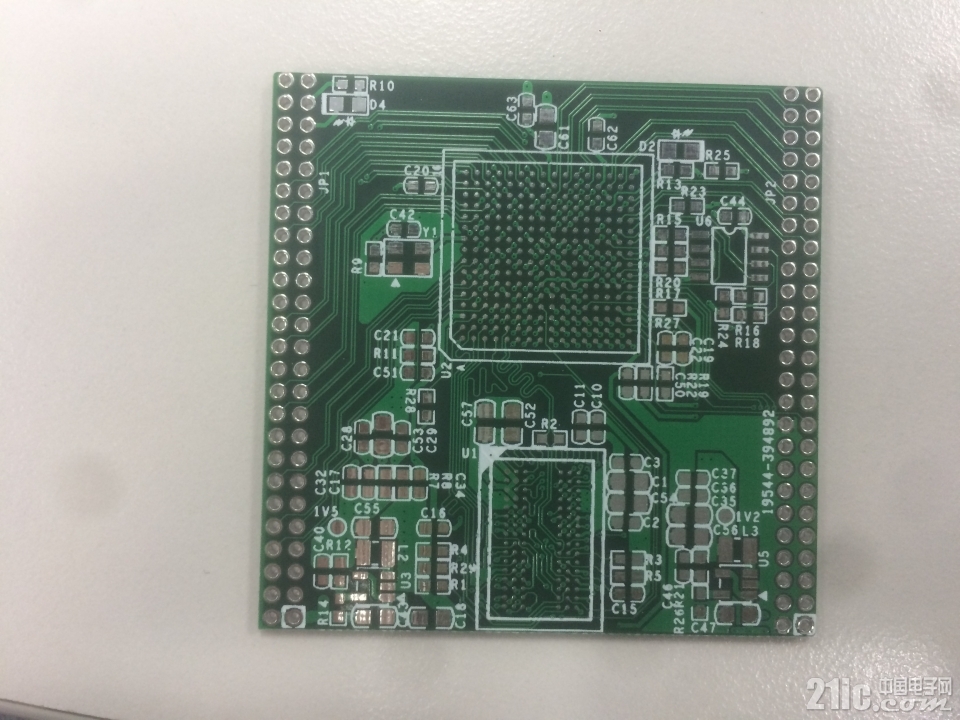

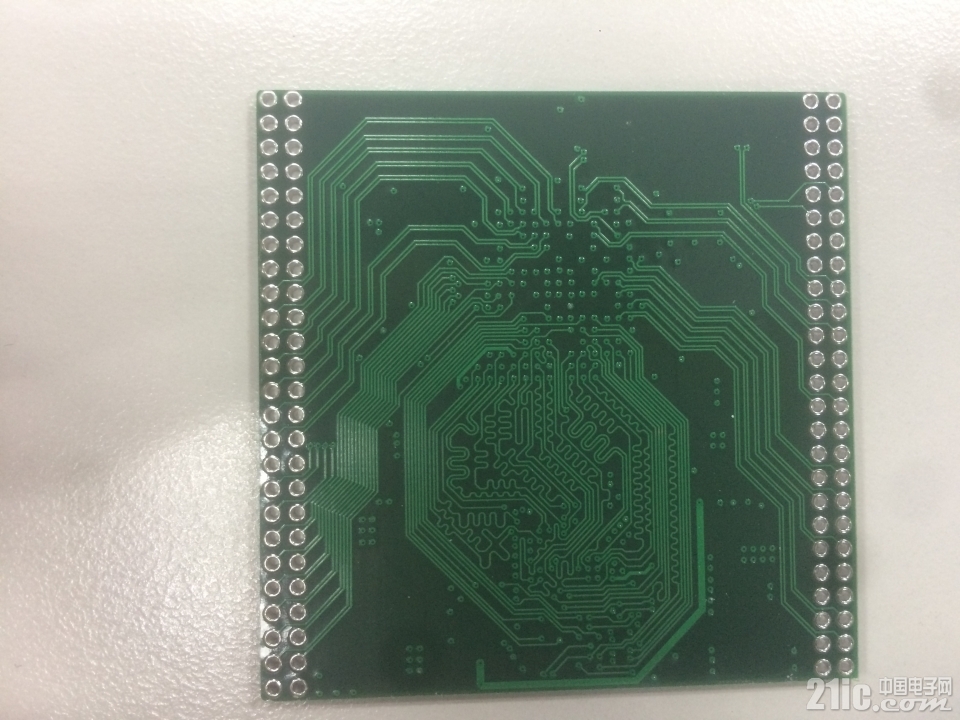

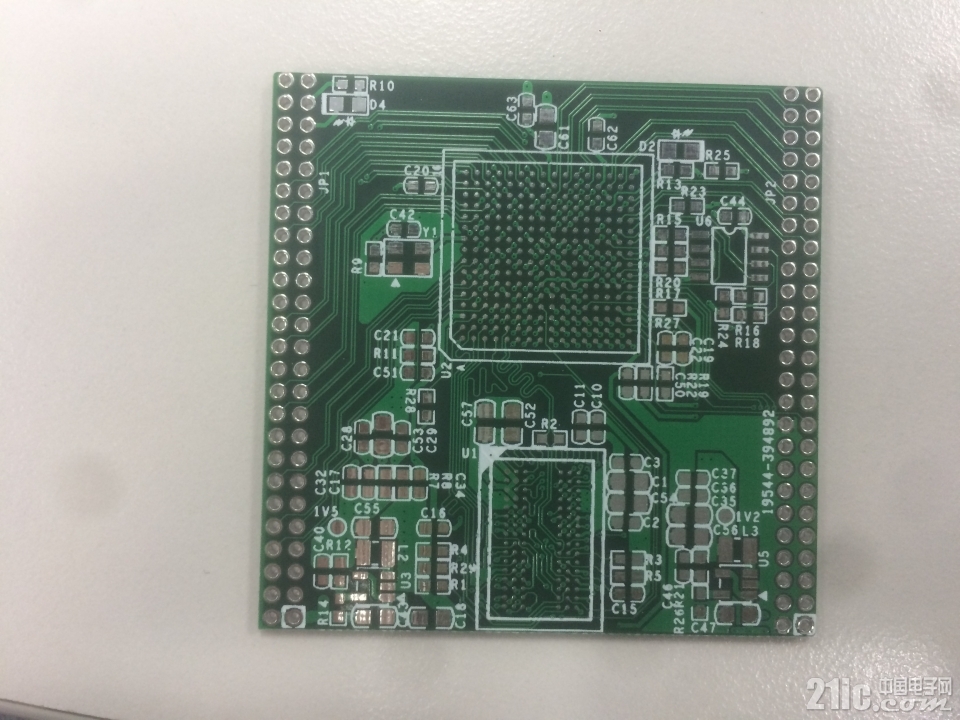

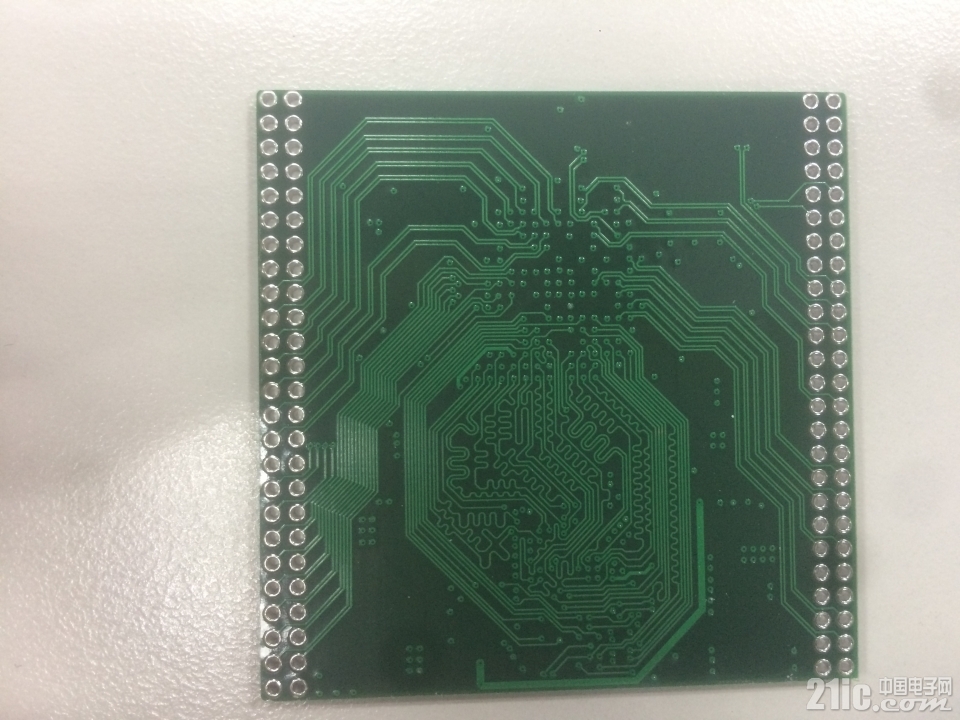

现在开始准备第二版,打算生成100个pcb,并且会将阻焊颜 {MOD}由绿 {MOD}改为黑 {MOD}。

具体设计细节和第一版的区别如下:

(1) IO引脚数量由原来的80个增加到86个IO;

(2) 所有引出的差分线尽量保持等长;

(3) 电容部分进行了改进,每个DC/DC输出都增加了铝电解电容,增加可靠性,铝电解电容都放在背面。

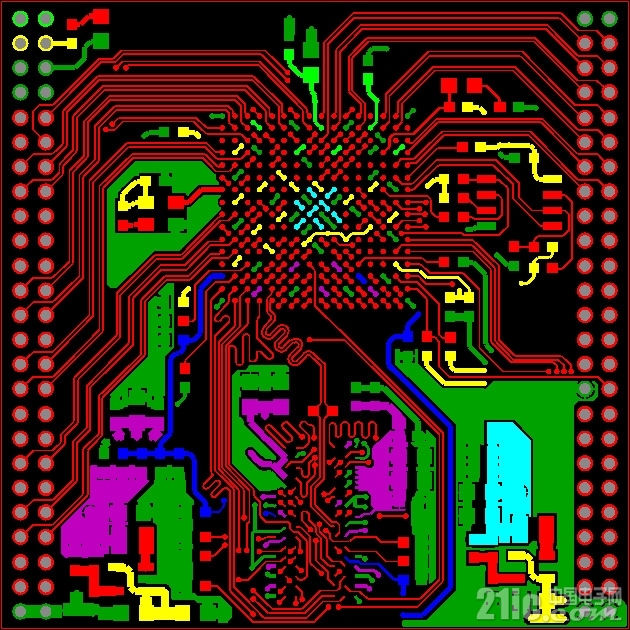

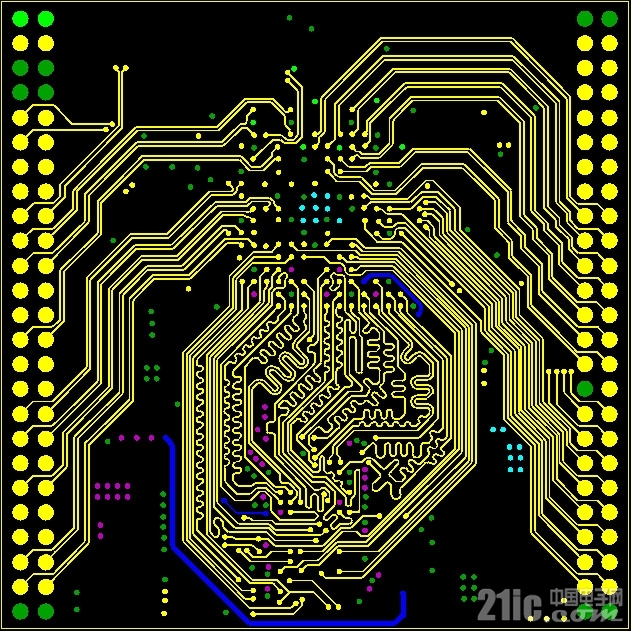

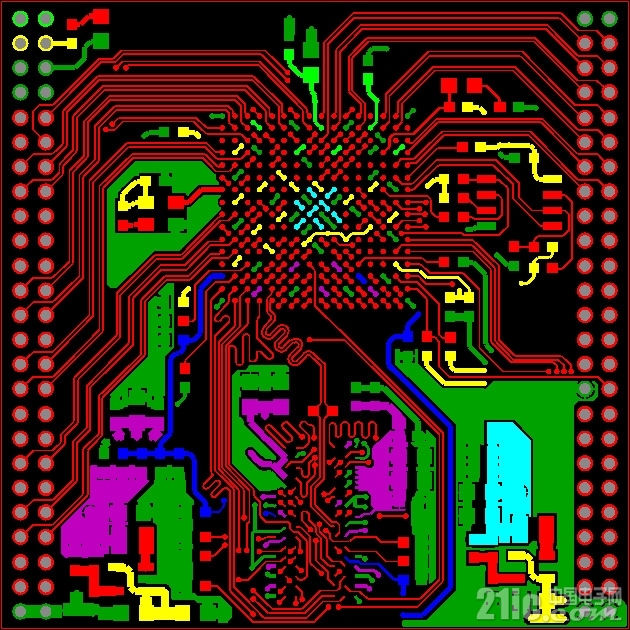

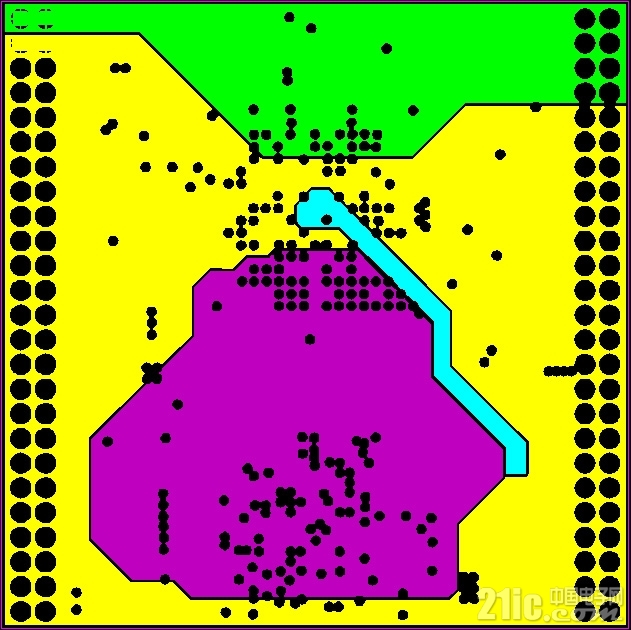

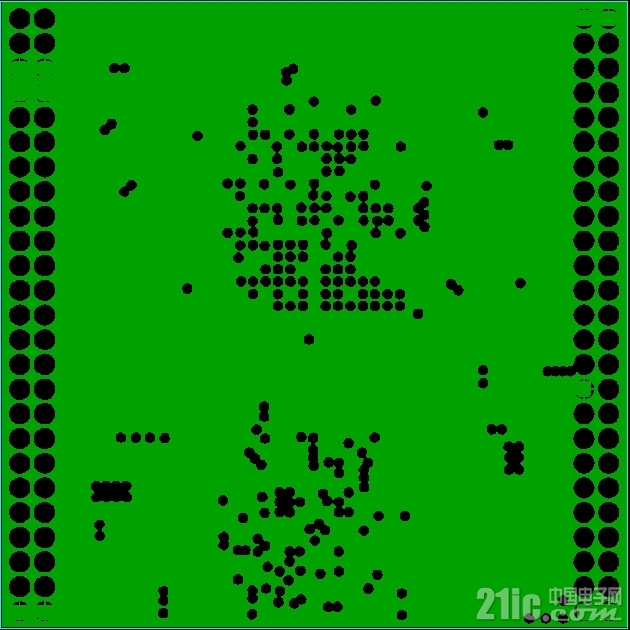

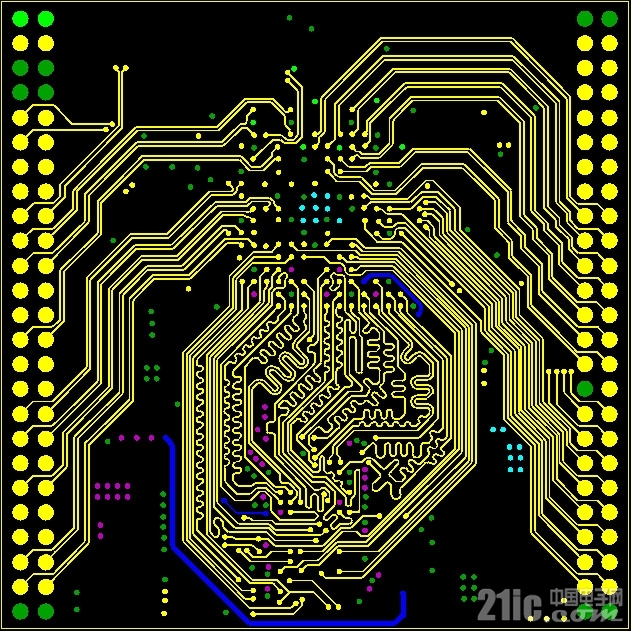

下面是第二版的图片:

/**************************************************************************/

/****************************2016-07-19 更新*********************************/

/**************************************************************************/

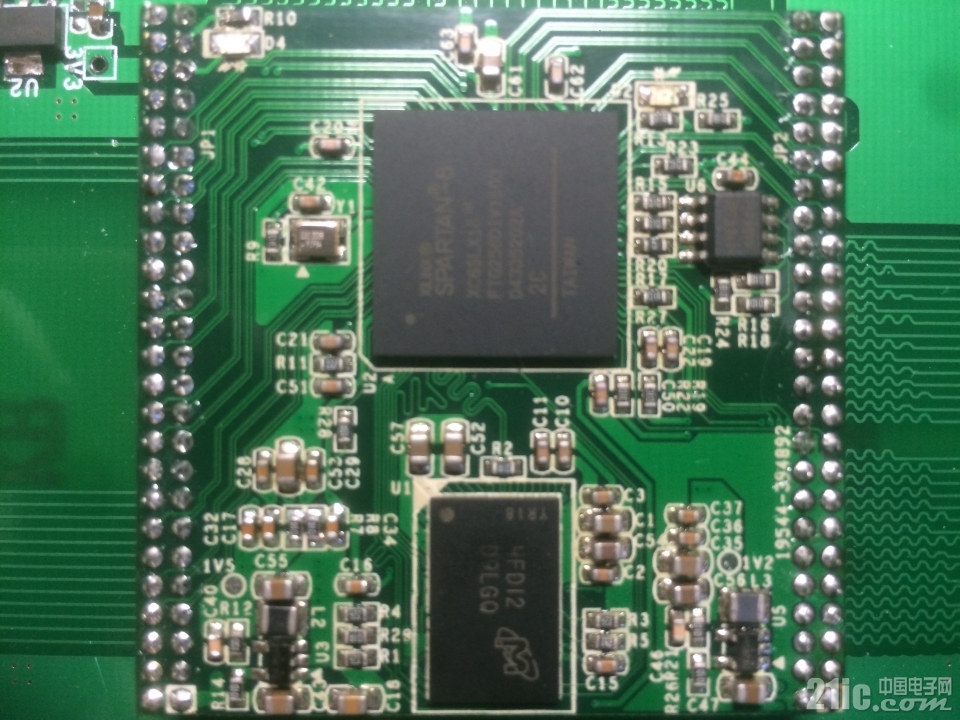

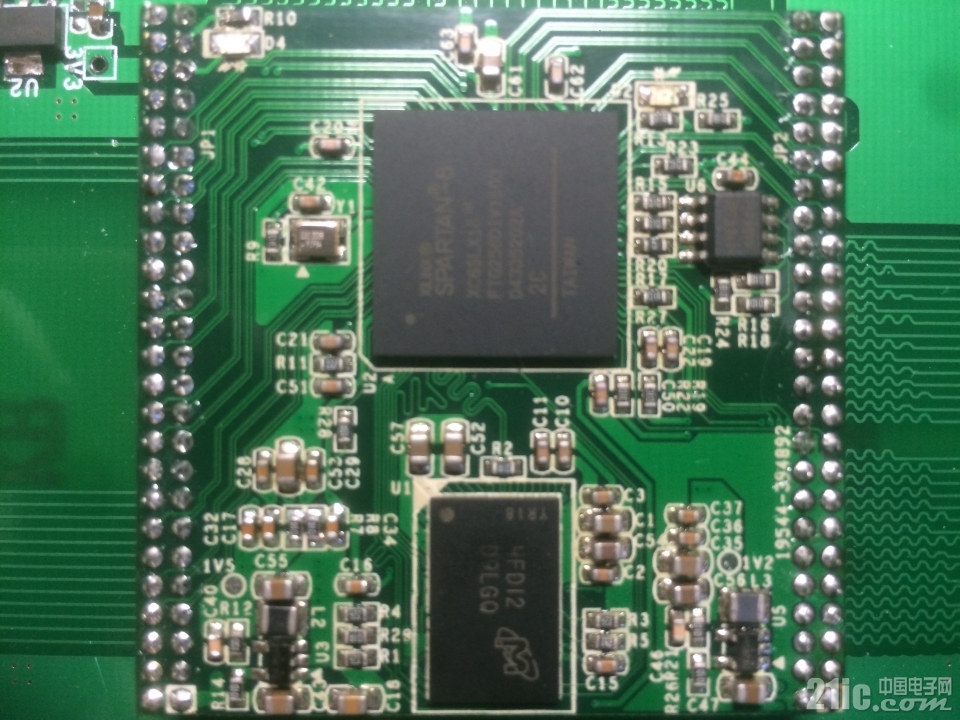

搞了一个上午,终于搞定第一个板子,FPGA的1.2V VDDCore电压,1.5V的DDR3供电电压,

VREF的0.75V电压都OK。往FPGA内部下载点灯程序OK,往SPI FLASH固化程序也OK。

下一步,DDR3 的MCB实现。。。。。。

/**************************************************************************/

/****************************2016-07-18 更新*********************************/

/**************************************************************************/

PCB打样回来了,5mil/5mil的线宽线距,10mil的过孔,花了我好多大洋!!!赶紧贴板子去了!!

贴完再上照。

/**************************************************************************/

/****************************2016-07-10 更新*********************************/

/**************************************************************************/

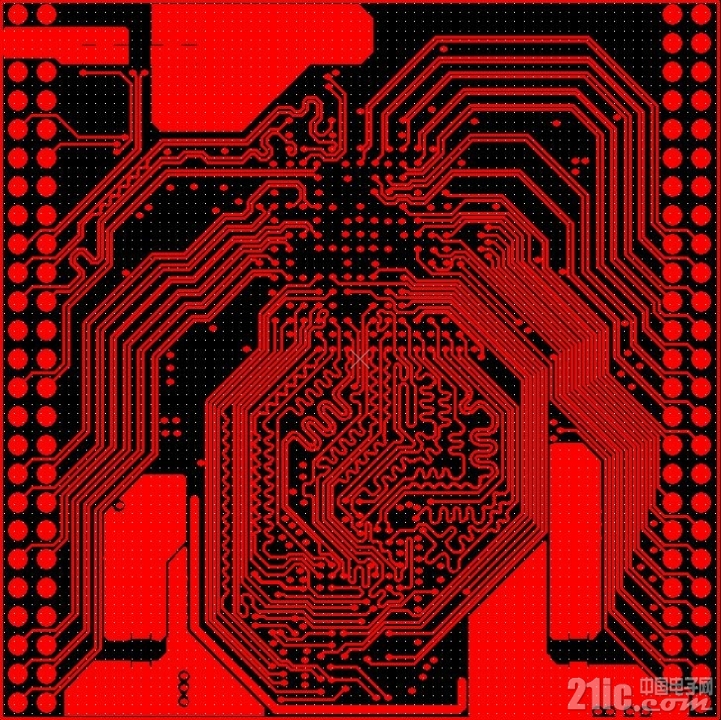

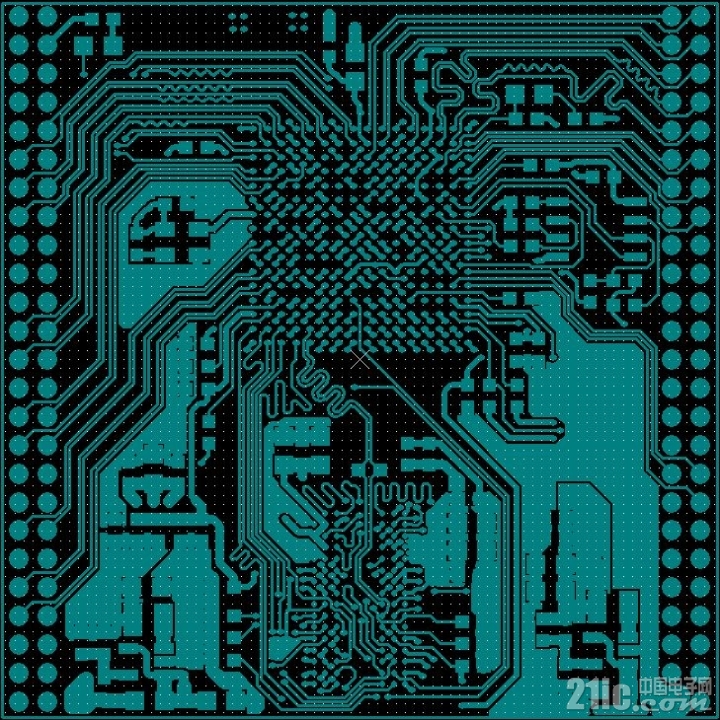

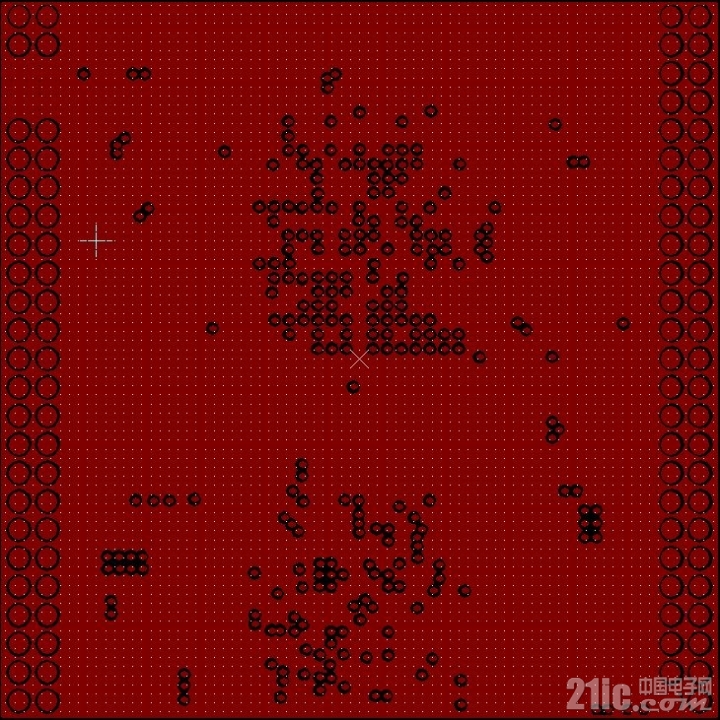

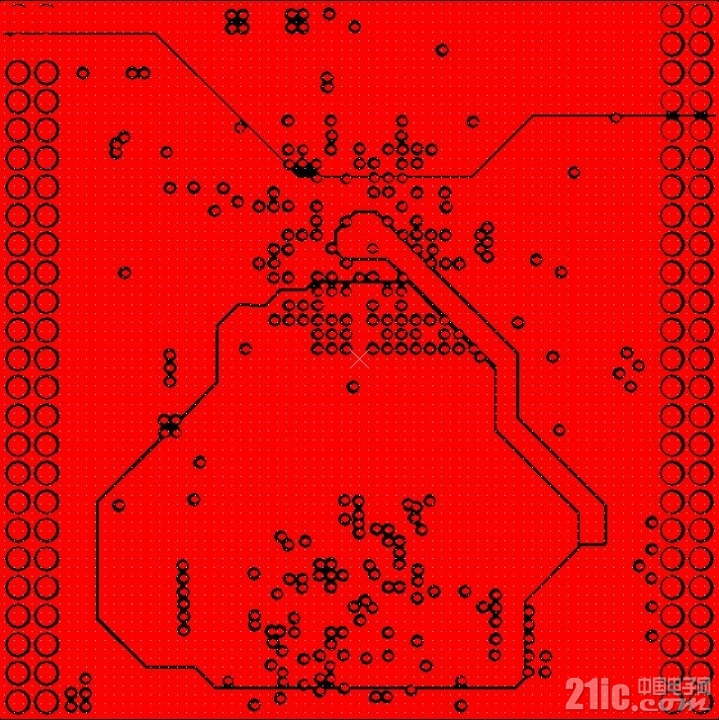

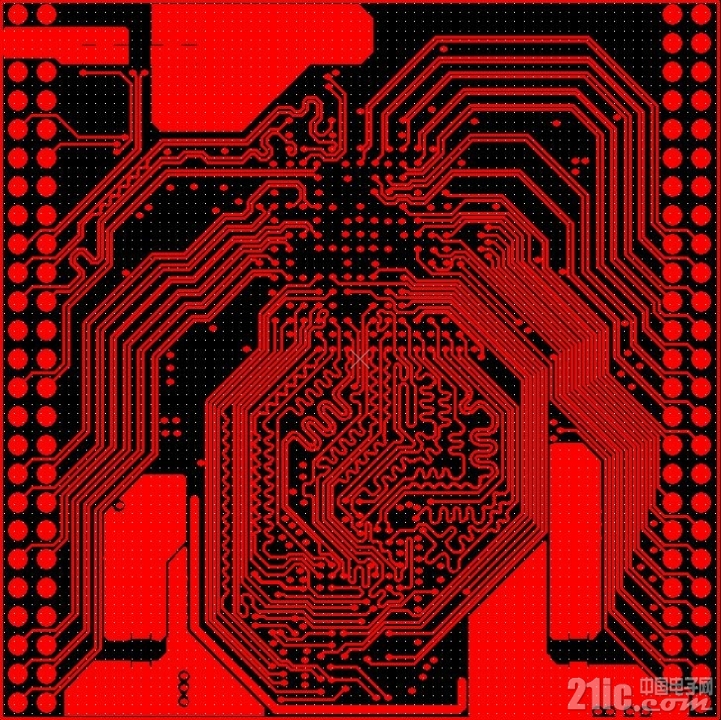

经过不知道多少个工作日空余时间和周末业余时间,终于大致设计板子浮出水面,等待后续检查。

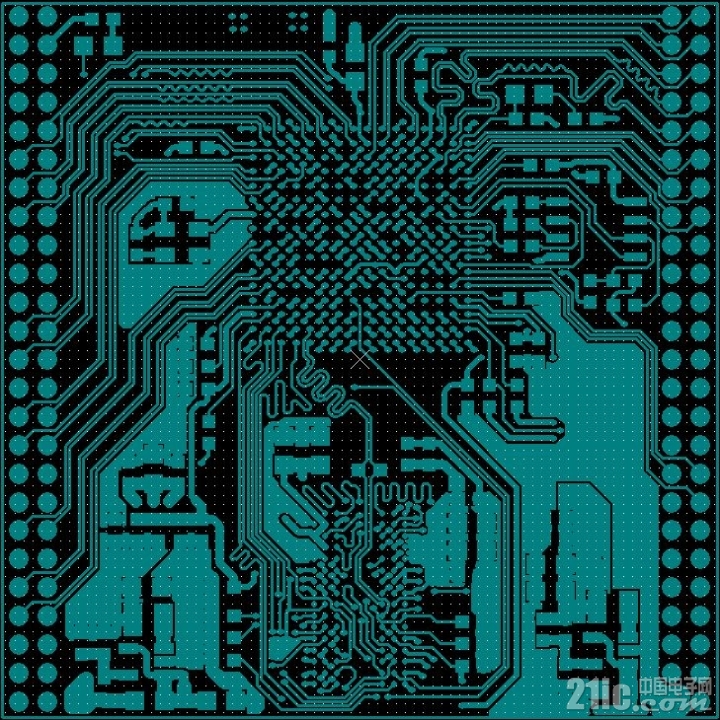

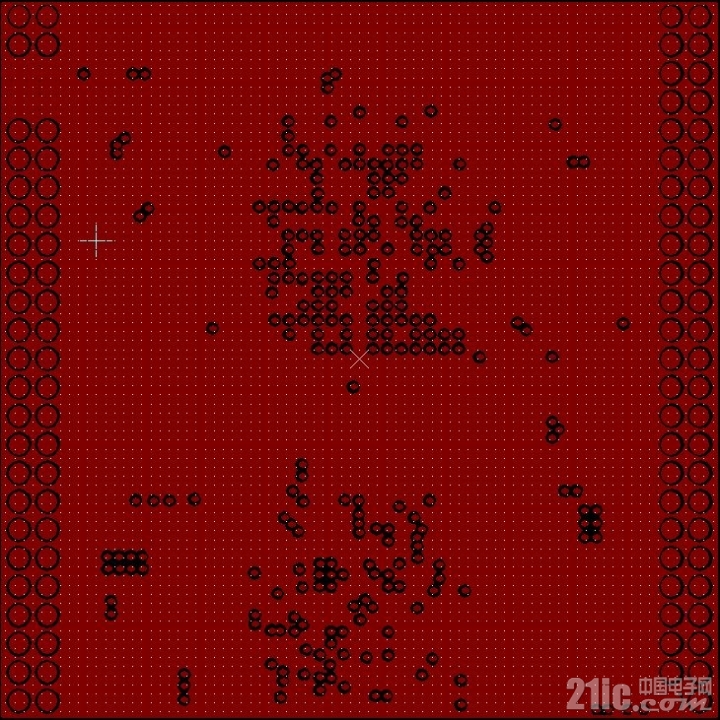

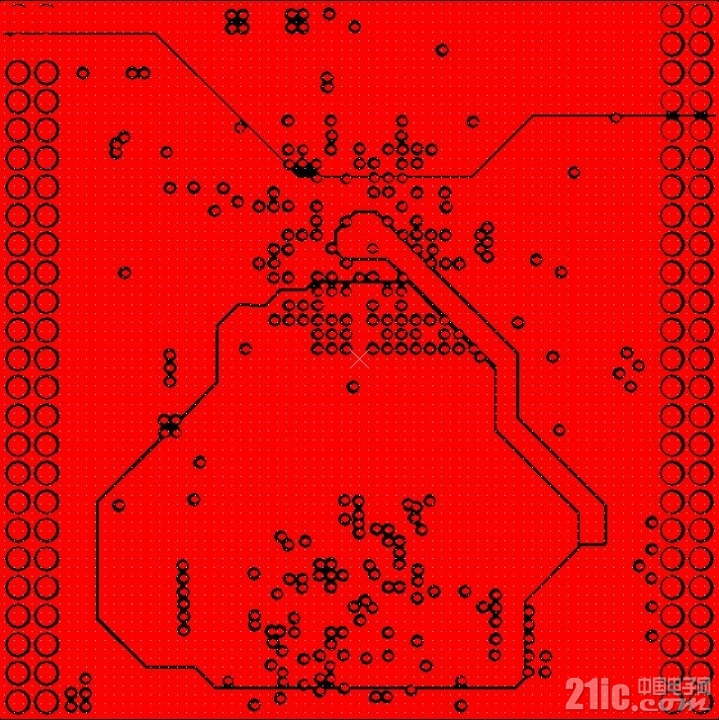

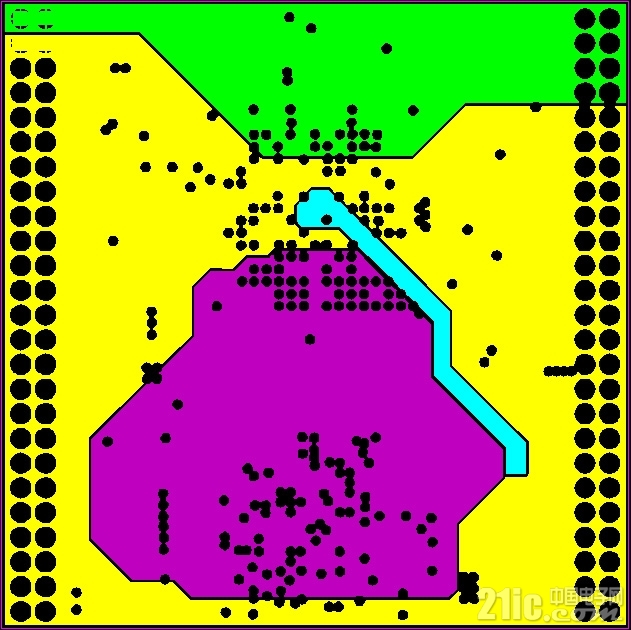

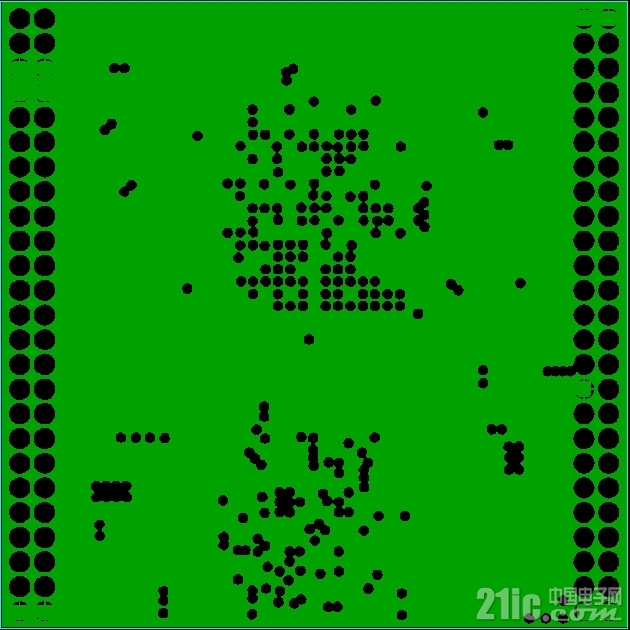

板子采用4层PCB,板子大小5cm x 5cm,层叠情况:Top -> GND -> Power -> Bottom板子芯片情况:

(1) FPGA: Xilinx Spartan6系列的XC6SLX16-FTG256

(2) DDR3: Micron的MT41J128M16,2Gbit存储容量

(2) 电源:采用2片Onsemi的NCP1529分别为FPGA Core 1.2V和DDR3 1.5V提供电源

/**************************************************************************/

立帖为证

/**************************************************************************/

/****************************2016-08-23 V02版本完成*********************************/

/**************************************************************************/

黑 {MOD}底板果然好看多了。

/**************************************************************************/

/****************************2016-07-26 完成*********************************/

/**************************************************************************/

2Gbit全地址空间测试完成,用的是Xilinx提供的MCB IP硬核,下面是原理图,测试程序和说明书,

请翻滚帖子至最后, 欢迎下载。

/**************************************************************************/

/****************************2016-07-23 更新*********************************/

/**************************************************************************/

经测试,第一版的DDR3可以正常稳定运行在400MHz,全地址空间读写数据无任何问题。

现在开始准备第二版,打算生成100个pcb,并且会将阻焊颜 {MOD}由绿 {MOD}改为黑 {MOD}。

具体设计细节和第一版的区别如下:

(1) IO引脚数量由原来的80个增加到86个IO;

(2) 所有引出的差分线尽量保持等长;

(3) 电容部分进行了改进,每个DC/DC输出都增加了铝电解电容,增加可靠性,铝电解电容都放在背面。

下面是第二版的图片:

/**************************************************************************/

/****************************2016-07-19 更新*********************************/

/**************************************************************************/

搞了一个上午,终于搞定第一个板子,FPGA的1.2V VDDCore电压,1.5V的DDR3供电电压,

VREF的0.75V电压都OK。往FPGA内部下载点灯程序OK,往SPI FLASH固化程序也OK。

下一步,DDR3 的MCB实现。。。。。。

/**************************************************************************/

/****************************2016-07-18 更新*********************************/

/**************************************************************************/

PCB打样回来了,5mil/5mil的线宽线距,10mil的过孔,花了我好多大洋!!!赶紧贴板子去了!!

贴完再上照。

/**************************************************************************/

/****************************2016-07-10 更新*********************************/

/**************************************************************************/

经过不知道多少个工作日空余时间和周末业余时间,终于大致设计板子浮出水面,等待后续检查。

板子采用4层PCB,板子大小5cm x 5cm,层叠情况:Top -> GND -> Power -> Bottom板子芯片情况:

(1) FPGA: Xilinx Spartan6系列的XC6SLX16-FTG256

(2) DDR3: Micron的MT41J128M16,2Gbit存储容量

(2) 电源:采用2片Onsemi的NCP1529分别为FPGA Core 1.2V和DDR3 1.5V提供电源

/**************************************************************************/

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

顶一把,

膜拜搞这种速度的人。

(1) CY7C68013 USB

(2) STM32F407/STM32F429

(3) 千兆以太网

(4) AD9288高速双通道ADC

(5) 高速DAC

(6) CMOS摄像头接口 + TFT液晶屏接口 or ADV7123 RGB->VGA

(7) ...

另外,这方面的板子没必要自己做,淘宝已经烂天下了,花更多的时间去系统架构和算法上吧!

一周热门 更多>