本帖最后由 haoxingheng 于 2020-1-12 23:12 编辑

Zynq高速串行CMOS接口的设计与实现作者:hello,panda

[受论坛对发帖的字数限制,本文分为上下两部分,本篇为下部分]。

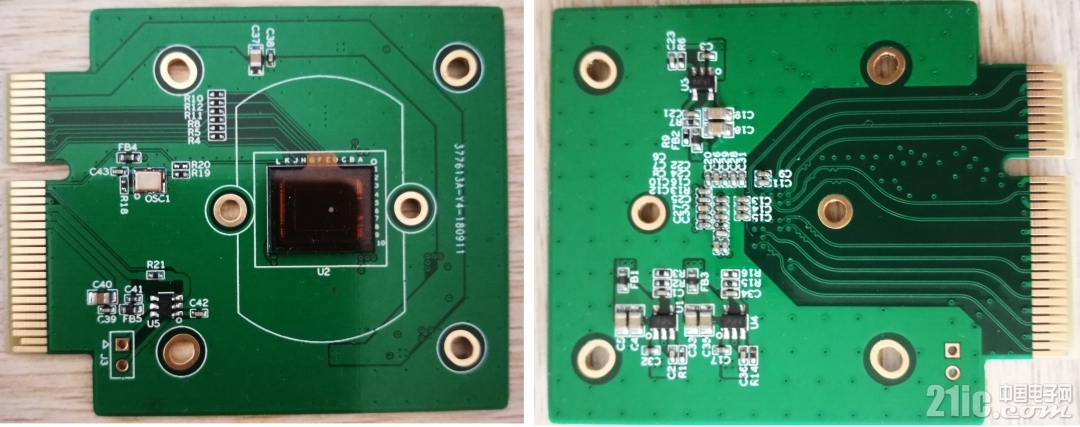

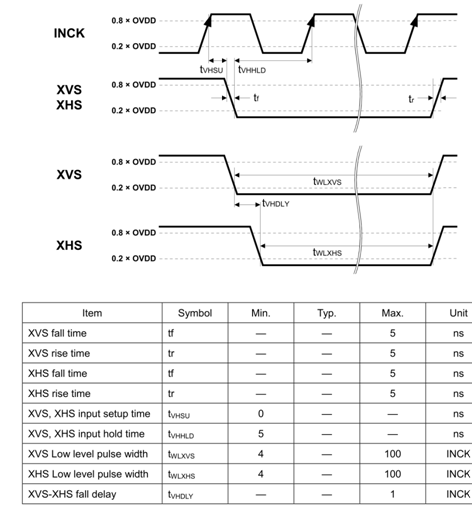

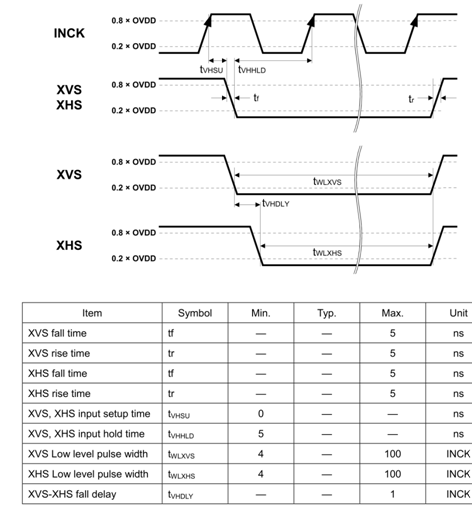

2 LVDS高速接口实现实例因为MIPI接口有其完整的物理层协议,因此不在这里讲具体实现,本文以Sony的IMX122 CMOS为例,聊一聊高速LVDS(HiSPi类似,只是电平标准有一点区别)接口在Xilinx 7系列FPGA和Zynq SoC上的实现。2.1 需求分析以Sony IMX122 CMOS为例,配置在1080P分辨率可输出30fps。CMOS在初始化完成后输出两通道稳定的LVDS数据,LVDS接收模块在收到配置完成信号后开始工作。因此,这个LVDS接收模块需要实现:① CMOS工作在Slave模式下,向CMOS发出参考时钟(INCK)、行同步(XHS)、帧同步(XVS)信号;② 接收LVDS数据并将它恢复成为指定的图像数据格式;③ 提供测试信息接口。2.2 IMX122 CMOS输出特性本小节简介IMX122 CMOS的一些特性。2.2.1 同步时序要求在Slave模式下需要向CMOS提供周期稳定的XHS和XVS信号,两者的时序要求如图7所示。在产生同步时序时需要注意以下要点:① XVS和XHS必须是稳定的周期性信号;② XVS和XHS信号的低电平保持时间为4~100个INCK;③ XHS可以和XVS同时拉低,也可延时一个时钟周期拉低。

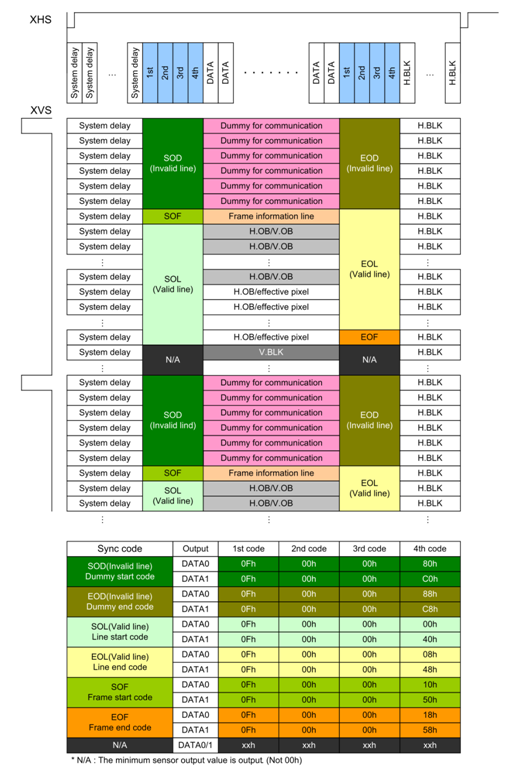

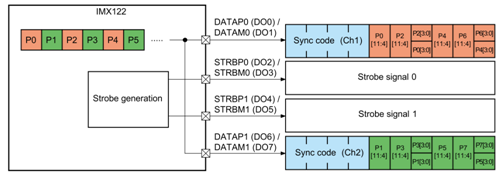

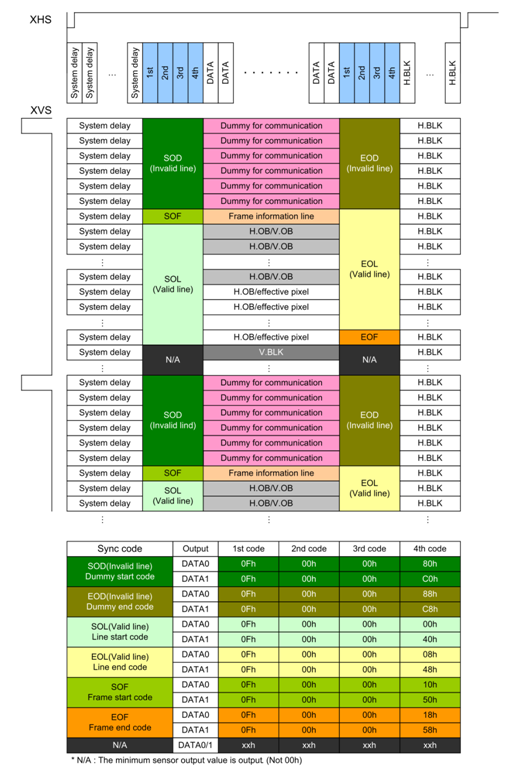

图7 Slave模式下同步时序2.2.2 输出数据率在串行SDR LVDS模式下以12bit模式输出,数据率为891Mbps,每个通道的数据率为445.5Mbps。2.2.3 Sync Code格式在串行输出模式下,CMOS通过输出固定的Sync Code来指示图像的有效帧、行信息,接收器需通过查找这些Sync Code来恢复图像。IMX122可提供两种模式的Sync Code,这里配置为Sync Code1,其具体定义如图8所示。

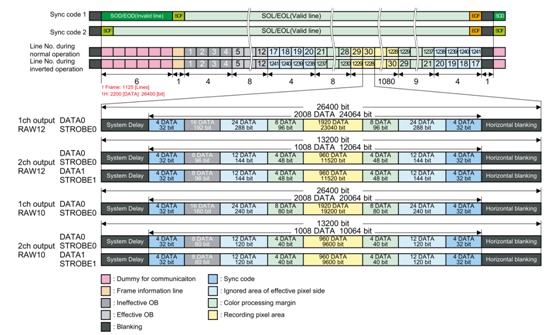

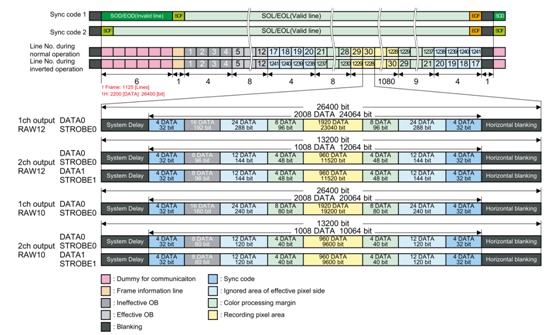

图8 IMX122 Sync Code定义2.2.4 输出图像组织形式IMX122在1080P读出模式下,输入参考时钟INCK是37.125MHz。一帧图像输出固定为1125行,每行1100 INCK(29.63μs),有效输出为1984×1105。图像输出的时序如图9所示,图10是输出数据编码规则。

图9 IMX122 LVDS模式输出时序

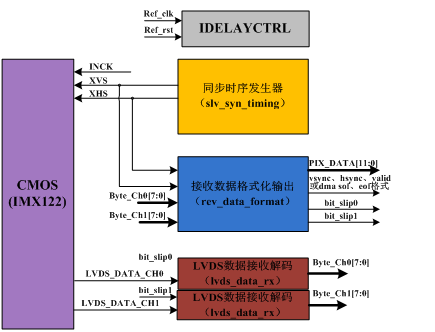

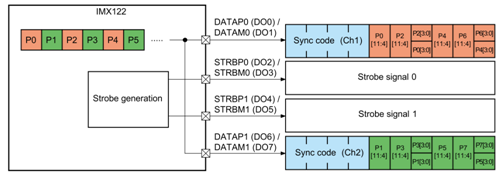

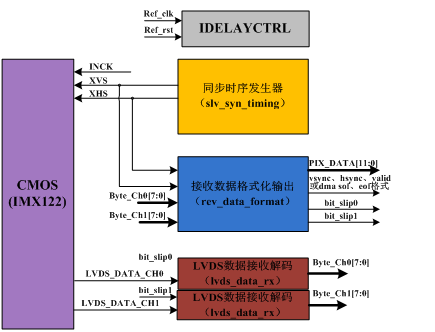

图10 IMX122 12-bit 2通道输出编码格式2.3 设计思路和模块结构Slave模式下工作的CMOS在XVS和XHS的同步下按照固定时序稳定输出LVDS图像数据。LVDS串行数据按照一定的方式进行编码,接收模块应先将串行数据解码恢复成为并行数据,再根据数据的排列方式格式化输出。因此,整个模块可以划分为时序同步、LVDS接收解码(串转并)和数据格式化输出三个部分。整个LVDS接收模块的结构如图11所示。

图11 LVDS接收模块顶层图① CMOS输入参考时钟(INCK)为37.125MHz;② CMOS输出LVDS数据为445.5MHz SDR型;③ 时序发生器由74.25MHz发生30fps的XVS、XHS信号;④ LVDS数据接收解码模块将数据恢复为8bit@55.6875MHz并行格式(DATA[7:0]);⑤ 格式化输出模块通过搜索同步头的状态确定是否发出bit_slip,并根据CMOS的数据格式和同步信号格式化输出12bit@74.25MHz像素数据(PIX_DATA[11:0]);⑥ IDELAYCTRL以Ref_clk为基准对整个IO BANK进行输入延时控制。2.3.1 时序同步同步时序由内部74.25MHz计数产生。按照图7所示时序即可。2.3.2 LVDS接收解码LVDS接收的主要工作是将串行的数据转为并行数据并进行自动相位调节,移位寄存器抽头调整(Bitslip)。Xilinx Artix7系列FPGA提供串转并模块ISERDES和IO延时模块IODELAYE2,ISERDES性能可在415Mb/s~1200Mb/s之间,IODELAYE2的延时参考时钟可以是200MHz(1tap≈78ps)或300MHz(1tap≈52ps)。(1)Artix7 FPGA时钟特性在Artix7系列器件里,MMCM可驱动BUFIO、BUFR、BUFH和BUFG,PLL只能驱动BUFH和BUFG。ZYNQ-7020采用Artix7 Speed-1器件,时钟网络的最高性能如下表5所示。表5 Artix7 Speed-1 器件时钟性能FPGABUFGBUFHBUFRBUFIOArtix7 Speed-1464MHz464MHz315MHz600MHz

Zynq高速串行CMOS接口的设计与实现作者:hello,panda

[受论坛对发帖的字数限制,本文分为上下两部分,本篇为下部分]。

2 LVDS高速接口实现实例因为MIPI接口有其完整的物理层协议,因此不在这里讲具体实现,本文以Sony的IMX122 CMOS为例,聊一聊高速LVDS(HiSPi类似,只是电平标准有一点区别)接口在Xilinx 7系列FPGA和Zynq SoC上的实现。2.1 需求分析以Sony IMX122 CMOS为例,配置在1080P分辨率可输出30fps。CMOS在初始化完成后输出两通道稳定的LVDS数据,LVDS接收模块在收到配置完成信号后开始工作。因此,这个LVDS接收模块需要实现:① CMOS工作在Slave模式下,向CMOS发出参考时钟(INCK)、行同步(XHS)、帧同步(XVS)信号;② 接收LVDS数据并将它恢复成为指定的图像数据格式;③ 提供测试信息接口。2.2 IMX122 CMOS输出特性本小节简介IMX122 CMOS的一些特性。2.2.1 同步时序要求在Slave模式下需要向CMOS提供周期稳定的XHS和XVS信号,两者的时序要求如图7所示。在产生同步时序时需要注意以下要点:① XVS和XHS必须是稳定的周期性信号;② XVS和XHS信号的低电平保持时间为4~100个INCK;③ XHS可以和XVS同时拉低,也可延时一个时钟周期拉低。

一周热门 更多>