本帖最后由 FPGA明德扬 于 2020-1-3 10:47 编辑

作者:纳兰公子本文为明德扬原创文章,转载请注明出处!

最近在做4k-led的项目,一个接收卡驱动的led的点数是1024 * 256,今天来分享一下FPGA驱动led的原理,接收卡的板卡如下图所示:

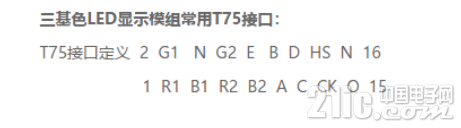

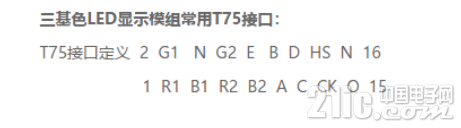

一个接收卡包含了16个HUB75接口,一个HUB75接口驱动64*256个点,那么16个驱动一共有16*64*256 = 1024*256个点。首先来看一下HUB75接口的定义,如下图所示:

一、 显示的原理:

每一个HUB75接口由R1/B1/G1/和R2/G2/B2组成,也就是说一个64扫的LED屏是由两个32扫的RGB组成的,分为上下两屏,即一个地址是同时选中了两行的。

16个HUB75接口的相对应的是同时显示的,即第0 32 64 96 128 行 …… 是同时显示的。

到了第二次循环的时候地址加1,此时同时显示是第1 33 65 97 ……

如此下去直到1024行显示完毕,利用人眼的视觉残留效果显示一副图像。

二、SDRAM储存量计算

此项目在硬件上用FPGA+SDRAM(一片)的架构。

图像来了之后先储存在SDRAM,那么SDRAM是如何划分的?SDRAM的速率带宽是多少?又是如何计算的?我们一起来讨论一下。

一副图像的信息量是1024*256,则一个点是RGB888,那么信息量是1024*256*24 bit;一秒钟来60帧图像,那么1秒来的数据量是1024*256*24*60 bit = 377,487,360 bit ,约等于380M bit;如果是按照来一副图像则显示一副图像的时候,那么SDRAM的速度要求为380*2 =760M bit,现在来一副图像的时候是根据19场原理来显示的话(19场原理这里就不做介绍了)则有SDRAM的要求为380 * 3.5 = 1330Mbit。在此项目中我们使用的SDRAM的数据位宽为32位,时钟频率为100M,则有根据SDRAM的效率为70%来算的由32*100*0.7 = 2100Mbit>1330Mbit,SDRAM的速率满足要求。

三、SDRAM储存图像的原理

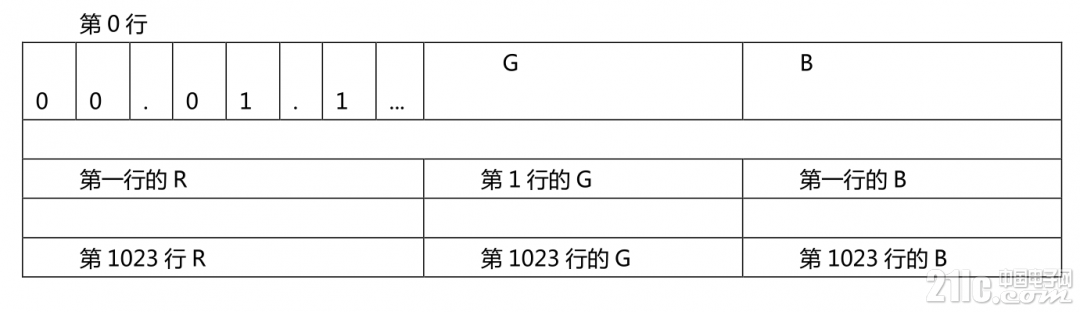

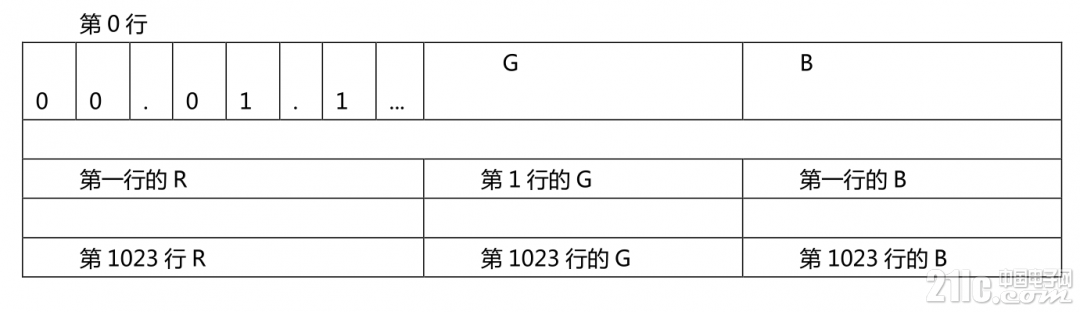

SDRAM的位宽是32位,一行有256*24 bit = y * 32,则y=192。即一行图像在SDRAM中占据了192个地址。那么则有R 、G 、B三种颜 {MOD}各自占据了64个地址,其中R[7:0]的R[0]占了8个地址,同理R[1]占了8个地址,以此类推每一个场占了8个地址,那么SDRAM可以划分如下:

也就是说第0行的R[0]地址0-7,R[1]:8-15,……,R[7]:55-63, G[0]:64-71 , ......,G[7]:120-127, ......同理下去;

第一行的R[0]: 192 ....199, R[1] : 200.....207, .........., ..... .......

第二行:R[0]:384....391, .... ..... ..........................................一直到1023行

地址的计算:

R: cnt0*192 + cnt1 * 8G: cnt0 *192 + cnt1 * 8+64B: cnt0 * 192 + cnt1*8+128

cnt0:表示第几行,cnt1表示第几场。

这就是我们划分SDRAM的数据的存储过程。

对此技术感兴趣的朋友可以联系明德扬,也可在评论中与我讨论!

作者:纳兰公子本文为明德扬原创文章,转载请注明出处!

最近在做4k-led的项目,一个接收卡驱动的led的点数是1024 * 256,今天来分享一下FPGA驱动led的原理,接收卡的板卡如下图所示:

一个接收卡包含了16个HUB75接口,一个HUB75接口驱动64*256个点,那么16个驱动一共有16*64*256 = 1024*256个点。首先来看一下HUB75接口的定义,如下图所示:

一、 显示的原理:

每一个HUB75接口由R1/B1/G1/和R2/G2/B2组成,也就是说一个64扫的LED屏是由两个32扫的RGB组成的,分为上下两屏,即一个地址是同时选中了两行的。

16个HUB75接口的相对应的是同时显示的,即第0 32 64 96 128 行 …… 是同时显示的。

到了第二次循环的时候地址加1,此时同时显示是第1 33 65 97 ……

如此下去直到1024行显示完毕,利用人眼的视觉残留效果显示一副图像。

二、SDRAM储存量计算

此项目在硬件上用FPGA+SDRAM(一片)的架构。

图像来了之后先储存在SDRAM,那么SDRAM是如何划分的?SDRAM的速率带宽是多少?又是如何计算的?我们一起来讨论一下。

一副图像的信息量是1024*256,则一个点是RGB888,那么信息量是1024*256*24 bit;一秒钟来60帧图像,那么1秒来的数据量是1024*256*24*60 bit = 377,487,360 bit ,约等于380M bit;如果是按照来一副图像则显示一副图像的时候,那么SDRAM的速度要求为380*2 =760M bit,现在来一副图像的时候是根据19场原理来显示的话(19场原理这里就不做介绍了)则有SDRAM的要求为380 * 3.5 = 1330Mbit。在此项目中我们使用的SDRAM的数据位宽为32位,时钟频率为100M,则有根据SDRAM的效率为70%来算的由32*100*0.7 = 2100Mbit>1330Mbit,SDRAM的速率满足要求。

三、SDRAM储存图像的原理

SDRAM的位宽是32位,一行有256*24 bit = y * 32,则y=192。即一行图像在SDRAM中占据了192个地址。那么则有R 、G 、B三种颜 {MOD}各自占据了64个地址,其中R[7:0]的R[0]占了8个地址,同理R[1]占了8个地址,以此类推每一个场占了8个地址,那么SDRAM可以划分如下:

也就是说第0行的R[0]地址0-7,R[1]:8-15,……,R[7]:55-63, G[0]:64-71 , ......,G[7]:120-127, ......同理下去;

第一行的R[0]: 192 ....199, R[1] : 200.....207, .........., ..... .......

第二行:R[0]:384....391, .... ..... ..........................................一直到1023行

地址的计算:

R: cnt0*192 + cnt1 * 8G: cnt0 *192 + cnt1 * 8+64B: cnt0 * 192 + cnt1*8+128

cnt0:表示第几行,cnt1表示第几场。

这就是我们划分SDRAM的数据的存储过程。

对此技术感兴趣的朋友可以联系明德扬,也可在评论中与我讨论!

一周热门 更多>