本帖最后由 FPGA明德扬 于 2019-12-26 10:57 编辑

作者:小黑同学本文为明德扬原创文章,转载请注明出处!

本模块的功能,是从一串输入的数据中,检测出指令头55D5,检测出包文头后,获取到紧接着的4个数据(2字节),并按字节为单位送给下游模块。指令头和无效数据则丢弃。

输入的包文指令格式:

输入的数据din为4比特,假设其依次输入:5、5、d、5、0、2、9、9、1、5、5、d、5、0、1、0、3其中前两个字节55d5就表示指令头,后一个字节02表示地址,再一个字节99表示数据。紧跟着后面的1为无效数据,往后又检测到55d5,则01为地址,03为数据。把指令头、无效的数据过滤掉(即dout_vld为0),最终输出以字节为单位的02、99、01、03。

一、设计架构

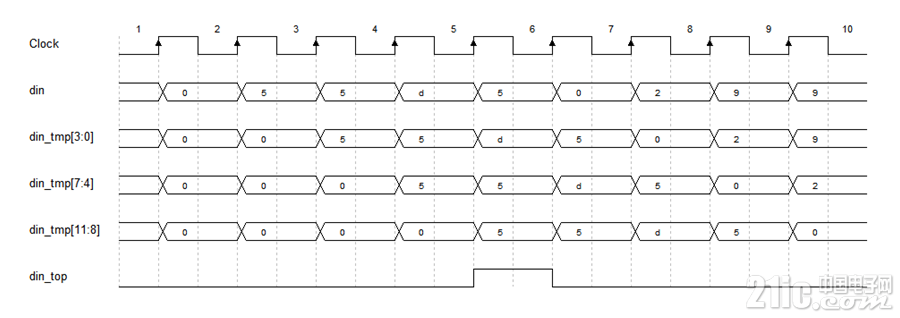

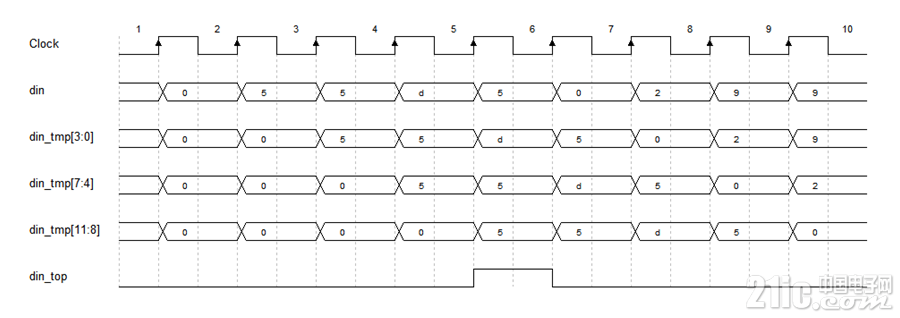

检测出指令头的方法如下:

检测出包文头后,需要对后面的4个数据进行计数。每2个数据组成1个字节,一共有2个字节。所以指令检测模块采用两个计数器的结构,这两个计数器分别对应接收一个字节需要的数据个数和接收字节数,其结构图如下所示:

计数器cnt0:数据个数计数器。对接收一个字节需要的数据进行计数,接收一个字节需要2个数据。该计数器的计数周期为2。计数器cnt1:字节数计数器。对接收的字节数进行计数,地址加上数据共两个字节。该计数器的计数周期为2。

二、信号的意义

信号类型意义clk输入信号时钟信号。rst_n输入信号复位信号,低电平有效。din输入信号输入的数据,位宽为4bitdin_vld输入信号输入数据有效指示信号。当其为1时,表示输入的数据有效,为0时表示输入数据无效。dout输出信号输出数据,位宽为8bit(1字节)。设计逻辑:在取数据状态时,每2个数据拼接成1字节输出。dout_vld输出信号输出数据有效指示信号,位宽为1bit。设计逻辑:在取数据状态,每取到1个字节数据就输出1个有效指示停车。cnt0中间信号数据个数计数器。用于对接收一个字节需要的数据个数进行计数,接收一个字节需要两个输入数据。该计数器的计数周期为2。add_cnt0中间信号数据个数计数器加1条件。设计逻辑:在取数据状态,输入有效此信号就有效。end_cnt0中间信号数据个数计数器的结束条件。设计逻辑:接收一个字节需要两个数据,所以数到两个就结束。cnt1中间信号字节数计数器。用于对地址和数据的字节数进行计数,地址和数据各占一个字节。该计数器的计数周期为2。add_cnt1中间信号字节数计数器加1条件。设计逻辑:每接收完1个字节,此计数器就加1。end_cnt1中间信号字节计数器结束条件。设计逻辑:地址和数据共两个字节,所以数到两个就结束。din_tmp中间信号输入数据din的寄存器信号。位宽为12位,由高到低,每4位组成一组数据,分别存储的din之前三个有效数据。详细请看设计架构部分。din_top中间信号指令头有效指示信号。设计逻辑:当前输入数据和之前的三个数据组成55D5时,就表示检测到指令头。flag_add中间信号取数据状态指示信号。当为1时,表示检测到包文头,此时处于取数据状态。设计逻辑:指令头有效时,就变1;当取完4个数据后就变0。

作者:小黑同学本文为明德扬原创文章,转载请注明出处!

本模块的功能,是从一串输入的数据中,检测出指令头55D5,检测出包文头后,获取到紧接着的4个数据(2字节),并按字节为单位送给下游模块。指令头和无效数据则丢弃。

输入的包文指令格式:

输入的数据din为4比特,假设其依次输入:5、5、d、5、0、2、9、9、1、5、5、d、5、0、1、0、3其中前两个字节55d5就表示指令头,后一个字节02表示地址,再一个字节99表示数据。紧跟着后面的1为无效数据,往后又检测到55d5,则01为地址,03为数据。把指令头、无效的数据过滤掉(即dout_vld为0),最终输出以字节为单位的02、99、01、03。

一、设计架构

检测出指令头的方法如下:

检测出包文头后,需要对后面的4个数据进行计数。每2个数据组成1个字节,一共有2个字节。所以指令检测模块采用两个计数器的结构,这两个计数器分别对应接收一个字节需要的数据个数和接收字节数,其结构图如下所示:

计数器cnt0:数据个数计数器。对接收一个字节需要的数据进行计数,接收一个字节需要2个数据。该计数器的计数周期为2。计数器cnt1:字节数计数器。对接收的字节数进行计数,地址加上数据共两个字节。该计数器的计数周期为2。

二、信号的意义

信号类型意义clk输入信号时钟信号。rst_n输入信号复位信号,低电平有效。din输入信号输入的数据,位宽为4bitdin_vld输入信号输入数据有效指示信号。当其为1时,表示输入的数据有效,为0时表示输入数据无效。dout输出信号输出数据,位宽为8bit(1字节)。设计逻辑:在取数据状态时,每2个数据拼接成1字节输出。dout_vld输出信号输出数据有效指示信号,位宽为1bit。设计逻辑:在取数据状态,每取到1个字节数据就输出1个有效指示停车。cnt0中间信号数据个数计数器。用于对接收一个字节需要的数据个数进行计数,接收一个字节需要两个输入数据。该计数器的计数周期为2。add_cnt0中间信号数据个数计数器加1条件。设计逻辑:在取数据状态,输入有效此信号就有效。end_cnt0中间信号数据个数计数器的结束条件。设计逻辑:接收一个字节需要两个数据,所以数到两个就结束。cnt1中间信号字节数计数器。用于对地址和数据的字节数进行计数,地址和数据各占一个字节。该计数器的计数周期为2。add_cnt1中间信号字节数计数器加1条件。设计逻辑:每接收完1个字节,此计数器就加1。end_cnt1中间信号字节计数器结束条件。设计逻辑:地址和数据共两个字节,所以数到两个就结束。din_tmp中间信号输入数据din的寄存器信号。位宽为12位,由高到低,每4位组成一组数据,分别存储的din之前三个有效数据。详细请看设计架构部分。din_top中间信号指令头有效指示信号。设计逻辑:当前输入数据和之前的三个数据组成55D5时,就表示检测到指令头。flag_add中间信号取数据状态指示信号。当为1时,表示检测到包文头,此时处于取数据状态。设计逻辑:指令头有效时,就变1;当取完4个数据后就变0。

一周热门 更多>