作者:鱼丸粗面

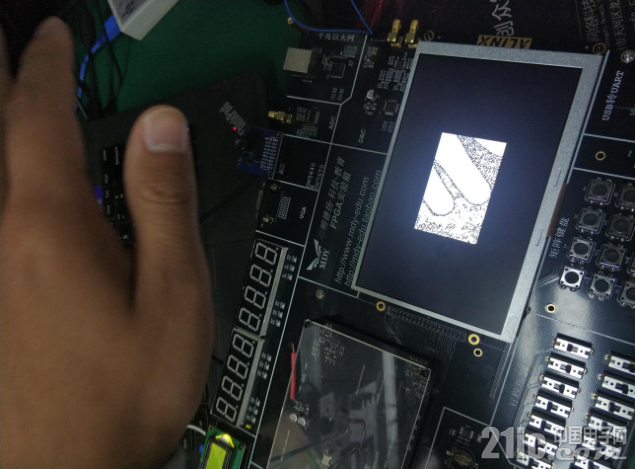

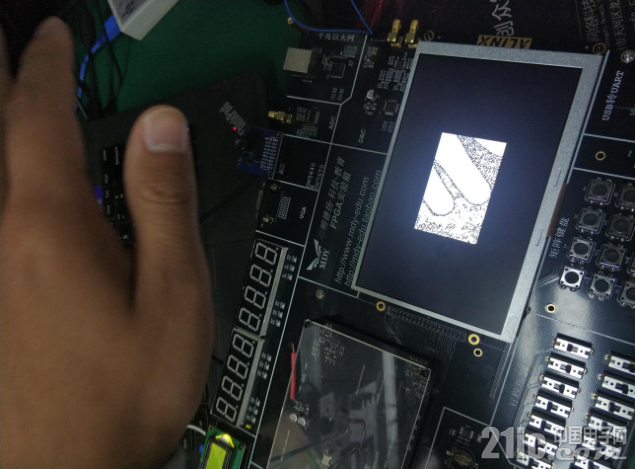

本文为明德扬原创文章,转载请注明出处! 明德扬开发板MP801有丰富的例程,共59个案例。其中一个有趣的案例是用MP801开发板实现一个边缘检测的功能。通过接入摄像头采集到外部图像数据,在FPGA中进行图像算法处理,最终能够通过VGA接口在显示屏上显示出采集到的外部图像的边缘信息。此例程在明德扬论坛上有更新,感兴趣的同学可以直接前往下载。 在官方论坛上的案例中,图像数据是通过VGA接口输出到显示屏上进行显示,输出的图像分辨率为640*480。今天我为大家重点介绍的是如何不使用VGA接口,而是通过一个7寸LCD屏幕显示出边缘检测的图像数据。显示效果如下图1所示:

图1 七寸LCD屏幕显示效果图

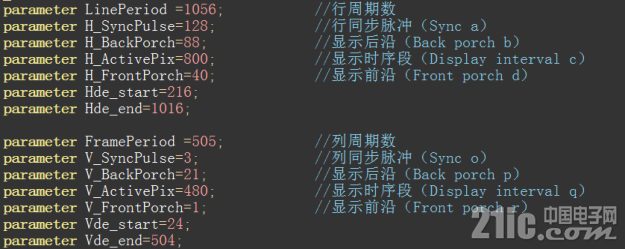

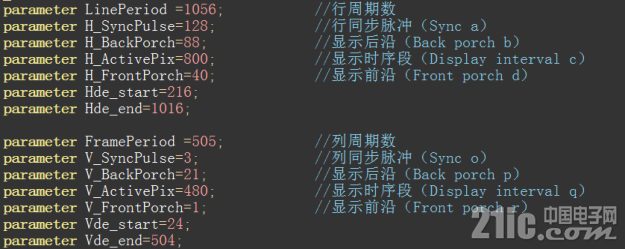

上图是在明德扬的高校实验箱上完成的测试,实验箱上核心板上的FPGA芯片型号与MP801开发板一致。其中,LCD屏幕的分辨率为800*480,数据接收格式为RGB888,并通过GPIO口与FPGA连接。由于此案例使用的是FPGA片内资源,最大只能存储320*200*1bit的两幅图像,因此无法保存一副完整的800*480分辨率的图像数据(存储两幅图像的目的是为了做数据读写乒乓操作)。最终输出的图像分辨率为320*200,也就是图中屏幕中间的部分。 此工程的模块与在MP801上实现的案例是一样的,直接拿过来使用,只是在显示模块vga_driver中做了部分修改。由于LCD屏的驱动时序与VGA的时序不一致,因此需要对显示模块进行适配的修改。首先需要先搞清LCD屏的驱动时序。 其中,LCD屏的行时序是: LCD屏显示方式从屏幕左上角一点开始,从左像右逐点显示,每显示完一行,再回到屏幕的左边下一行的起始位置,在这期间,需要对行进行消隐,每行结束时,用行同步信号进行同步;LCD的驱动有两种方式,一种为HV模式,另一种为DE模式,这两种模式都能驱动LCD屏,数据在DCLK的上升沿采样。 LCD屏的列时序为: 当显示完所有的行,形成一帧,用场同步信号进行场同步,并使LCD显示回到屏幕左上方,同时进行场消隐,开始下一帧。行、场的时序参数定义如下:

图2 LCD时序参数定义

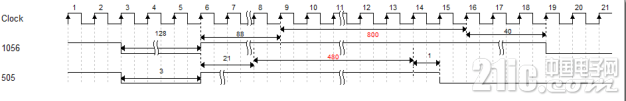

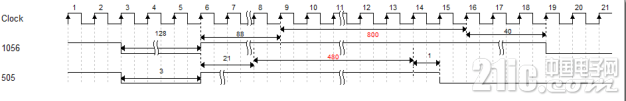

LCD行、场的时序图:其中行周期数是1056,列周期数是505,LCD显示的区域是800*480时序段,行、场数通过计数器进行计数。

图3 LCD行、场时序图

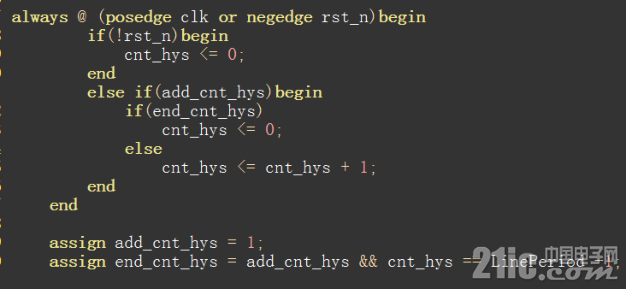

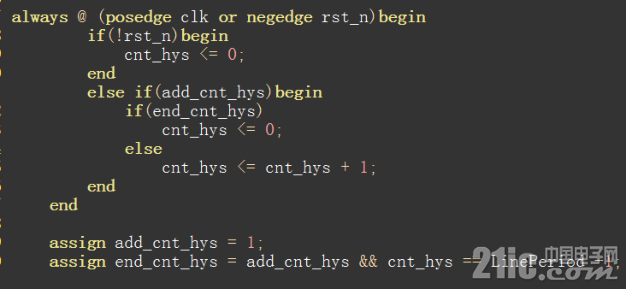

水平扫描计数代码:

图4 水平扫描计数

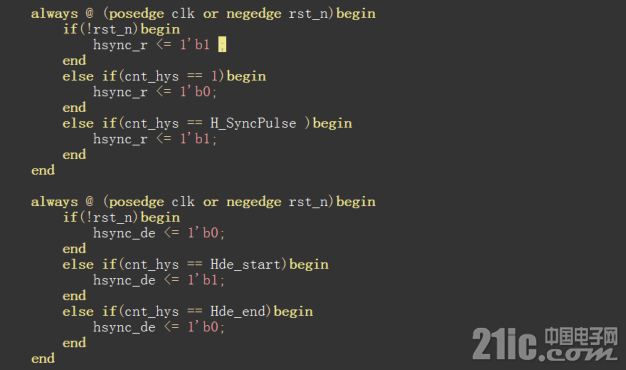

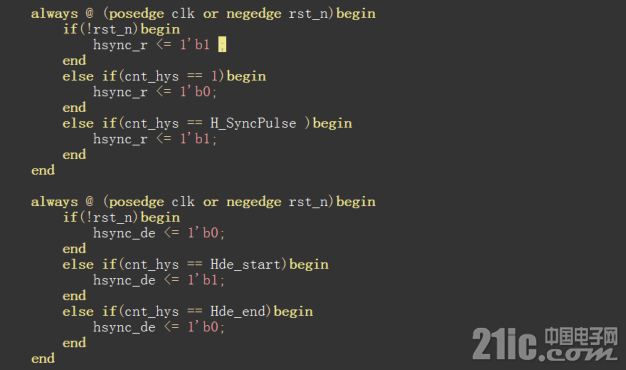

行同步信号hsync_r以及行有效显示信号hsync_de:

图5 行同步信号以及行有效显示信号

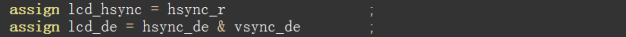

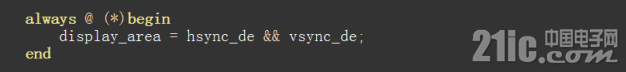

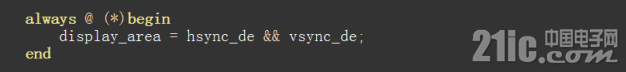

场信号也是按照上面的时序来进行设计,主要是为了得到场同步信号vsync_r和场有效显示信号vsync_de。有效显示信号lcd_de是在这两个信号同时有效时才拉高。当lcd_de拉高时,输出的像素值在LCD屏幕上显示。

图6 LCD屏幕显示区域

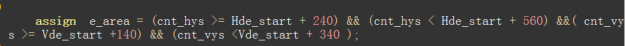

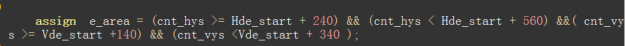

由于RAM中保存的数据数量最大为320*200,因此在LCD屏上最大只能有320*200的外部数据显示区域:

图7 RAM中存储数据显示区域

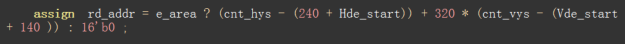

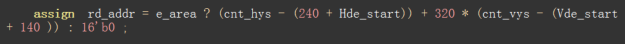

驱动模块向RAM中输入读地址以读取RAM中存储的数据:

图8 读地址设计

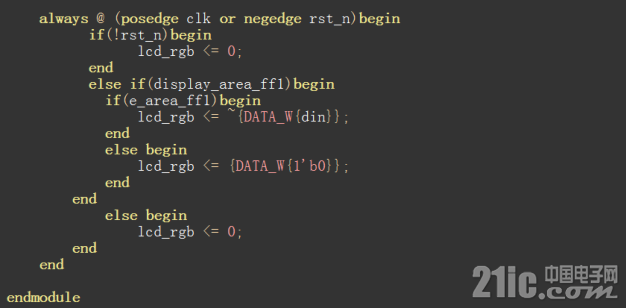

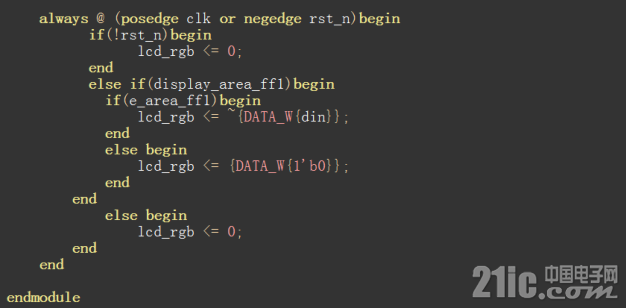

最终在LCD屏上输出的RGB信号:

图9 输出RGB信号

总结: 由于RAM的资源限制,RAM中存储的一副图像最大只能有320*200的像素点,因此导致输出到LCD屏幕上的像素最大也只能为320*200,摄像头采集到的一帧640*480的图像数据会有大部分被丢弃掉,这也导致了显示出来的效果不是很理想。想要解决这个问题,就只能增大存储空间,通过外部存储器如SDRAM,将摄像头输出的整幅图像都保存起来然后在LCD屏幕上显示。目前我们正在做这一工程的移植,并且还会增加许多有趣的功能,提供很有意思的玩法。

想要源代码或者感兴趣的同学可以加下面本人的联系方式:QQ1479512800,期待与大家一起探讨进步!

本文为明德扬原创文章,转载请注明出处! 明德扬开发板MP801有丰富的例程,共59个案例。其中一个有趣的案例是用MP801开发板实现一个边缘检测的功能。通过接入摄像头采集到外部图像数据,在FPGA中进行图像算法处理,最终能够通过VGA接口在显示屏上显示出采集到的外部图像的边缘信息。此例程在明德扬论坛上有更新,感兴趣的同学可以直接前往下载。 在官方论坛上的案例中,图像数据是通过VGA接口输出到显示屏上进行显示,输出的图像分辨率为640*480。今天我为大家重点介绍的是如何不使用VGA接口,而是通过一个7寸LCD屏幕显示出边缘检测的图像数据。显示效果如下图1所示:

上图是在明德扬的高校实验箱上完成的测试,实验箱上核心板上的FPGA芯片型号与MP801开发板一致。其中,LCD屏幕的分辨率为800*480,数据接收格式为RGB888,并通过GPIO口与FPGA连接。由于此案例使用的是FPGA片内资源,最大只能存储320*200*1bit的两幅图像,因此无法保存一副完整的800*480分辨率的图像数据(存储两幅图像的目的是为了做数据读写乒乓操作)。最终输出的图像分辨率为320*200,也就是图中屏幕中间的部分。 此工程的模块与在MP801上实现的案例是一样的,直接拿过来使用,只是在显示模块vga_driver中做了部分修改。由于LCD屏的驱动时序与VGA的时序不一致,因此需要对显示模块进行适配的修改。首先需要先搞清LCD屏的驱动时序。 其中,LCD屏的行时序是: LCD屏显示方式从屏幕左上角一点开始,从左像右逐点显示,每显示完一行,再回到屏幕的左边下一行的起始位置,在这期间,需要对行进行消隐,每行结束时,用行同步信号进行同步;LCD的驱动有两种方式,一种为HV模式,另一种为DE模式,这两种模式都能驱动LCD屏,数据在DCLK的上升沿采样。 LCD屏的列时序为: 当显示完所有的行,形成一帧,用场同步信号进行场同步,并使LCD显示回到屏幕左上方,同时进行场消隐,开始下一帧。行、场的时序参数定义如下:

LCD行、场的时序图:其中行周期数是1056,列周期数是505,LCD显示的区域是800*480时序段,行、场数通过计数器进行计数。

水平扫描计数代码:

行同步信号hsync_r以及行有效显示信号hsync_de:

场信号也是按照上面的时序来进行设计,主要是为了得到场同步信号vsync_r和场有效显示信号vsync_de。有效显示信号lcd_de是在这两个信号同时有效时才拉高。当lcd_de拉高时,输出的像素值在LCD屏幕上显示。

由于RAM中保存的数据数量最大为320*200,因此在LCD屏上最大只能有320*200的外部数据显示区域:

驱动模块向RAM中输入读地址以读取RAM中存储的数据:

最终在LCD屏上输出的RGB信号:

总结: 由于RAM的资源限制,RAM中存储的一副图像最大只能有320*200的像素点,因此导致输出到LCD屏幕上的像素最大也只能为320*200,摄像头采集到的一帧640*480的图像数据会有大部分被丢弃掉,这也导致了显示出来的效果不是很理想。想要解决这个问题,就只能增大存储空间,通过外部存储器如SDRAM,将摄像头输出的整幅图像都保存起来然后在LCD屏幕上显示。目前我们正在做这一工程的移植,并且还会增加许多有趣的功能,提供很有意思的玩法。

想要源代码或者感兴趣的同学可以加下面本人的联系方式:QQ1479512800,期待与大家一起探讨进步!

一周热门 更多>