本帖最后由 FPGA明德扬 于 2019-12-19 09:33 编辑

作者:郑先生

本文为明德扬原创文章,转载请注明出处!

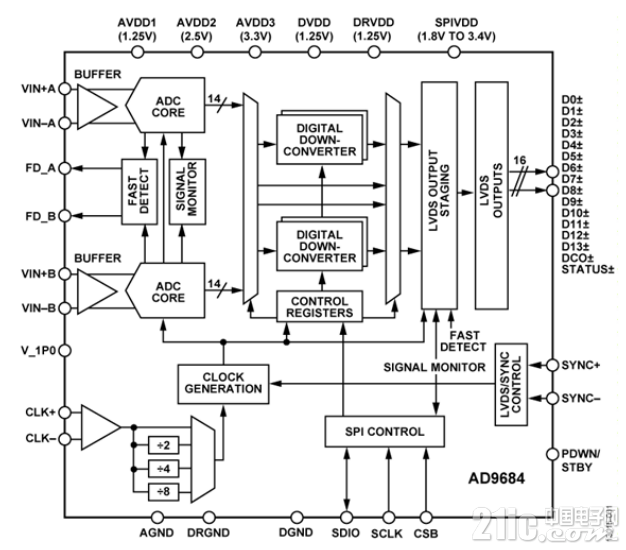

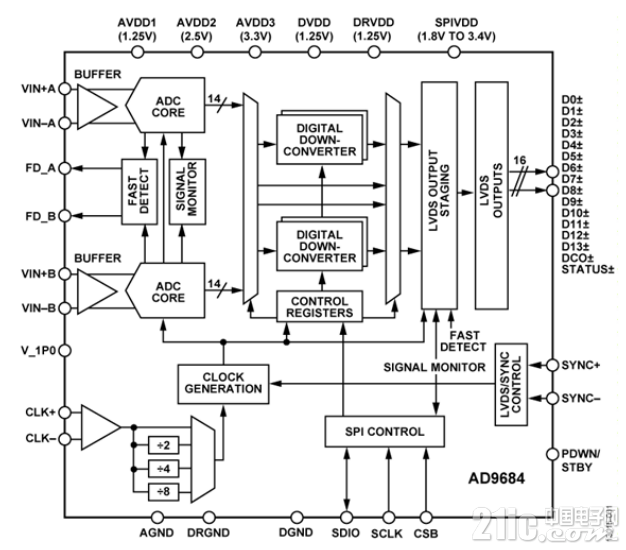

AD9684是一款双通道14位、500 MSPS采样率 ,并行LVDS接口的模数转换器。该芯片可用于通信,3G/4G, TD-SCDMA, W-CDMA, MC-GSM, LTE数字接收机,雷达,特殊领域激光测距。

该芯片有7个电源轨,3个数字电源轨和3个模拟电源轨,还有一个高精度参考电源轨,双通道模拟差分输入,输入数据通道分为高速采样数据时钟与同步信号输入,还有 SPI控制ADC芯片配置通道;数据通道输出为16对差分信号,分别为输出随路时钟,14位数据,Status信号。

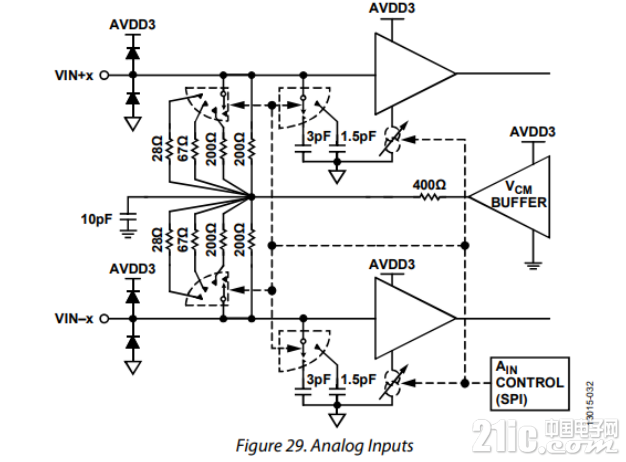

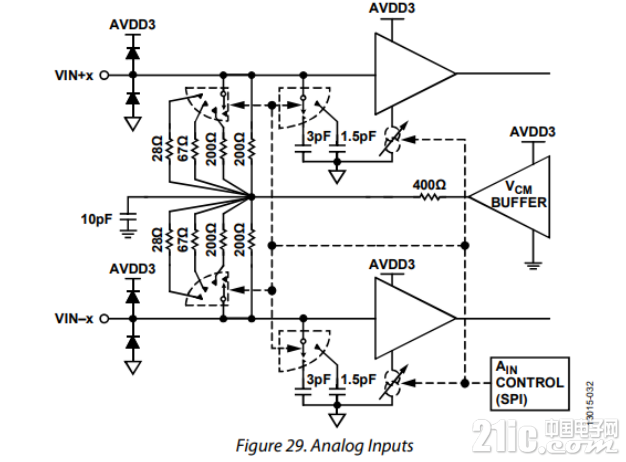

AD9684内置硬件FIR,DCO等功能,模拟通道输入阻抗可配置为400 Ohm, 200 Ohm,100 Ohm,50 Ohm。这些模式功能可以通过SPI通道对其进行配置。

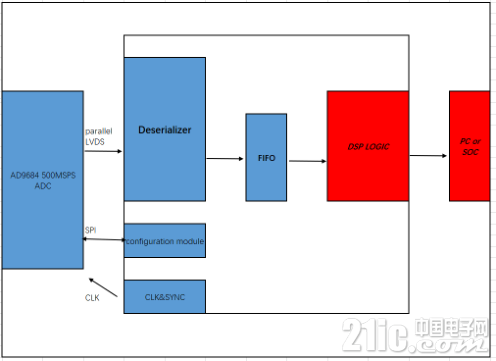

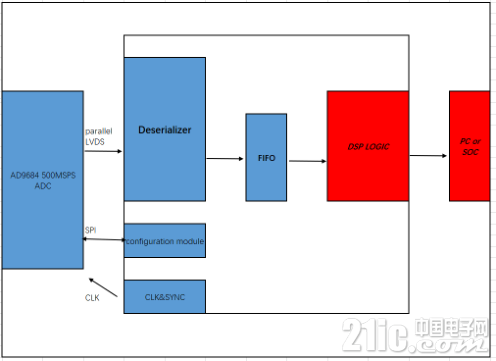

由于AD9684输出是并行LVDS数据,且采用的是DDR模式,所以500M采样率工作时,LVDS数据输出的随路时钟是250Mhz,一般的芯片没有可以的达到该速率的接收器,所以必须使用FPGA来作为该芯片的数据接收与后续的信号处理。

明德扬AD9684 ADC接口工程,已经使用Xilinx kintex-7实现这个ADC的接口数据接收驱动与后续信号处理。

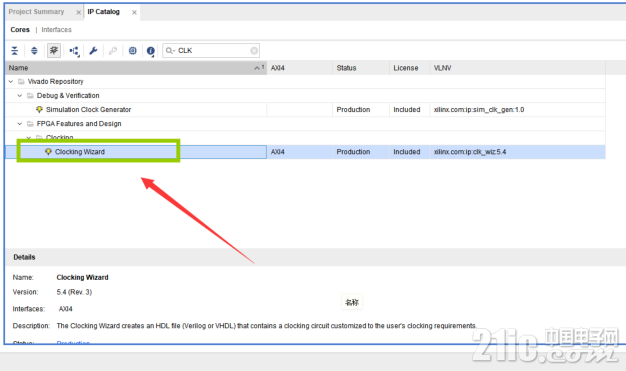

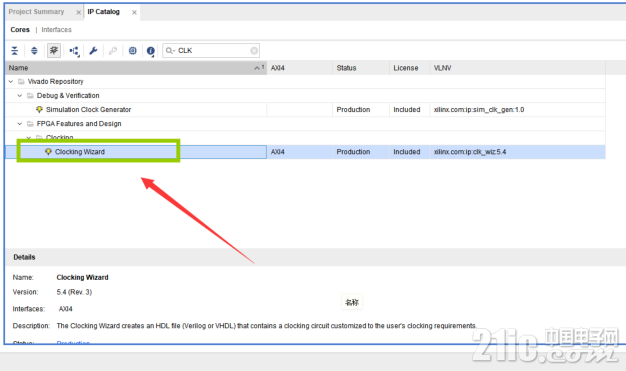

由于AD9684需要外部触发时钟输入,需要板卡上的外部基准时钟输入,通过FPGA内部的锁相环倍频产生一个时钟输出,以触发AD9684采样数据,对于Kintex-7器件,使用Vivado 的IP Catalog 配置一个PLL。

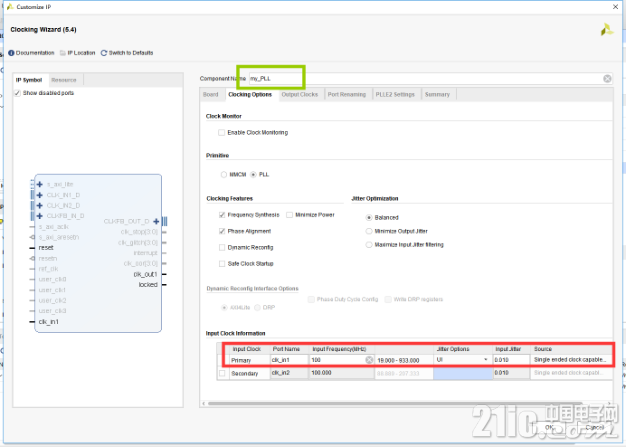

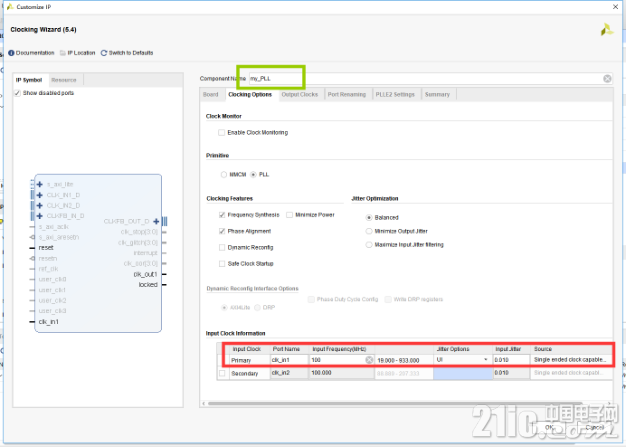

我们双击上图的绿 {MOD}框框,就可以进入IP核的配置界面,如下图所示:

绿 {MOD}框里面输入需要使用的IP核名字,红 {MOD}框中设置外部基准输入时钟,我们这里的板子的外部晶振输入时钟为100Mhz,所以这里输入100,输入抖动我们默认。之后点击上方的output clocks框,进入锁相环输出的配置。

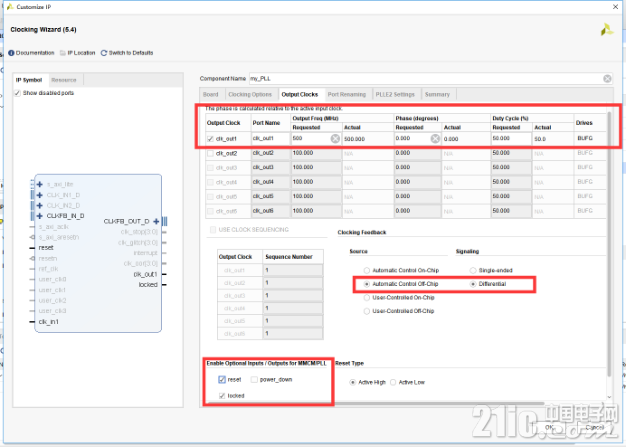

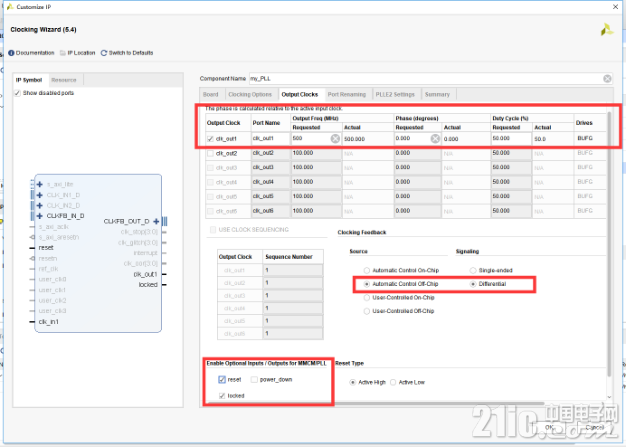

按照上图对其进行配置,这样的配置表明输出是500Mhz的时钟,占空比是50%。使能型号我们选择reset 跟PLL锁定标志信号locked。由于AD9684的触发时钟输入是需要LVDS电平,所以我们在这里使能差分信号,点击OK生成IP核。

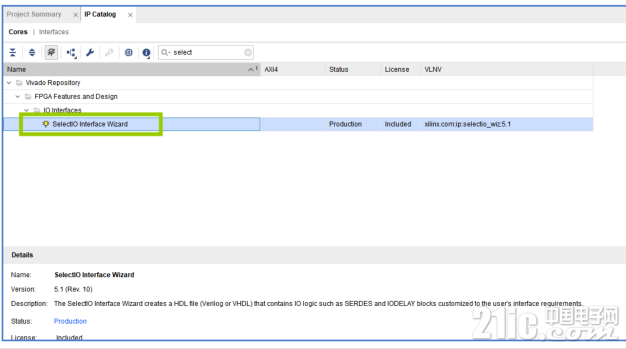

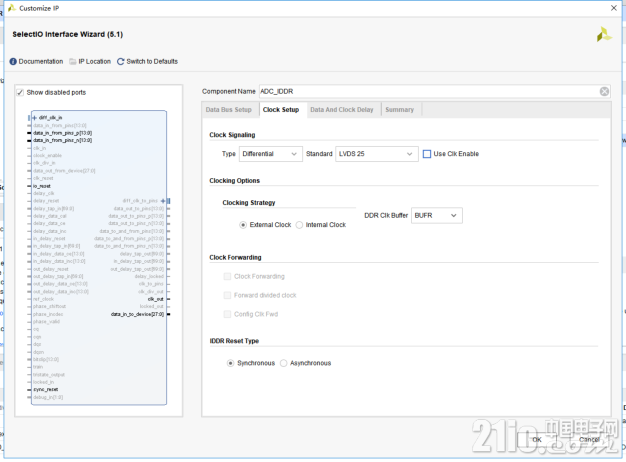

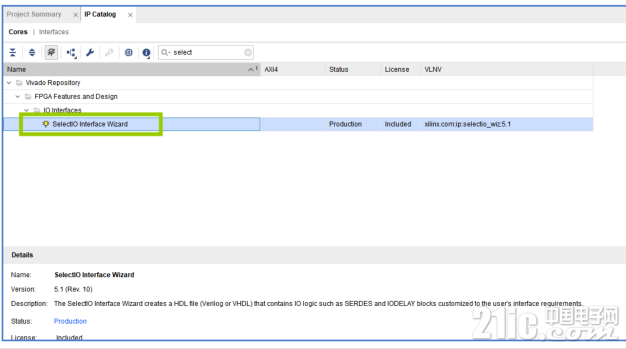

AD9684触发时钟配置完后,我们配置该芯片的接收器,由于这里AD9684是并行DDR模式的LVDS数据,所以我们需要使用的Xilinx selectIO IP核。双击下图的绿 {MOD}框可进入IP核配置界面。

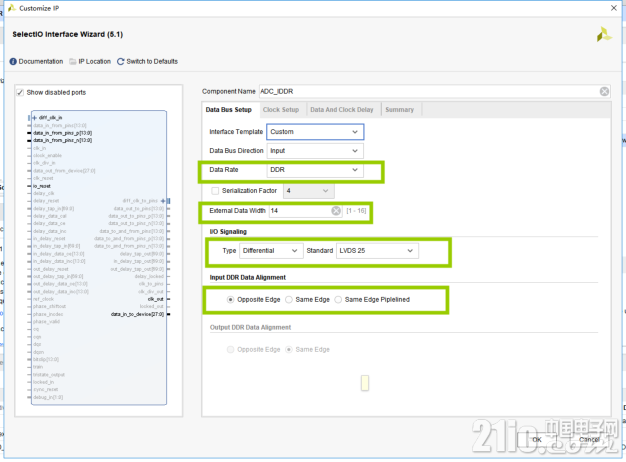

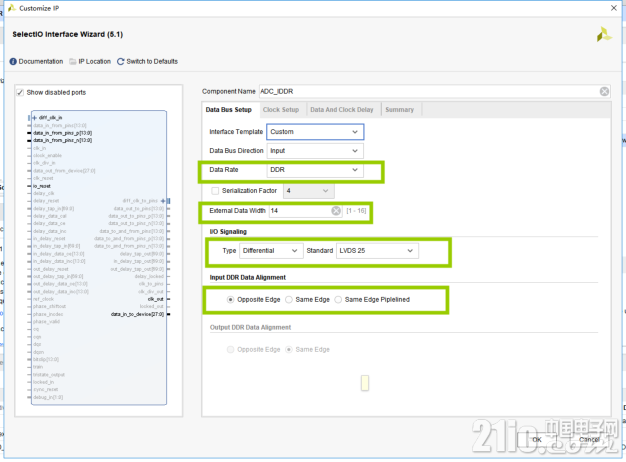

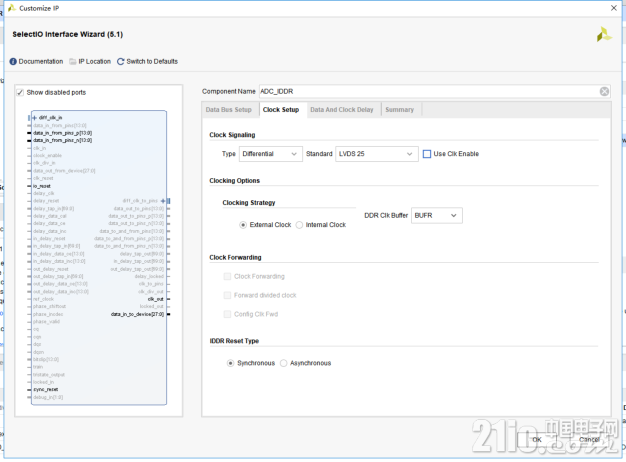

按照下图参数选择,配置14位LVDS电平输入的DDR接收器:

配置完以后点击OK生成IP核,生成后我们在TOP上对其进行例化,这里我们需要自己写一个SPI逻辑去配置AD9684,生成比特流文件接着烧写进板卡后就可以进行测试了。需要注意的是,在AD9684接收的数据通道与FPGA相连接的时候出现夸BANK行为的时候,综合后布局布线会报错,这里需要对其输入数据进行约束,甚至需要将数据通道的随路时钟先引入锁相环在接到我们配置好的Select IO IP核,但是这样做会导致时序出错,需要对所有数据通道进行时序约束以保证DDR接收器的建立时间与保持时间余量。如果不做时序约束,DDR接收器所采样的数据将会出现误码。

明德扬AD9684 ADC接口工程,已经做好时序约束测试完成,AD9684的各模式也测试完毕。想要了解更多的朋友可以联系明德扬,也欢迎在评论中与我进行交流讨论!

作者:郑先生

本文为明德扬原创文章,转载请注明出处!

AD9684是一款双通道14位、500 MSPS采样率 ,并行LVDS接口的模数转换器。该芯片可用于通信,3G/4G, TD-SCDMA, W-CDMA, MC-GSM, LTE数字接收机,雷达,特殊领域激光测距。

该芯片有7个电源轨,3个数字电源轨和3个模拟电源轨,还有一个高精度参考电源轨,双通道模拟差分输入,输入数据通道分为高速采样数据时钟与同步信号输入,还有 SPI控制ADC芯片配置通道;数据通道输出为16对差分信号,分别为输出随路时钟,14位数据,Status信号。

AD9684内置硬件FIR,DCO等功能,模拟通道输入阻抗可配置为400 Ohm, 200 Ohm,100 Ohm,50 Ohm。这些模式功能可以通过SPI通道对其进行配置。

由于AD9684输出是并行LVDS数据,且采用的是DDR模式,所以500M采样率工作时,LVDS数据输出的随路时钟是250Mhz,一般的芯片没有可以的达到该速率的接收器,所以必须使用FPGA来作为该芯片的数据接收与后续的信号处理。

明德扬AD9684 ADC接口工程,已经使用Xilinx kintex-7实现这个ADC的接口数据接收驱动与后续信号处理。

由于AD9684需要外部触发时钟输入,需要板卡上的外部基准时钟输入,通过FPGA内部的锁相环倍频产生一个时钟输出,以触发AD9684采样数据,对于Kintex-7器件,使用Vivado 的IP Catalog 配置一个PLL。

我们双击上图的绿 {MOD}框框,就可以进入IP核的配置界面,如下图所示:

绿 {MOD}框里面输入需要使用的IP核名字,红 {MOD}框中设置外部基准输入时钟,我们这里的板子的外部晶振输入时钟为100Mhz,所以这里输入100,输入抖动我们默认。之后点击上方的output clocks框,进入锁相环输出的配置。

按照上图对其进行配置,这样的配置表明输出是500Mhz的时钟,占空比是50%。使能型号我们选择reset 跟PLL锁定标志信号locked。由于AD9684的触发时钟输入是需要LVDS电平,所以我们在这里使能差分信号,点击OK生成IP核。

AD9684触发时钟配置完后,我们配置该芯片的接收器,由于这里AD9684是并行DDR模式的LVDS数据,所以我们需要使用的Xilinx selectIO IP核。双击下图的绿 {MOD}框可进入IP核配置界面。

按照下图参数选择,配置14位LVDS电平输入的DDR接收器:

配置完以后点击OK生成IP核,生成后我们在TOP上对其进行例化,这里我们需要自己写一个SPI逻辑去配置AD9684,生成比特流文件接着烧写进板卡后就可以进行测试了。需要注意的是,在AD9684接收的数据通道与FPGA相连接的时候出现夸BANK行为的时候,综合后布局布线会报错,这里需要对其输入数据进行约束,甚至需要将数据通道的随路时钟先引入锁相环在接到我们配置好的Select IO IP核,但是这样做会导致时序出错,需要对所有数据通道进行时序约束以保证DDR接收器的建立时间与保持时间余量。如果不做时序约束,DDR接收器所采样的数据将会出现误码。

明德扬AD9684 ADC接口工程,已经做好时序约束测试完成,AD9684的各模式也测试完毕。想要了解更多的朋友可以联系明德扬,也欢迎在评论中与我进行交流讨论!

一周热门 更多>